DDR3的布局和布线非常严格,需要按照一定的设计要求来进行,下面总结一下该设计过程和相关 的注意点:

-

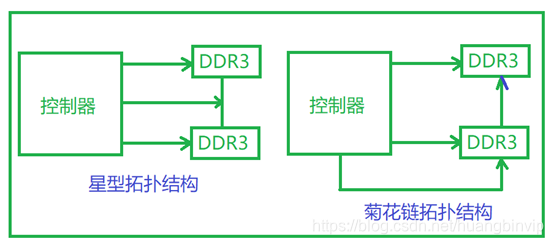

确定拓扑结构

● 数据线(DQ,LDM,UDM,LDQS,UDQS):点对点,每一片单独与控制器连接,不存在拓扑结构选择问题。

● 地址线和控制线(A0-14,BA0-2,CLK,CKE,RAS,CAS,CS,WE,RESET等):

对于拓扑结构一定要看芯片是否支持读写平衡(Read and Write Leveling),支持读写平衡情况下:

2-4片颗粒:走T点或是Fly-by都可以。

4片及以上颗粒:建议走Fly-by。

● 拓扑结构只影响地址线的走线方式,不影响数据线,一般DDR3走线选择Fly-by,不只具有最好的兼容性,也容易走线。

-

摆放器件

DDR3靠近控制器摆放,可以取得最短的走线,获得最好的性能。 -

布线顺序

● 确定好布局后,先尝试走CLK线,看看总长度是否小于4inch。

● 根据走线层和板厂叠层结构,确定走线阻抗参数:单端50欧姆,差分100欧姆

● 然后按顺序走LDQS,UDQS,DQ,A0-14,BA0-2,控制线等。

● 完成走线后,优先扇出DDR和控制器DDR区域的电源和地线,避免后面绕等长线后无法扇出电源和地线。 -

等长设置

● 以参考目标线为居中,正负偏差均可

● 对走线进行分组:DQ0-15,LDQS0,UDQS0和LDM0,UDM0为一组,DQ16-31,LDQS1,UDQS1和LDM1,UDM1为一组, A0-14,BA0-2,CLK和其余控制线为一组。

● 总的原则:CLK的长度要大于ADDR,ADDR要大于DQ

● DQ参考LDQS和UDQS(不是CLK),最大误差±50mil,LDQS和UDQS差分等长误差±5mil

● LDQS和UDQS参考CLK,最大误差±250mil,即DQS=CLK±250mil

● LDM参考LDQS,UDM参考UDQS,最大误差±50mil

● ADD[0-14]:BA0-2,RESET,WE,CS,CAS,RAS,ODT等控制线,参考CLK最大误差±100mil -

其他布线约束和设计经验

● 数据线同组同层,等长,±30mil误差,保留一个裕量。

● DQS,CLK差分走线采用紧耦合的方式走线(<2w即间距小于倍线宽),线间误差小于5mil

● 组内线间距大于3H(H为走线到主参考平面的距离),组间大于5H

● 数据线组内可以交换(不是控制器侧,是DDR侧), 数据线线序,推荐 D0、D16不要改变(每一片的第一个数据线不变),其它的数据线可以在自由调换。原因是内存的数据线只是存放数据,而CPU是根据CPU的数据线来存取,与内存的数据线顺序无关,相当于把数据存到一组容器,数据按什么顺序放就按什么顺序取。有时为了布线方便而调整组内的顺序

● 地址线不能交换。原因是模式寄存器的值是通过地址总线发出的

● 对于双向I/O信号来说,例如DQ,串行端接电阻R放置在走线的中间,用来抑制振铃,过冲和下冲

● 地址线,控制线,串行端接电阻放置在走线的发送端。

● 间距的控制要考虑阻抗要求和走线的密度。

● 相邻两层尽量参考GND

● rt电阻放最后一片DDR

● 对于DDR3,地址线的等长往往需要过孔来配合,具体的规则均绑定在过孔上和VTT端接电阻上。最优设计,CPU的地址线到达过孔的距离等长,过孔到达VTT端接电阻的距离也等长。本质是保证统一层的走线延时一致(因为同样长度的PCB走线外层和内层的传输时间不一样)

● CLK和DQS布线时不要随意换层,且与其他信号线的间距应大于该信号线相对于参考层的2.5倍,以减少串扰

● 注意数据线、地址线、时钟线等信号线的相对延迟,一般时钟线会略长于其他走线,以保证在时钟信号到来时数据信号或地址信号必须准备妥当

● 设计阻抗比要求偏小1-2欧姆,因为阻抗越大,线越细。先按小阻抗设计,后续板厂修线调整就方便。因为减小线宽,就可以加大阻抗,同时增加了间距,这样阻抗和性能两个方面都比较好照顾。

● VTT开始上电必须在VDDQ之后(具体实现方式可以采用VDDQ来控制VTT电源芯片的使能),避免器件latch-up,推荐VTT和VREF同时上电

● 传输线的速度按照6mil/ps来计算(167ps/inch,6.57ps/mm)

● 走完地址线和数据线后,务必将DDR芯片的电源脚,接地脚,去耦电容的电源脚,接地脚全部走完,否则在后面绕等长时会很麻烦。

● DDR数据线用DQS来锁存,因此要和DQS保持等长。地址、控制线用时钟来锁存,因此要和时钟保持等长,一般等长就没有什么问题。

● 串扰方面,只要拉开线距,一层信号一层地,就不会出问题

● 一般来说,DQ,DQS,DM和时钟信号线选择VSS作为参考平面,因为VSS比较稳定,不易受到干扰

● 高速信号换层处需要加回流过孔,这里其实就是增加了垂直方向的回流路径,这个对于高速信号是非常有必要的

作者:huangbinvip

来源:CSDN

原文:https://blog.csdn.net/huangbinvip/article/details/105473768

版权声明:本文为作者原创文章,转载请附上博文链接!

内容解析By:

CSDN,CNBLOG博客文章一键转载插件