前言

系统时钟和配置时钟必须要学会并且了然于胸。

而STM32f03时钟这部分。是难点。

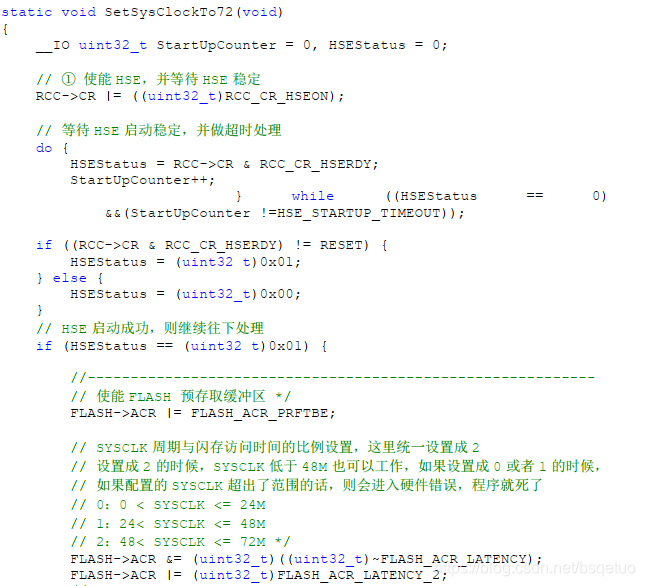

时钟树单纯讲理论的话会比较枯燥,如果选取一条主线,并辅以代码,先主后次讲解的话 会很容易 ,而且记忆还 更深刻。 我们这里选取库函数时钟系统时钟函数:

SetSysClockTo72(); 以这个函数的编写流程来讲解时钟树

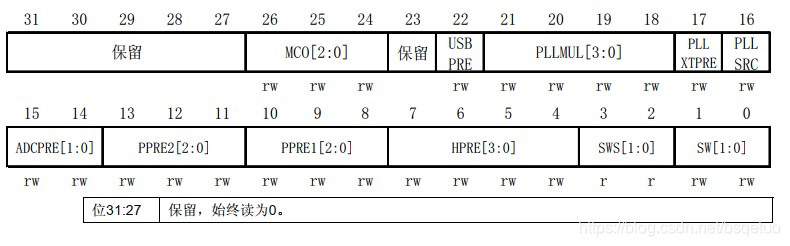

下面是STM32时钟树。

1.CRC相关寄存器

要了解并配置时钟树,首先需要认识有关寄存器

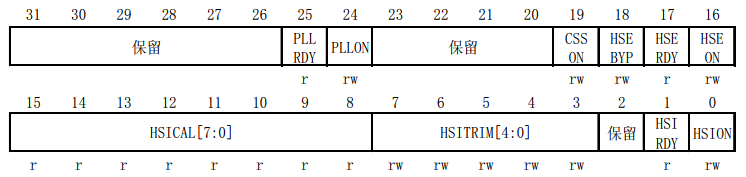

1.1 时钟控制寄存器(RCC_CR)

偏移地址: 0x00

复位值: 0x000 XX83, X代表未定义

访问: 无等待状态, 字, 半字 和字节访问

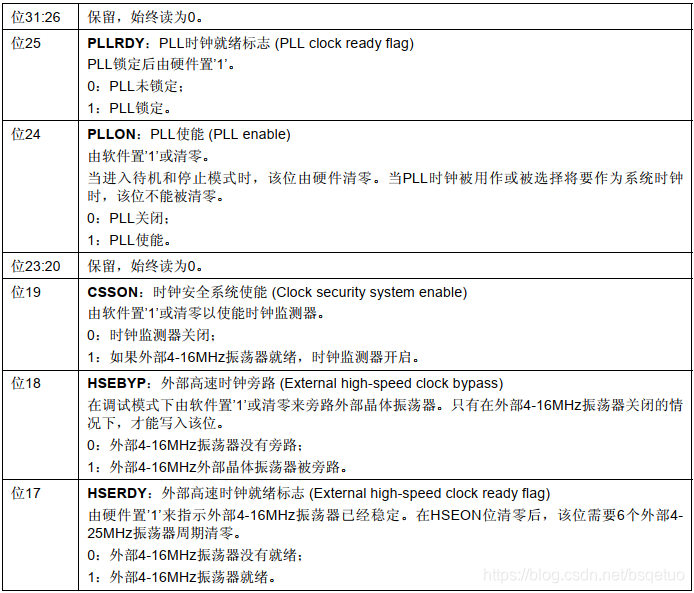

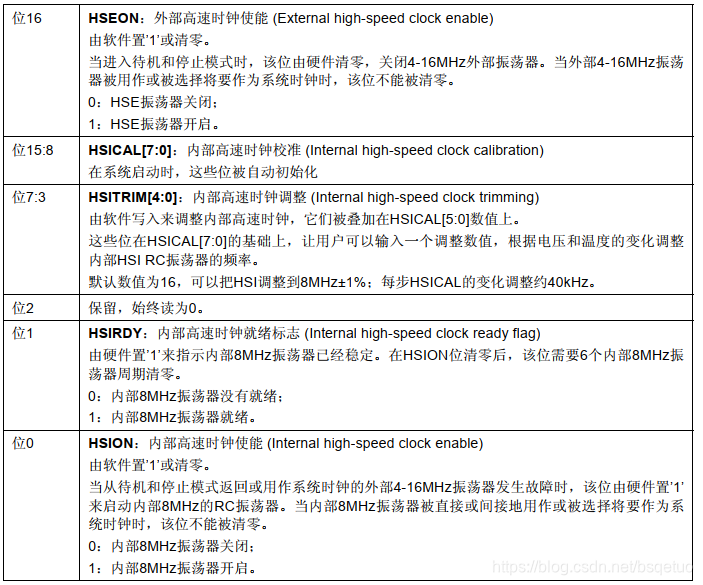

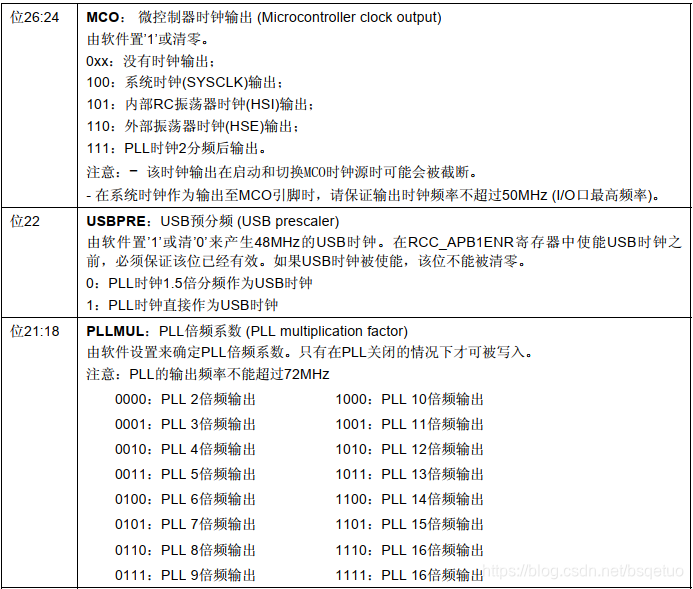

1.1 时钟配置寄存器(RCC_CFGR)

偏移地址: 0x04

复位值: 0x0000 0000

访问: 0到2个等待周期,字,半字和字节访问

只有当访问发生在时钟切换时,才会插入1或2个等待周期。

2.系统时钟讲解

对应于图中黄色部分

2.1 HSE:高速外部时钟

无源晶振(4-16M),通常使用8M,对应于

RCC_CR寄存器中位16(控制)和位17(就绪标志)

PLLXTPRE,确定 PLL 时钟来源的时候, HSE 可以不分频或者 2 分频,这个由时钟配置寄存器

CFGR 的位 17

来控制

2.2 PLL 时钟源

PLLSRC,PLL 时钟来源可以有两个,一个来自 HSE,另外一个是 HSI/2,具体用哪个由时钟配置寄存器

CFGR 的位 16: PLLSRC 设置。

HSI 是内部高速的时钟信号,频率为 8M,根据

温度和环境的情况频率会有漂移,一般不作为 PLL 的时钟来源。这里我们选 HSE 作为PLL 的时钟来源。

2.3 PLL 时钟 PLLCLK

PLLMUC为PLL倍频系数,设置成多少, 由时钟配置寄存器

CFGR 的位21-18

: PLLMUL[3:0]设置。我们这里设置为 9 倍频。

注意:PLL时钟源头使用HIS/2的时候,PLLMUL最大只能为16,这个时候PLLCLK最大只能是64M,小于ST官方推荐的最大时钟72M。

2.4 系统时钟 SYSCLK

系统时钟来源可以是: HSI、 PLLCLK、 HSE,具体的时钟配置寄存器

CFGR 的位 1-0

:SW[1:0]设置。我们这里设置系统时钟: SYSCLK = PLLCLK = 72M。

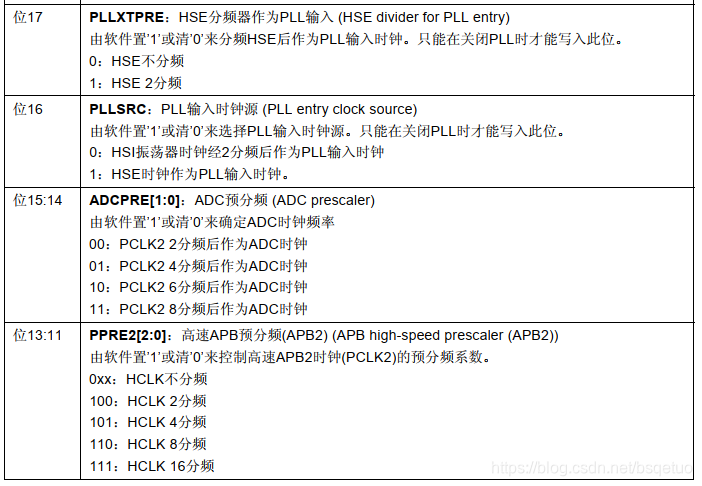

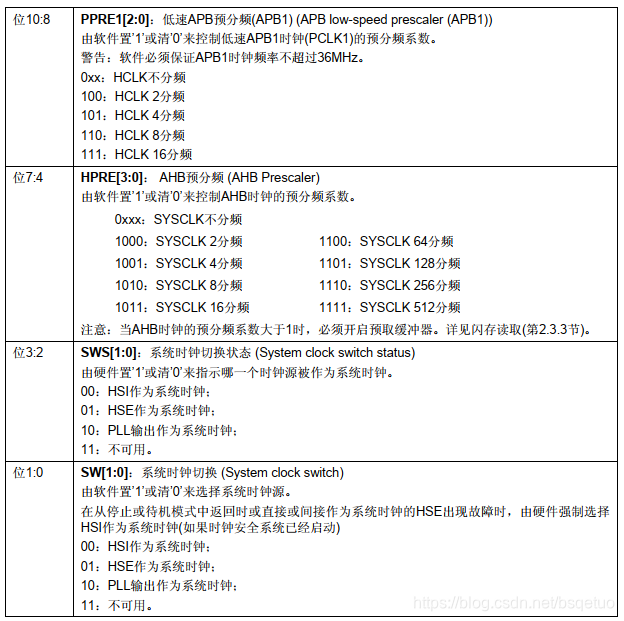

2.5 AHB 总线时钟 HCLK

由时钟配置寄存器

CFGR的位 7-4

: HPRE[3:0]设置。

我们这里设置为 1 分频,即 HCLK=SYSCLK=72M。

2.6 APB2 总线时钟 HCLK2

由时钟配置寄存器

CFGR 的位 13-11

: PPRE2[2:0]决定。

们这里设置为 1 分频,即 PCLK2= HCLK = 72M。

2.7 APB1 总线时钟 HCLK1

由时钟配置寄存器

CFGR 的位 10-8

:PRRE1[2:0]决定。

最高为36M。

3.时钟树其他部分讲解

通过对系统时钟设置的讲解,整个时钟树我们已经把握的有六七成,剩下的时钟部分我们讲解几个重要的。

对应图中字母部分

3.1 A、 USB 时钟

USB 时钟是由 PLLCLK 经过 USB 预分频器得到,分频因子可以是: [1,1.5], 具体的由时钟配置寄存器

CFGR 的位 22: USBPRE 配置

。 USB 的时钟最高是 48M,根据分频因子

反推过来算 , PLLCLK 只能是 48M 或者是 72M。一般我们设置 PLLCLK=72M,USBCLK=48M。 USB 对时钟要求比较高,所以 PLLCLK 只能是由 HSE 倍频得到,不能使用 HSI 倍频

3.2 B、 Cortex 系统时钟

Cortex 系统时钟由 HCLK 8 分频得到,等于 9M, Cortex 系统时钟用来驱动内核的系统定时器 SysTick, SysTick 一般用于操作系统的时钟节拍,也可以用做普通的定时。

3.3 C、 ADC 时钟

ADC 时钟由 PCLK2 经过 ADC 预分频器得到,分频因子可以是[2,4,6,8],具体的由时钟配置寄存器

CFGR 的位 15-14

: ADCPRE[1:0]决定。 很奇怪的是怎么没有 1 分频。 ADC

时钟最高只能是 14M,如果采样周期设置成最短的 1.5 个周期的话, ADC 的转换时间可以达到最短的 1us。如果真要达到最短的转换时间 1us 的话,那 ADC 的时钟就得是 14M,反推 PCLK2 的时钟只能是: 28M、 56M、 84M、 112M,鉴于 PCLK2 最高是 72M,所以只能取 28M 和 56M。

3.4 D、 RTC 时钟、独立看门狗时钟

RTC 时钟可由 HSE/128 分频得到,也可由低速外部时钟信号 LSE 提供,频率为32.768KHZ,也可由低速内部时钟信号 HSI 提供,具体选用哪个时钟由备份域控制寄存器

BDCR 的位 9-8

: RTCSEL[1:0]配置。 独立看门狗的时钟由 LSI 提供,且只能是由 LSI 提供,LSI 是低速的内部时钟信号,频率为 30~60KHZ 直接不等,一般取 40KHZ。

3.5 E、 MCO 时钟输出

MCO 是 microcontroller clock output 的缩写,是微控制器时钟输出引脚,在 STM32 F1系列中 由 PA8 复用所得,主要作用是可以对外提供时钟,相当于一个有源晶振。 MCO 的时钟来源可以是: PLLCLK/2、 HSI、 HSE、 SYSCLK,具体选哪个由时钟配置寄存器

CFGR 的位 26-24

: MCO[2:0]决定。 除了对外提供时钟这个作用之外, 我们还可以通过示波器监控 MCO 引脚的时钟输出来验证我们的系统时钟配置是否正确。

3.6 F、 HSI高速的内部时钟。

来源:芯片内部,大小为8M,当HSE故障时,系统时钟会自动切换到HSI,直到HSE启动成功。

控制: RCC_CR 时钟控制寄存器的位0:HSION控制

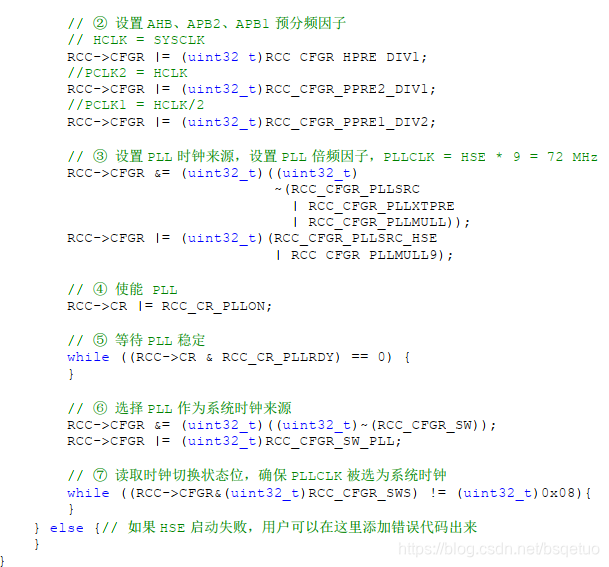

4.设置系统时钟库函数

设置系统时钟库函数如下,该函数是直接操作寄存器的,有关寄存器部分请参考数据手册的 RCC 的寄存器描述部分。

后记

时钟树这块配置还是很重要的,一定要掌握。