今天我们一起来学习一下MIPI DSI协议;

1:Overview

DSI 全称Display Serial Interface,是由MIPI联盟定义的处理器与外设之间的移动设备接口规范,该规范建立在现有的标准的基础上,并采用了MIPI联盟DBI,DPI,DCS标准中定义的像素格式和命令集,DSI是主要用于显示传输的接口。

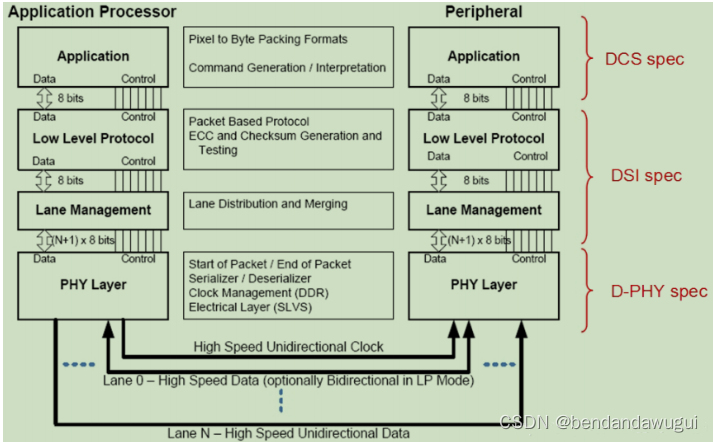

一般而言,完整的的DSI传输如下图所示,从上到下依次为(本文主要关注第二层与第三层)

1:Application:描述了数据流中包含的数据的更高层的编码和解释,根据显示子系统架构,他可能由具有规定格式的像素组成,或者由显示模块的命令组成,可以参考DSC/DPI/DBI spec;

2:Low Level Protocal:该协议规定了通过接口的位和字节的顺序和值,它定义如何将字节组织成定义的组,即数据包,该协议以数据包为最小集合,并为每隔数据包定义了所需要的包头,以及如何生成和解释包头信息,后续发送端将包头和错误检查信息附加到正在传输的数据中;

3:Lane Managment:通道管理,DSI可进行通道扩展以提高性能,根据应用的带宽要求,Data Lane的数量可以是1,2,3,4;

4:PHY Layer:物理层

操作模式:

DPHY有三种操作模式: Escape mode, High-Speed(Burst) mode,及 Control mode。

• MIPI的HS模式(0.2V),传送图像数据,速度为80Mbps ~ 1000Mbps;

• MIPI的LP模式(1.2V),可以用于传送控制命令,最高速度为10Mbps;

• MIPI规定,任一个MIPI设备必须具有Escape Mode,此为LP模式(低功耗模式)中的一种,此模式下可低速传输图像或其他数据。

2.1 从控制模式的停止状态开始的可能事件有:

• Escape mode request (LP-11→LP-10→LP-00→LP-01→LP-00)

• High-Speed mode request (LP-11→LP-01→LP-00)

• Turnaround request (LP-11→LP-10→LP-00→LP-10→LP-00)

2.2 Escape mode是数据Lane在LP状态下的一种特殊操作

• 在这种模式下,可以进入一些额外的功能:LPDT, ULPS, Trigger

• 数据Lane进入Escape mode模式通过LP-11→LP-10→LP-00→LP-01→LP-00

• 一旦进入Escape mode模式,发送端必须发送1个8-bit的命令来响应请求的动作,0x87(LPDT),0x78(ULPS), 0x45(Trigger)。

• Escape mode 使用Spaced-One-Hot Encoding

2.3 超低功耗状态(ULPS, Ultra-Low Power State)

•这个状态下,lines处于空状态 (LP-00)

• 时钟Lane的超低功耗状态

•时钟Lane通过LP-11→LP-10→LP-00进入ULPS状态

•通过LP-10 → TWAKEUP →LP-11退出这种状态,最小TWAKEUP时间为1ms

2.4 高速数据传输 (High-Speed(Burst) mode)

•发送高速串行数据的行为称为高速数据传输或触发(burst)

•全部Lanes门同步开始,结束的时间可能不同。

•时钟应该处于高速模式

2. 5 各模操作式下的传输过程

•进入Escape模式的过程 :LP-11→LP-10→LP-00→LP-01→LP-00→Entry Code → LPD (10MHz)

•退出Escape模式的过程:LP-10→LP-11

•进入高速模式的过程:LP-11→LP-01→LP-00→SoT(00011101) → HSD (80Mbps ~ 1Gbps)

•退出高速模式的过程:EoT→LP-11

•控制模式 - BTA 传输过程:LP-11→LP-10→LP-00→LP-10→LP-00

•控制模式 - BTA 接收过程:LP-00→LP-10→LP-11

PS:(1)BTA(Bus turn around):总线控制权可在主机端与从机端之间交换,发送端发送放弃总线请求,接收端接收请求之后

控制总线发起应答,总的过程为BTA(turn around)操作。(2)Escape mode 和 High-Speed(Burst)

mode之间的状态转换,必须经过stop state状态,不可直接转换。(3)每个字节都是低位先传,多字节元素(16位计数值、 16位CRC)也是低字节低位先传。

2:DSI Mode

DSI 定义了

两种

基本操作模式,

Video模式

和

Command模

式,使用那种模式取决于外设的架构,功能与应用的目标。

2.1 Video模式

Video模式是指

从主机

处理器

到外围

设备的传输采用

实时像素流形式

的操作,一般而言,显示模块依靠主机处理器以足够的带宽提供图像数据,以避免显示图像中的闪烁或其他可见伪影,而一些视频模式架构可能包括一个

简单的时序控制器

和

部分帧缓冲区

,用于在待机或者低功耗下保持部分屏幕或较低分辨率的图像,这允许关闭接口以降低功耗,当然为了降低复杂性和成本,仅在Video模式下运行的系统是单向的Data Lane。

# 视频信息只能使用高速模式传输

2.2 Command 模式

Command模式是指其中事务主要采取将

命令

和

数据

发送到外设(例如显示模块)的形式的操作,显示控制器需要有

本地寄存器

和

帧缓冲器

,处理器通过

向显示控制器发送命令

,

参数

和

数据

来间接

控制其显示行为

,同时还可以

读取

显示模块

状态信息

或

帧存储器的内容

,故command模式操作需要一个双向的Data Lane。

# 某些显示器仅能在LP模式下初始化

3:DSI Physical Layer

本节简要概述DSI中使用的物理层,有关详细信息可以参考D-PHY——

MIPI 系列之 D-PHY_爱洋葱的博客-CSDN博客

DSI使用一个或者多个串行数据信号和一个串行时钟在主机处理器和外围设备之间传输信息,通过总线发送高速串行数据的动作称为

HS传输或者Burst

,在高速传输之间,差分数据信号或者通道进入低功耗状态(LPS),且接口在不主动发送或者接收高速数据时也应该处于低功耗状态LPS。

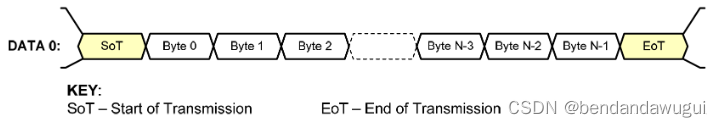

下图为HS模式下的数据传输:

协议规定了

一个字节

即最小数据单元,一次传输包含N个字节。

3.1:数据流控

由前面的结构可知,底层为协议层将数据发给PHY层,但是协议层和PHY层之间

没有握手

,一旦传输开始,协议层就可以限制进出PHY层的数据传输,而数据包一共完整无间断的发送和接收,则需要链路两端的协议层和数据缓冲应始终具有等于或者大于PHY层电路的带宽,一个实际的结果是系统实现者应该确保接收器的带宽能力等于或者大于发射器的带宽能力。

3.2 双向性

DSI实现的物理层由一到四个数据通道和一个时钟通道组成,其中:

Command Mode:

data lane0应该是双向的

;额外的Data lane应是单向的。

Video Mode:

Data

Lane0可以是双向的或单向的

;额外的Data Lane应是单向的。

Note:Clock lane应该由Master驱动,而不能由外设驱动;

LP传输应仅使用Data Lane0;

PHY和协议层之间的接口

有几个控制总线方向的信号

,当master需要外设的响应时使用,例如

返回READ数据或状态信息

,它有如下

流程

:

1:Master在传输的最后一个数据包期间向其PHY断言

TurnRequest

;

2:PHY层拿到TurnRequest后在

Eot序列之后发送BTA(bus turn around)

命令;

3:当外设接收到BTA命令时,其PHY层将TurnRequest置为协议层的输入;

4:外设拿到TurnRequest通知其接收协议层准备向master发送响应;

5:外设发送响应后,外设同样使用TurnRequest将总线控制权交换给Master;

BTA机制时需要在LP下实现的

下图为测试过程中抓的一个BTA波形:

3.3 Video Mode Interface

在 Video 模式下运行的 DSI TX 的最低 PHY 要求是:

• Data Lane Module:CIL-MUNN(HS-TX、LP-TX)

• Clock Lane Module:CIL-MCNN(HS-TX、LP-TX)

在 Video 模式下运行的 DSI RX 的最低 PHY 要求是:

• Data Lane Module: CIL-SUNN (HS-RX, LP-RX)

• Clock Lane Module: CIL-SCNN (HS-RX, LP-RX)

3.4 Command Mode Interface

在 Command 模式下运行的 DSI TX 的最低 PHY 要求是:

• Data Lane Module: CIL-MUYY (HS-TX, LP-TX, LP-RX, and LP-CD)

•Clock Lane Module: CIL-MCNN (HS-TX, LP-TX)

在 Command 模式下运行的 DSI RX 的最低PHY要求是:

• Data Lane Module: CIL-SUYY (HS-RX, LP-RX, LP-TX, and LP-CD)

•Clock Lane Module: CIL-SCNN (HS-RX, LP-RX)

3.5 Clock

DSI时钟是

从Master到Slave

的信号,它可能具有多种功能:

1:Bit Clock:在整个链路上,DSI时钟用作源同步时钟,用于捕获接收器PHY中的串行数据位;

2:Byte Clock:分频后,DSI时钟用于在协议层和应用层之间的概念接口生成Lane Byte Clock

3:Esc Clock:分频后,DSI时钟用于LP模式;

4:Application Clock:DSI位时钟的分频版本可用于其他时钟功能;

所有DSI TX/RX都

应支持时钟通道上的连续时钟行为

,并且可以选择

支持非连续时钟

行为(可降低功耗)

Note:

在低功耗信号模式下,LP 时钟在功能上嵌入在数据信号中。当 LP 数据传输结束时,时钟有效停止,后续的 LP 时钟对外设不可用。如果外设需要额外的时钟来推进其逻辑状态,通过顺序缓冲区移动数据,或类似的,可能需要在 LP 传输中添加“虚拟”数据字节以实现状态机的前向进程或推进数据通过时序逻辑。

BTA 的握手过程只允许 Master 和 Slave 之间的 Escape Mode 时钟频率存在有限的不匹配。 Master 和 Slave 之间的 Escape Mode 频率比不得超过 3:2。Master 负责控制自己的时钟频率以匹配外设。Master 的 LP 时钟频率应在外围 LP 时钟频率的 67% 到 150% 范围内。因此,外设实现者应指定外设的标称 LP 时钟频率和保证的精度。

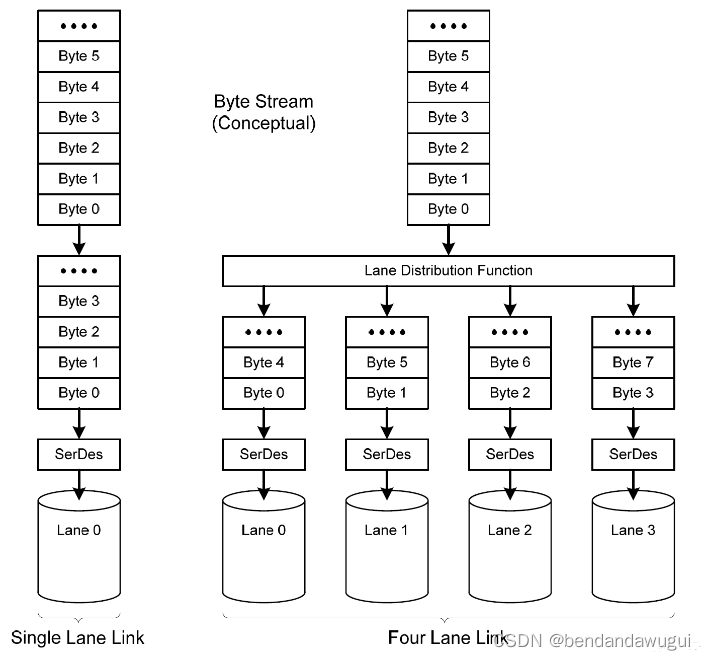

4:多通道管理

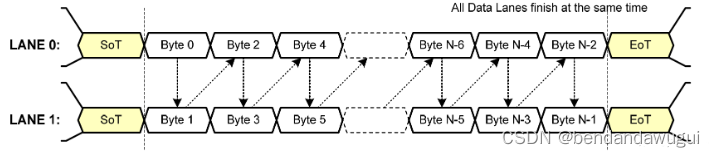

在PHY层之上有一个通道管理层,在发送端,负责数据分发到每条lane,而在接收端,负责将多个lane的数据合并,如下图中所示,即发送端分别在单lane与4lane的情况下数据的lane上分布。

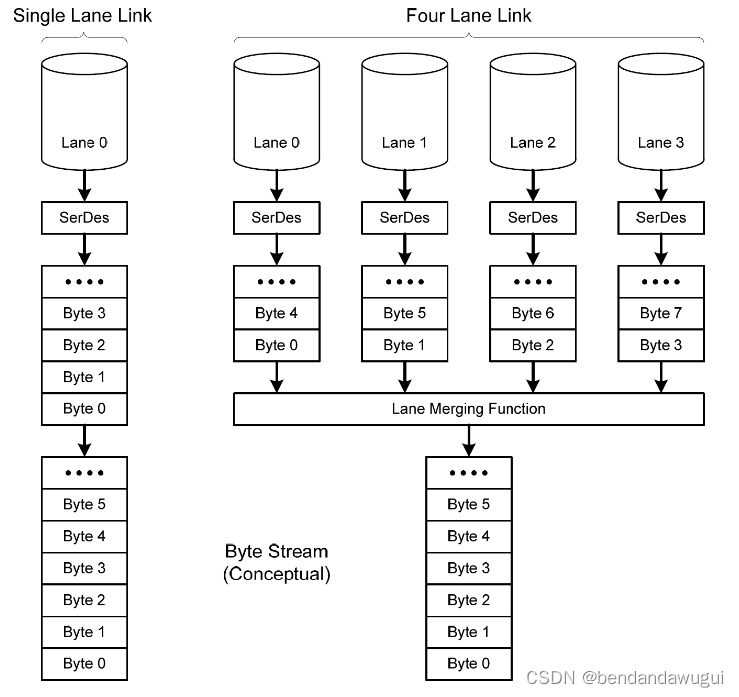

接收端就正好相反,如下图所示,即发送端分别在单Lane与4Lane的情况下数据的Lane上分布;

4.1:通道数匹配

当Slave通道数与Master不匹配时,可以通过调整D-PHY的通道数来匹配对方。如下图所示:当Receiver PHY只有两条Data Lane,而Transmitter PHY有四条Data Lane。这是可以调整Transmitter PHY输出使用两条Data Lane,同理也可以将两边都调整为使用一条lane。而在这种情况下并不影响DSI与D-PHY之间的连接。

4.2 线上数据分布

我们知道DSI的数据是以

Byte为最小单位

的,使用的Data Lane的条数是可以调整。而一次传输包含了

SOT、Data、EOT

等。排布规则也比较简单:每条Lane都有自己的SOT与EOT,数据在SoT之后从Lane0~Lane3依次排布。

那么在线上则存在不同情况:

1:数据为lane数的整数倍:

2:数据为非lane数的整数倍

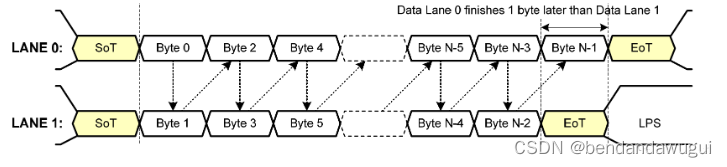

5:DSI协议

在 DSI 链路的发送端,并行数据、信号事件和命令会在协议层中转换为数据包。协议层附加数据包协议信息和包头,然后通过Lane管理层将所有字节发送到 PHY。 数据包由 PHY 序列化并通过串行链路发送。 DSI 链路的

接收端执行与发送端相反的操作

,将数据包分解为并行数据、信号事件和命令。

Note:数据包协议和格式与使用的通道数无关

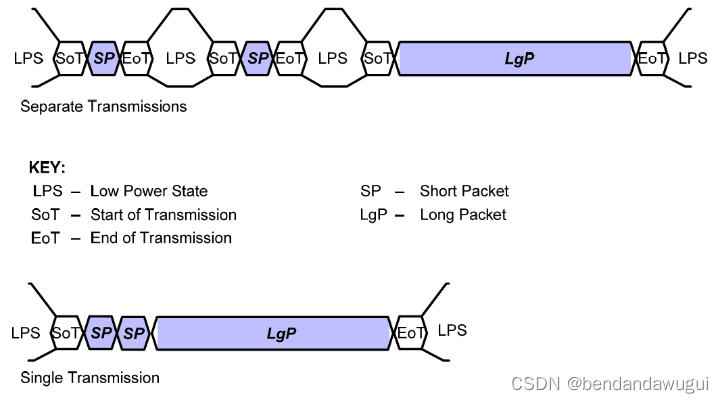

DSI支持一次传输一个包或者多个包,每次传输包含一个SOT代表开始,一个EoT代表结束。要传 3 个包,那么如下所示两种方式:

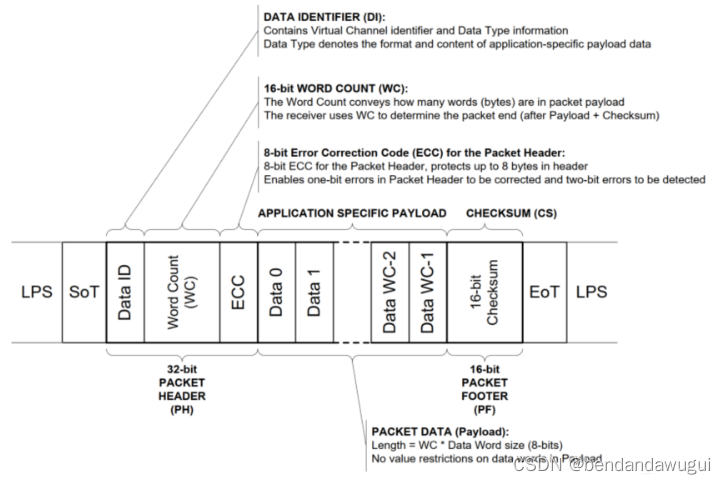

5.1包格式

DSI定义了两种数据包结构:

长包

和

短包

,对于这两种数据包结构,数据标识符始终是数据包的第一个字节。

5.1.1短包

一个短数据包包含一个

8 位数据 ID

,后跟

2 个字节数据

和一个

8 位 ECC

。 短数据包的长度为 4 个字节。主要用于传输

命令

、

参数

、

读写寄存器

,也可以传输一些

时序信息

,比如

Hsync

、

Vsync

等。

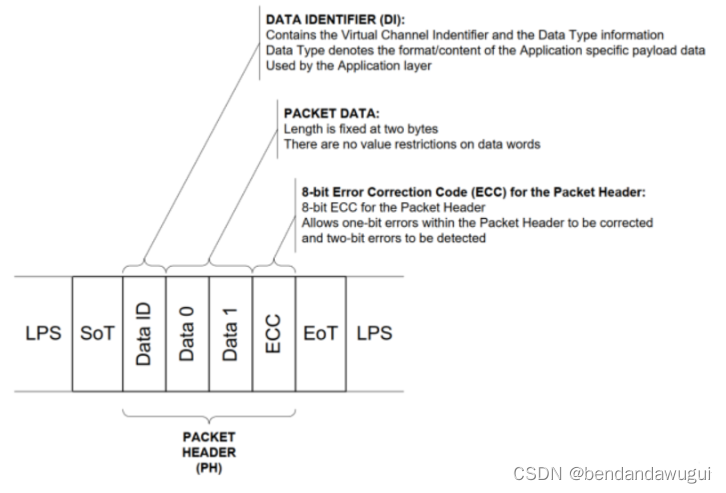

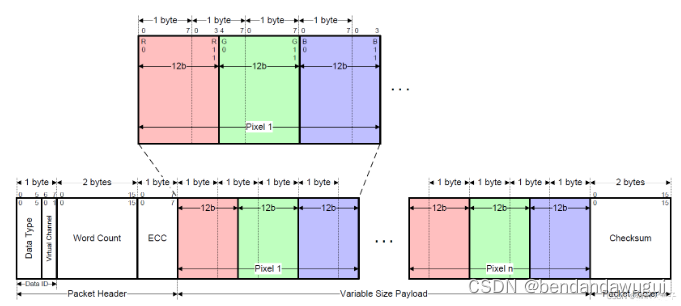

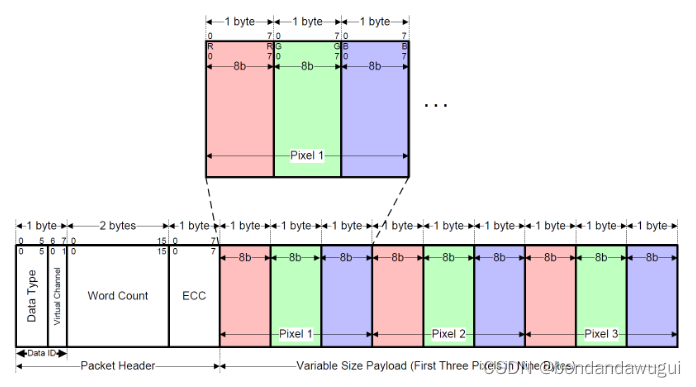

5.1.2 长包

长数据包应由三个元素组成:

32 位数据包头(PH)

、具有

可变字节数

(0-65535)的特定应用数据有效负载和

16 位数据包尾(PF)

。 包头进一步由三个元素组成:8 位数据标识符、16 位字数和 8 位 ECC。 包尾有一个元素,

一个 16 位校验和

。 长数据包的长度可以是 6 到 65,541 个字节。主要用于传输图像、视频等数据。

Word Count 仅指数据的长度,以Byte为单位,而不包含后续的Checksum。

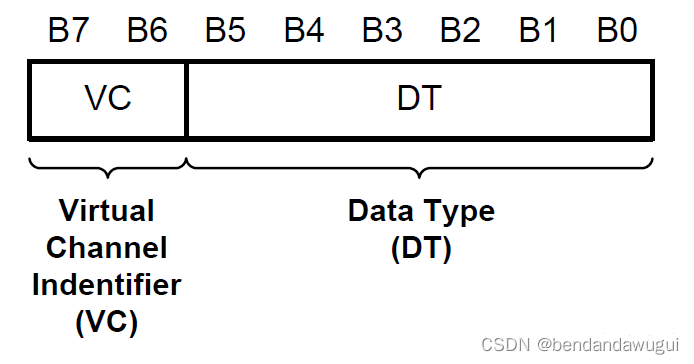

5.2 Data ID

任何数据包的第一个字节是 DI(数据标识符)字节。 下图即数据标识符 (DI) 字节的组成。 DI[7:6]:这两位将数据标识为定向到四个虚拟通道之一。 DI[5:0]:这六个位指定数据类型。

5.3 ECC

ECC可以纠正单比特错误并在数据包报头中检测 2 比特错误;

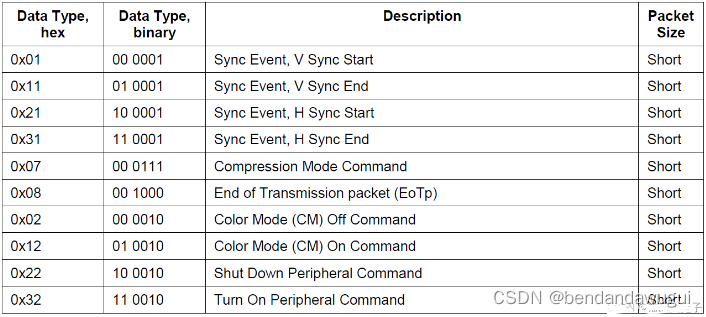

5.4 Data Type(Processor(主机) -> Peripheral(外设))

DSI的传输都是基于包传输的(分短包与长包),而每个包的第一个Byte一定是Data ID。由前面我们可知,

Data ID由Virtual ID 与 Data Type组成

。Virtual ID很好理解,代表当前虚拟通道号。Data Type 即知名我们传输的包是干什么的,这样对端接收到包,第一时间解析除Data Type,它就知道怎么准备接收了。

5.4.1 Sync Event (H Start,H End,V Start,V End)Data Type = XX 0001

Data Type = 00 0001 (0x01)V sync start

Data Type = 01 0001 (0x11)V sync end

Data Type = 10 0001 (0x21)H sync Start

Data Type = 11 0001 (0x31)H sync end

一般来讲,

Sync Event 应该是成对出现

的,即,出现 Sync Start 必定后面跟着 Sync End

事实上,一个表达式sync event 的packet包含的信息不止有data type,前面说了它是一个短包,那么作为一个短包,即:

DI+DATA0+DATA1+ECC

,在解析DI之后,如果

DATA0的值为0x00

,那么

DATA0和DATA1都会被直接无视

,如果DATA0的值不为0x00,那么对端就要去解析DATA1的内容。

可以看出来,DSI在sync event的时候Data0和Data1中包含的是和

3D显示相关

的东西和配置;

5.4.2 Eot packet ,data type = 00 1000 (0x08)

Eotp用于在链路层指示一个High Speed传输结束;引入它的目的主要是增强DSI系统在高速传输时候的可靠性,早期的DSI协议并不支持这个,所以为了兼容旧的DSI协议,这个Eotp是一个可配置的,Eotp的主要目的是在HS传输模式下

增强系统整体的鲁棒性

,在LP模式时,不应该出现Eotp

一个支持Eotp的包,应该是下面这个样子:

- Data Type = DI [5:0] = 0b001000

- Virtual Channel = DI [7:6] = 0b00

- Payload Data [15:0] = 0x0F0F

- ECC [7:0] = 0x01

对于

多通道的传输

,Eotp字节

分布在多个通道中

5.4.3 Color Mode Cmd,Data Type = 00_0010(0x02)01_0010(0x12)

Color Mode Off (0x02)是短数据包命令,它将Video模式显示模块

从low-color模式返回到正常显示

;

Color Mode On (0x12)是短数据包命令,它将Video模式显示模块

从正常显示操作切到low-color模式

;

5.4.4 Peripheral On/Off Cmd,Data Type = 10_0010(0x22),11_0010(0x32)

Shutdown Peripheral(0x22)是短数据包命令,

关闭视频模式

显示模块中的显示以节省电力。但接口应保持通电以便接收开启命令。

Turn On Peripheral (0x32) 是短数据包命令,

打开视频模式

显示模块中的显示以进行正常显示操作。

5.4.5 Deneric Write/Read Packet

Generic WRITE

有 4 种类型,

3种Short Write Packet

与

1种 Long Write Packet

,他们的目的是用于

向显示设备发送通用数据

,支持

0-2个parameters

;

Data Types = 00 0011 (0x03):Short Write with 0 个 parameter;

Data Types = 01 0011 (0x13):Short Write with 1 个 parameter;

Data Types = 10 0011 (0x23):Short Write with 2 个 parameters;

Data Types = 10 1001 (0x29):Long Write

Generic READ Request

有 3 种 Read Packet,它们的主要目的是

读取显示设备的寄存器

与

状态交互

。

Data Types = 00 0100 (0x04):Read with 0 个 parameter;

Data Types = 01 0100 (0x14):Read with 1 个 parameter;

Data Types = 10 0100 (0x24):Read with 2 个 parameters

Generic READ Request 也是一个

Short Packet

,是

向外设请求数据

,也就是读数据;和上面一样,这种 Generic READ 是由 system designer 确认的 host processor 和外设共同有的并都支持的东西;这个需要关注显示设备的 Datasheet;

返回的数据,可能是 Short 也可能是 Long;

完整的 Generic READ Request 包,和 WRITE 一样:

当不传送 parameter 的时候,Data 0 和 Data 1 的内容设置为 0x00;

当传输 1 个字节的 parameter 的时候,Data 0 就是这个 parameter,Data 1 需要被设置为 0x00;当传输 2 个字节的时候,直接往 Data 0 和 Data 1 里面写;

READ Request 命令完成后,主机应该发送 BTA

5.4.6 DCS命令 packet

DCS 是用于

命令模式显示模块的标准化命令集合

,在 MIPI 的 DCS 文档中专门进行描述;

针对的是 Command Mode 的显示设备

;

对于 DCS 命令,

DI字节之后的第一个字节是 DCS 命令字节

, 如果 DCS 命令不需要参数,则第二个有效载荷字节应为 0x00。

DCS命令

共有 3 种

:

5.4.6.1 DCS Short Write Command, Data Types = 00 0101 (0x05), 010101 (0x15)

Data Types = 00 0101 (0x05):Write whit 0 个 parameter;

Data Types = 01 0101 (0x15):Write whit 1 个 parameter;

从名字就看得出来,这是 DCS Short 写的;如果没有 parameter 需要写的话,Data 1 填充 0x00;(Data 0 放置的是

DCS Command Byte

);

值得注意的是,如果 DCS Short Write Command 后面跟了一个 BTA 的话,正常情况下,外设需要返回 ACK Trigger Message;除非在主机到外设的传输过程中遇到了 Error,如果遇到 Error,那么外设需要回复 Acknowledge and Error Report 给主机;

5.4.6.2

DCS Read Request, No Parameters, Data Type = 00 0110 (0x06)

Data Types = 00 0110 (0x06):DCS Read Request

DCS 也支持 Read Request,用于通过 DCS 定义的方式读取数据,这是一个 Short Packet;完整的包组成为:

DI + DCS Read command + 0x00 + ECC

所以这个 DCS Read command 定义了很多内容,需要参考 MIPI DCS 文档,你懂的;

因为是 Read,所以需要在发送完这次传输后,再在双向通道发送 BTA;

外设返回的数据,

可能是 Short Packet 也可能是 Long Packet;

READ 部分的其他限制,参考 Generic READ Request;

5.4.6.3 DCS Long Write / write_LUT Command, Data Type = 11 1001 (0x39)

Data Types = 11 1001 (0x39):Long Write;

DCS 也支持 Long Packet 的 Write,用于向外设发送大量的数据,具体的需要参考 MIPI DCS 的文档;

5.4.7 Set Maximum Return Packet Size ,Data type = 11_0111 (0x37)

Set Maximum Return Packet Size 是一个 Short Packet,用于指定

外设返回给主机

的 Long Packet 最多

包含多少 payload

,主要是

怕主机的 buffer 爆掉

,值得注意的是,当主机和外设 Power-on 或者 Reset 之后,在两者通信之前,这个

值最好是先被设置好.

5.4.8 Null packet(Long packet)Data type = 00_1001 (0x09)

Null Packet 是一种在

发送虚拟数据时将串行数据通道保持在高速模式的机制

。 这是一个长数据包。 与所有数据包一样,其内容应为整数字节。Null 数据包由

DI 字节、两字节 WC、ECC 字节

和

WC 字节的“空”有效载荷组成

,以

两字节校验和结束

。 发送的实际数据值无关紧要,因为外围设备不捕获或存储数据。 但是,应生成 ECC 和校验和并将其传输到外设。

5.4.9 Blanking Packet (long packet),Data Type = 01 1001(0x19)

消隐数据包用于在长数据包中传送消隐时间信息。 通常,数据包代表Video模式显示器的有效扫描线之间的周期,其中传统的显示时序是从主机提供给显示模块的。 消隐期可能具有散布在消隐段之间的同步事件包。 与所有数据包一样,消隐数据包内容应为整数字节。

消隐数据包可能包含任意数据作为有效载荷

。

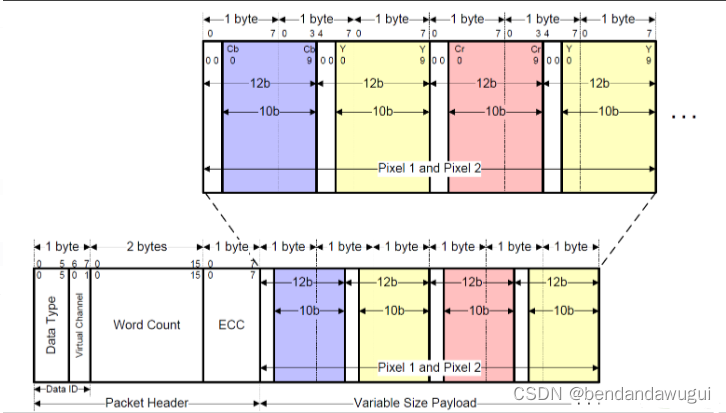

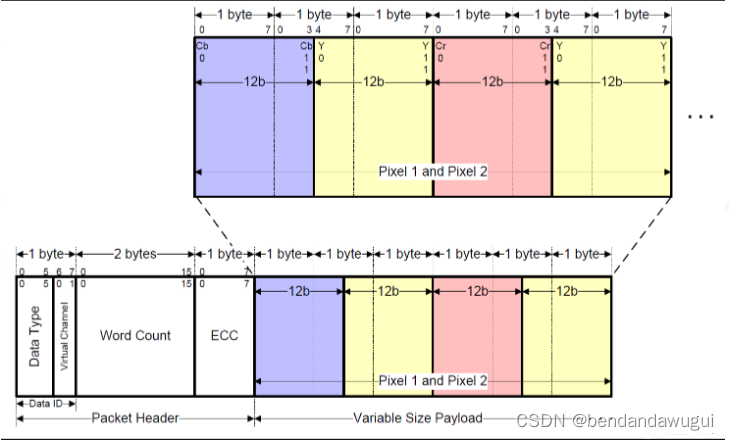

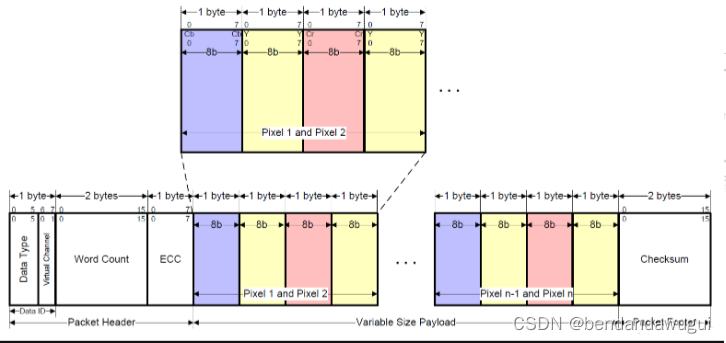

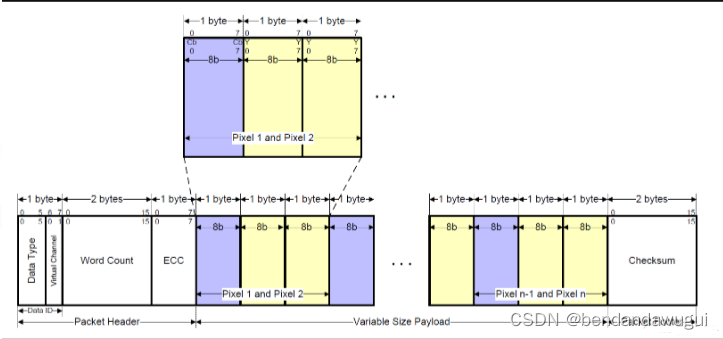

5.4.10 YCbCr Packed Pixel Stream

YCbCr 格式的像素流主要有以下四种格式:

1. Loosely Packed Pixel Stream, 20-bit YCbCr 4:2:2 Format, Data Type = 00 1100 (0x0C)

2. Packed Pixel Stream, 24-bit YCbCr 4:2:2 Format, Data Type = 01 1100 (0x1C)

3. Packed Pixel Stream, 16-bit YCbCr 4:2:2 Format, Data Type = 10 1100 (0x2C)

4. Packed Pixel Stream, 12-bit YCbCr 4:2:0 Format, Data Type = 11 1101 (0x3D)

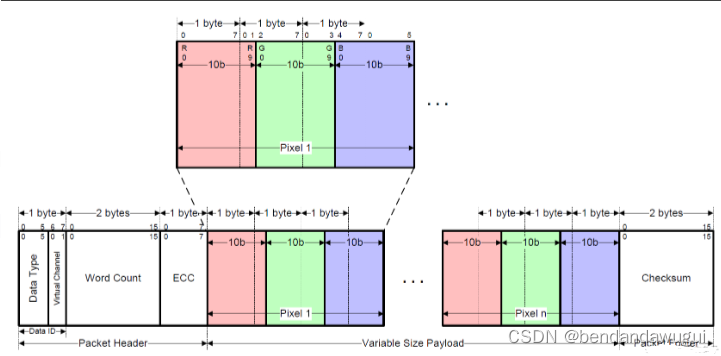

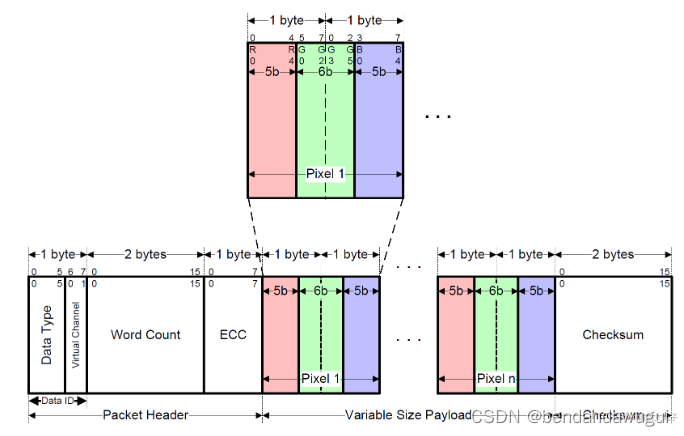

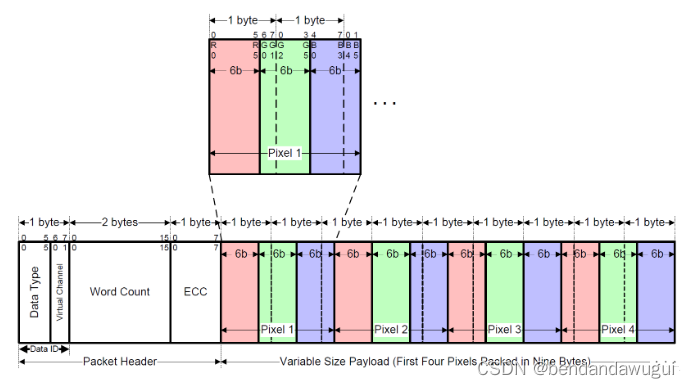

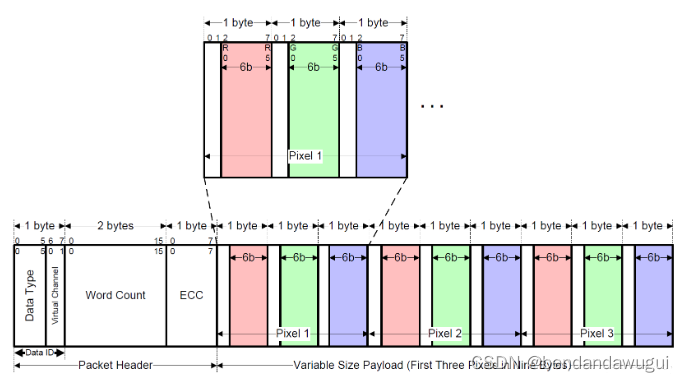

5.4.11 RGB Packed Pixel Stream

RGB 格式的像素流主要有以下六种格式:

1. Packed Pixel Stream, 30-bit Format, Long Packet, Data Type = 00 1101 (0x0D)

2. Packed Pixel Stream, 36-bit Format, Long Packet, Data Type = 01 1101 (0x1D)

3. Packed Pixel Stream, 16-bit Format, Long Packet, Data Type 00 1110 (0x0E)

4. Packed Pixel Stream, 18-bit Format, Long Packet, Data Type = 01 1110 (0x1E)

5. Pixel Stream, 18-bit Format in Three Bytes, Long Packet, Data Type = 10 1110 (0x2E)

6. Packed Pixel Stream, 24-bit Format, Long Packet, Data Type = 11 1110 (0x3E)

5.4.12 Execute Queue(0x16)

Execute Queue (0x16)是

发送到一个显示驱动的短数据包

,它

控制

和

同步

显示模块中的其他显示驱动以执行存储在执行队列中的

帧同步命令 (FSC)

。显示模块内的每个显示驱动可能已将一个或多个命令

存储在Execute Queue中

。

显示驱动接收执行队列:

1:如果使用Video模式,同步显示驱动以执行排队的 FSC 与下一个垂直同步脉冲或事件一致。

如果使用Cmd模式,同步显示驱动以在命令模式下执行排队的 FSC 与显示驱动程序内部处理的下一个撕裂效果一致。

2:接收执行队列的显示驱动程序包含一种机制,用于同步每个显示驱动程序以启动排队命令的处理。短包数据字节 0 和 1 的值未指定,被外设忽略。 允许发送到除主 DDIC 以外的 DDIC 的执行队列,但被忽略。

5.4.13 Do Not Use and Reserved Data Type

不应该使用具有四个LSB =0000或者1111的数据类型的代码。

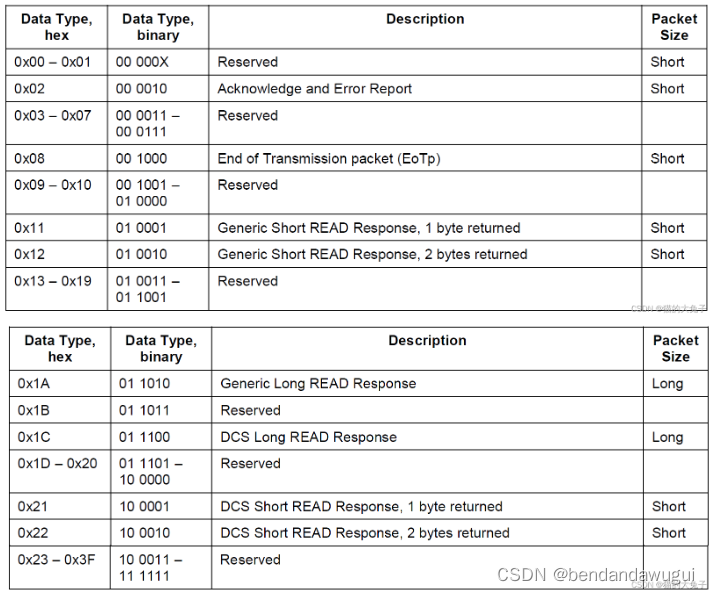

5.5 Data Type(peripheral(外设) -> Processor(主机))

与5.4对应的,也有peripheral -> Processor方向的Data type;DSI 管 Processor -> Peripheral 方向叫正向传输,

Peripheral -> Processor 叫反向

传输;

双向传输,只允许在

Low-power

模式下(D-PHY);

5.6 Peripheral -> Processor 方向传输事务

5.6.1 Acknowledge and Error Report,Data Type 00 0010 (0x02)

外设检测到主机端发送的

数据包有错误

,但是

主机一直没有发BTA

,则

外设

就没有机会

将错误报给主机

,所以当主机发送BTA时,如果外设之前检测到了错误,外设就会第一时间发送Acknowledge and Error Report来告诉主机,但是这里弊端也很明显,如果

主机不是每次传输都发送BTA来接收外设的回复,则主机接收到错误的报告后无法判断是哪次传输有错

。

在可纠正的ECC错误被检测到后,这个Acknowledge and Error Report会跟随被读到的data数据在同一个LP传输下传送给Host。

5.6.2 Generic long Read Respose,1 or 2 Bytes

这个packet是

为了响应来自主机

的Generic READ Request:

Data Types = 01 1010 (0x1A):即返回N个Bytes payload data;

5.6.3 Generic short Read Respose,1 or 2 Bytes

这个packet是

为了响应来自主机

的Generic READ Request:

Data Types = 01 0001 (0x11):即返回一个Byte Data0;

Data Types = 01 0010 (0x12):即返回两个Bytes Data0 与 Data1;

Note:如果命令本身可能由于不可纠正的ECC错误,SoT或者EoT同步错误而损坏,则外设就不会发送请求的READ数据包,而仅发送确认和错误报告包。

5.6.4 DCS Long Read Response with optional checksum,1 or 2 Bytes

这个 long packet 是为了响应来自 主机 的

DCS READ Request

:

Data Types = 01 1100 (0x1C):即

返回

N个Bytes payload data;

5.6.5 DCS short Read Response with optional checksum,1 or 2 Bytes

这个 short packet 是为了响应来自 主机 的

DCS READ Request

:

1.Data Types = 10 0001 (0x21):即

返回

一个Byte Data0;

2.Data Types = 10 0010 (0x22):即返回两个Bytes Data0 与 Data1;

5.7 外设针对Command和ACK Request的Responses

一般来讲,如果Host Processor在完成传输后,带了一个BTA,那么这就意味着外设需要回复1个或者多个packet,然后将总线的控制器移交给Host Processor;反之,如果Host Processor传输完成没有带BTA,那么外设就不会向Host Processor返回ACK或者Error;

当Host Processor向外设发送了BTA后,期望收到的responses如下:

1:若是一个non-Read的command,外设在没有检测到Error的前提下,将回复

Acknowledge

;

2:若是一个Read Request,外设在没有检测到Error的前提下,应该回复对方期望读取的数据;

3:若是一个Read Request,外设检测到1bit的ECC error,着1bit的Error能被修正,外设使用short packet或者long packet回复对方期望的数据,并且此传输中在后面跟上一个

4bytes

的

Acknowledge and error Report

,这个Error Report需要标记为ECC

Error-single Bit

;

4:若是一个Read Request,外设检测到1bit的ECC error,这种无法被修正,外设需要发送一个

4bytes

的

Acknowledge and error Report

,不需要发送对方期望读取的数据(因为ECC错误了),错误报告中应该设置ECC

Error-mulit bit

标志;

5:若是一个non_Read的command,外设检测到多bit的ECC Error,这种无法修正,外设将不执行这个命令,并且发送4bytes的Ackonledge and Error Report,错误报告中应该设置ECC Error—Mulit bit标志;

6:如果遇到一下情况:

-

SoT Error

-

SoT Sync Error

-

DSI VC ID Invalid

-

违反了 DSI 协议

-

无法识别的 DSI Command

外设发送 4 bytes 的

Acknowledge and Error Report

,设置相对应的合适的错误的 bit 标志;

7:如果遇到以下情况:

- EoT Sync Error

- LP Transmit Sync Error

- Playload Checksum Error

外设发送 4 bytes 的

Acknowledge and Error Report

,设置相对应的合适的错误的 bit 标志;如果是读的话,不会返回任何数据;

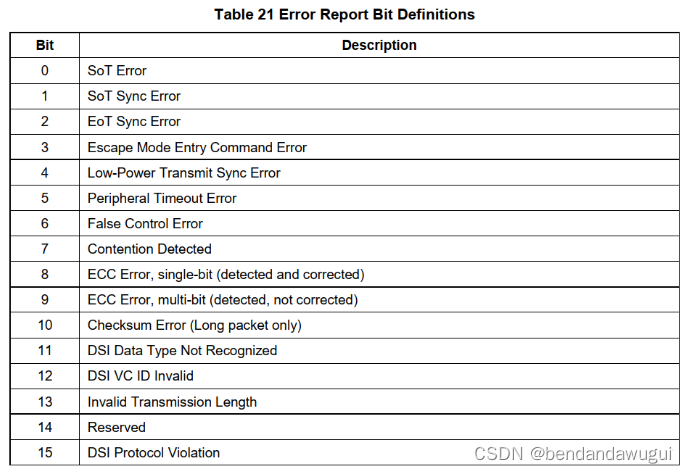

5.7.1 Ackowledge and Error Report以及Response to Read Request格式

Acknowledge and Error Report 用于

外设回复来自 Host Processor 的传输

;

如果在传输中,外设接收到的 Error 太多,会造成累计,当它返回 Report 给 Host 的时候,这些 Error 混在一起,Host 很难区分到底是那一笔传输出现错误;

Acknowledge and Error Report

属于 Short Packet 它的格式如下:

Byte 0

: Data Identifier (Virtual Channel ID + Acknowledge Data Type)

Byte 1: Error Report bits 0-7

Byte 2: Error Report bits 8-15

Byte 3

:ECC byte covering the header

Acknowledge 用 Trigger message

的形式发送:

Byte 0: 00100001 (shown here in first bit [left] to last bit [right] sequence)

Response to Read Request 返回来自 Host Processor 的 READ command 的数据,它可能是 Short Packet 也可能是 Long Packet;

Response to Read Request 的 Short 回复如下

:

Byte 0

: Data Identifier (Virtual Channel ID + Data Type)

Bytes 1, 2

: READ data, may be one or two bytes. For single byte parameters, the parameter shall be returned in Byte 1 and Byte 2 shall be set to 0x00.

ECC byte

covering the heade

Response to Read Request 的 Long 回复如下

:

Byte 0

: Data Identifier (Virtual Channel ID + Data Type)

Bytes 1-2

: Word Count N (N = 0 to 65, 535)

ECC byte

covering the header

N Bytes

: READ data, may be from 1 to N bytes

Checksum, two bytes (16-bit checksum)

If

Checksum is not calculated

by the peripheral,

send 0x0000

Error Reporting格式:

前面说了错误上报的是,是 Short Packet 的格式,发生某种错误的时候,是需要外设设置这种错误的 bit 的标志,这些 bit 的具体定义如下:

其中:

- bit 0 ~ bit 7 是物理层的错误;bit 8 ~ bit 9 是 ECC 的错误;其余的是 DSI 协议上的错误;

- ECC Error single-bit是可以被纠正的,所以,不会被重传;

- Checksum Error是可以被外设监测出来,并且报告给Host Processor的,Host Processor可以选择重传或者不重传;

- DSI Data type Not Recongnized Error的出现是因为外设收到了DSI标准不支持,或者这个外设不支持的Data type,比如一个显示设备,它没有支持18-bit的RGB,外设会直接扔掉或者叫放弃这个传输;

- DSI VC ID Invalid Error是当外设遇到了packet header中无法识别的VC ID 的时候;

- An Invalid Transmission Length Error发生在外设在某些特定的传输中,收到了非法的传输数据长度导致;比如WC 指定的长度和实际的payload的字节数不相等;

- 更多的关于error的详细描述和分析,可以参考DSI Spec

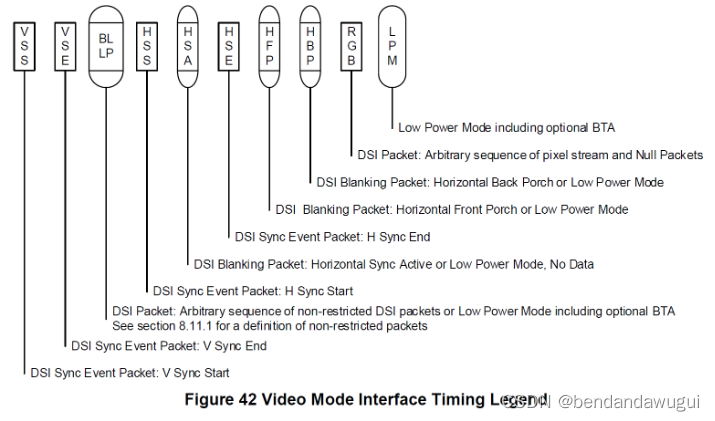

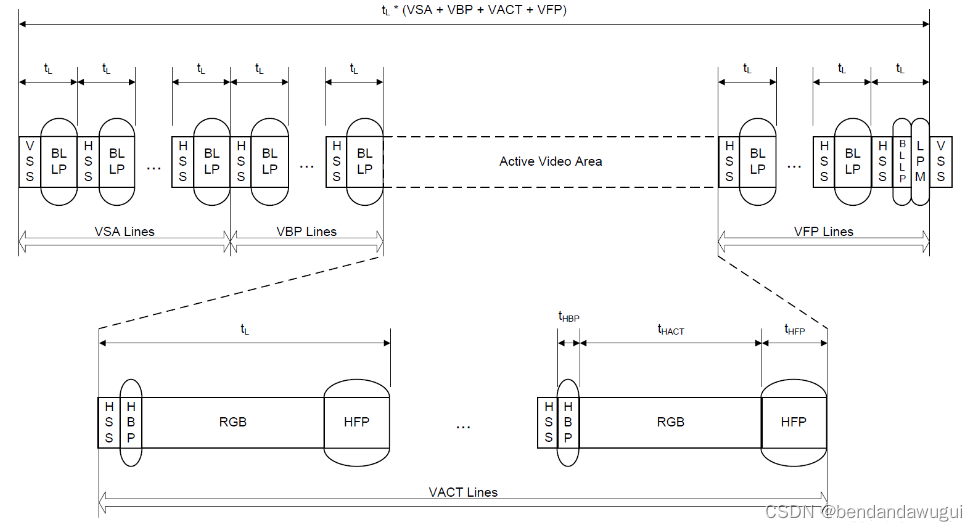

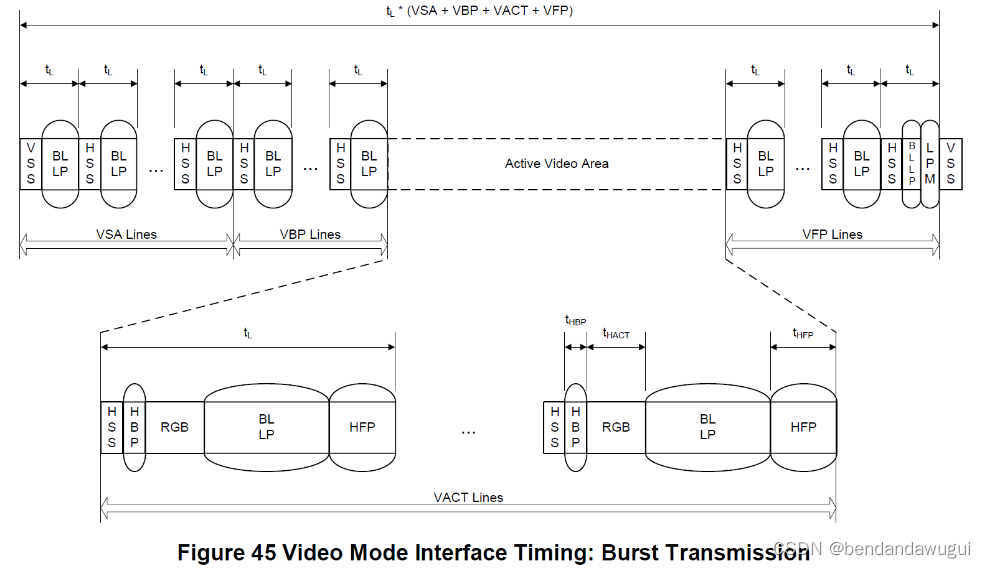

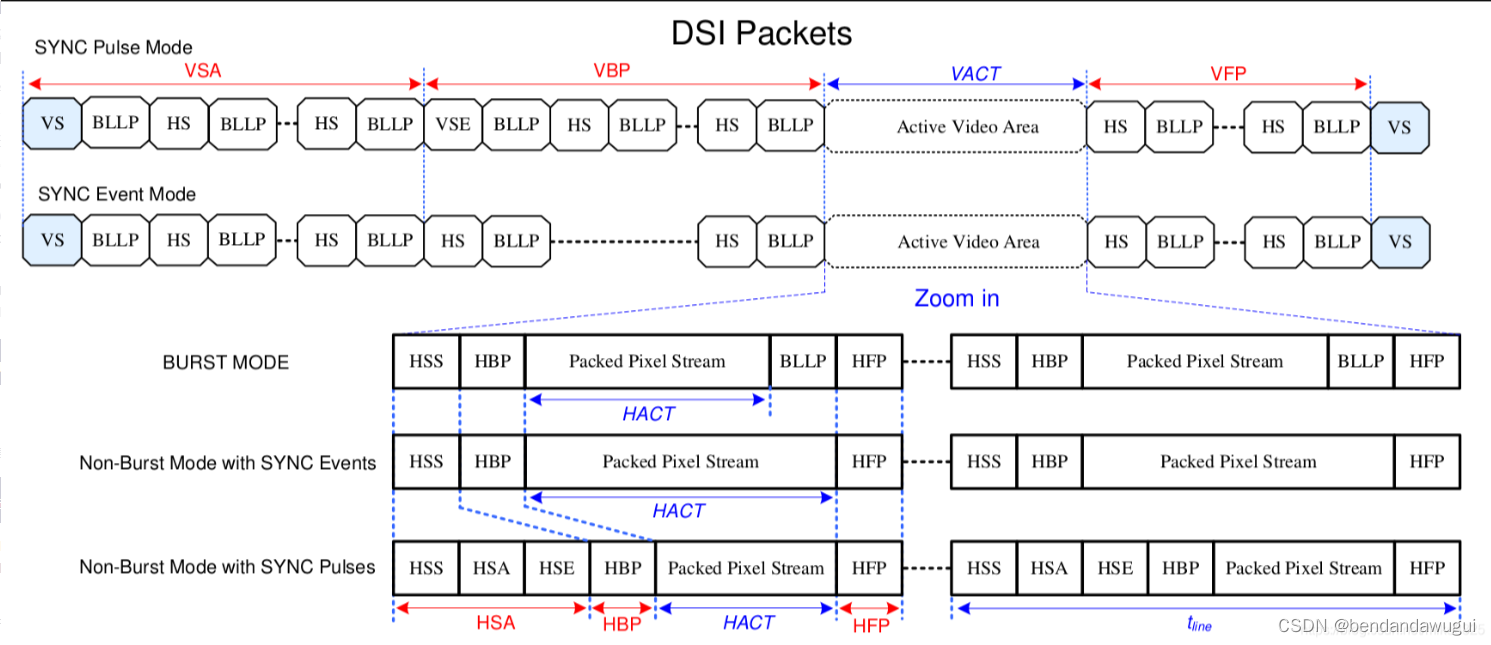

5.8 Video Mode 接口时序

Video模式外设需要实时传送像素数据。 Video模式

又有三种子模式

支持:

1,

Non-Burst Mode

with Sync

Pulses

:使外设能够精确地重建原始视频时序,包括同步脉冲宽度;

2,

Non-Burst Mode

with Sync

Events

:与上述类似,但不需要精确重建同步脉冲宽度,因此会使用单个 Sync Event;

3,

Burst mode

:RGB 像素数据 Packet 经过时间压缩,在扫描线期间留出更多时间用于 LP 模式(节省功耗)或将其他传输多路复用到DSI 链路上;

Note:这里,定义了一个叫做

BLLP

(

Blanking or low-Power interval

)的东西;视频数据包未传输到外设的时间段;

为了能够正常的进行PHY的同步,host processor需要

周期性的关闭High-Speed传输

,让Data Lane进入LP模式;至少每一帧开始都会做一次这样的操作;同时,Host Processor应该在每次水平扫描消隐的时候,切换到LP模式;

在BLLP期间,DSI链接可以做到下面的事情:

1:Host Processor保持在IDLE状态(LP-11),外设处于LP-RX

2:在Escape模式下,向外设传输1个或者多个非video packet;

3:在High-Speed模式下,向外设传输1个或者多个非video packet;

4:如果前一个processor-to-peripheral的传输以BTA结尾,使用Escape模式,从外设传输1个或者多个packets;

5:通过指定Virtual Channel ID,Host向多个不同的外设传输数据包;

Note:上图顶部有圆弧的代表数据包,长方形的代表时序的状态

。

5.7.1 Non-Burst Mode with Sync Pulse

使用这种格式,目的是通过DSI串行链路准确的传送DPI类型的时序,这包括匹配的DPI像素传输率,以及同步脉冲等定时时间的宽度,因此,同步周期是使用发送同步脉冲的开始和结束的分组来定义的。

5.7.2 Non-Burst Mode with Sync Events

这个是上面那个的简化模式,只有每隔同步脉冲的Start被传输,外设那边根据收到的Sync Event重新生成同步脉冲;像素按照和上面一阿姨那个的速度传输。

5.7.3 Burst Mode

这种模式下,大量的像素数据能够在更短的时间内进行传输,使用time-comressed burst格式;这样可以有效降低DSI的功耗。

比较:

下面是对三种子模式的深入解析:

MIPI-DSI 三种 Video Mode 理解_Eliot_shao的博客-CSDN博客

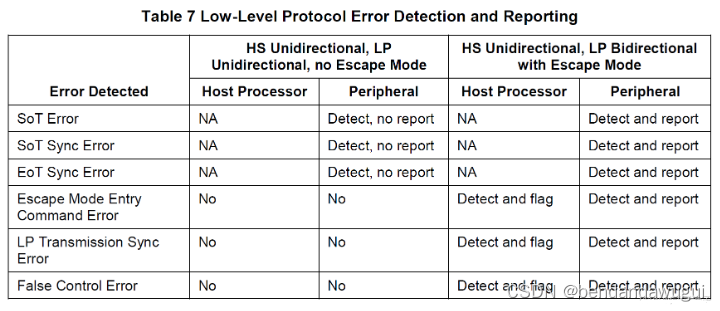

6:DSI 错误检测

对于DSI系统,

EMI,ESD

或者其他瞬态错误机制可能会

导致链路的一端进入错误

状态,或者链路传输损坏的数据,故错误检测机制对于系统的稳定性不言而喻,在DSI中,错误检测主要分三个部分:

1:Low-Level Protocol Errors

2:Contention Detection and Recovery

3:Additional Timers

6.1 Low-Level Protocal Errors

PHY 中的逻辑可以检测某些类别的协议错误, 这些错误

通过 PHY 协议接口传达给协议层

。 外设识别以下错误并将其存储为状态位,以便后续向主机处理器报告:

• SoT Error

• SoT Sync Error

• EoT Sync Error

• Escape Mode Entry Command Error

• LP Transmission Sync Error

• False Control Error

6.2 Contention Detection and Recovery

Contention是十分严重的问题,虽然非常罕见,但可能会导致系统挂起并强制进行硬重置或断电/通电循环以恢复。DSI 定义了两种机制来最大限度地减少此问题并实现更轻松的恢复:

1,用于 LP 模式争用的 PHY 中的争用检测器;

2,以及用于其他形式的争用和共模故障的定时器;

6.2.1 Contention Detection in LP Mode

在双向链路中,PHY 中的争用检测器应检测两种类型的争用错误:LP High 错误和 LP Low错误。当检外设测到任一争用故障时,应在错误报告字节中设置检测到争用。

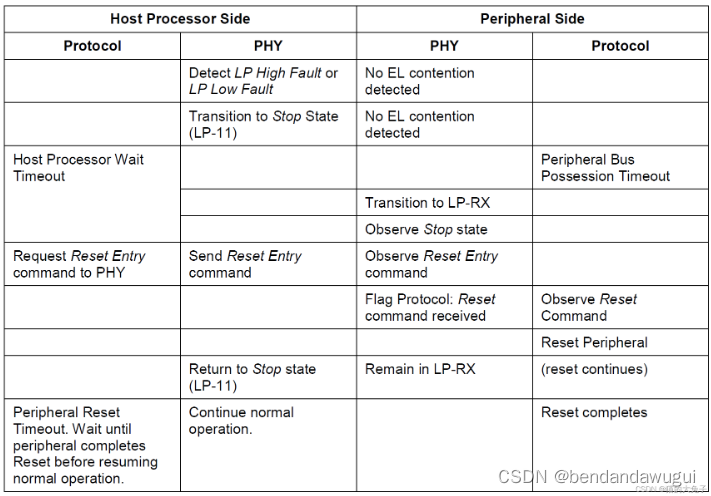

下面用一个流程举例:

6.2.2 Contention Recovery Using Timers

PHY 无法检测所有形式的争用。 使用适当的定时器超时机制可确保发生的任何争用都是有限的持续时间。即在传输过程使用一个定时器计数,则可以通过超时机制来判断传输是否出问题。目前共有四种超时机制:

1:HS RX Timeout (HRX_TO) in Peripheral

2:HS TX Timeout (HTX_TO) in Host Processor

3:LP TX-Peripheral Timeout (LTX-P_TO)

4:LP-RX Host Processor Timeout (LRX-H_TO)

6.3 Additional Timers

上述两种方法也未必能检测出所有错误,故DSI补充了另外即定时器,对其他操作进行检测。主要是为一下操作提供超时机制:

Turnaround Acknowledge Timeout (TA_TO)

Peripheral Reset Timeout (PR_TO)

Peripheral Response Timeout (PRESP_TO)

参考文献:

MIPI-DSI 协议深度解析-简单易懂协议详解_mipi dsi_maggie2014的博客-CSDN博客