一.fifo简介

1.fifo

first in first out的缩写,先进先出数据缓存器。

与普通存储器的区别:对外接口没有地址线。

由此所带来的

优点

是:不用处理地址信号,时序较简单。

缺点

是:不能像普通存储器那样自由读写某个地址的数据,只能顺序地写入,顺序地读出数据。

例如

:往fifo中存入100个数据,想要读出第50个,只能先读出前面那49个。

2.用途

(1)跨时钟域数据传输;

例如

:以50M的时钟写入,再将其以100M的时钟读出。如此,便完成了由低频域系统向高频域系统的传输。当然,反过来也行,即由高频域向低频域系统传输。

(2)作为不同位宽数据的缓冲。

例如

:ADC采样的数据是16位的,而upp(一种可用于连接AD模块和DSP的高速并行数据总线)接口配置的是8位的数据位宽。显然,这两个系统是不能直接相连的。怎么解决呢?

我们可以将其以16位的数据位宽写入fifo,再将其以8位的位宽读出,如此便可通过upp将数据发给DSP。

3.分类

分为两类。

(1)同步fifo:读写时钟为同一时钟,在时钟沿来临时,同时发生读写操作。

(2)异步fifo:读写时钟不一致,相互独立。

注意

:fifo两侧读写速度可以不一致,也就是说:写可以比读快,大不了写满了就写等待,等数据读了,空出位置来再继续写;同理:读的速度也能比写的速度快,大不了读空了就等等写。总而言之,就是读空了就读等待,写满了就写等待,只要保证前后传输数据的bps相等即可。

4.资源:(2种)

(1)B RAM:支持读写位宽不同(常用)

(2)D RAM:读写位宽必须相同。

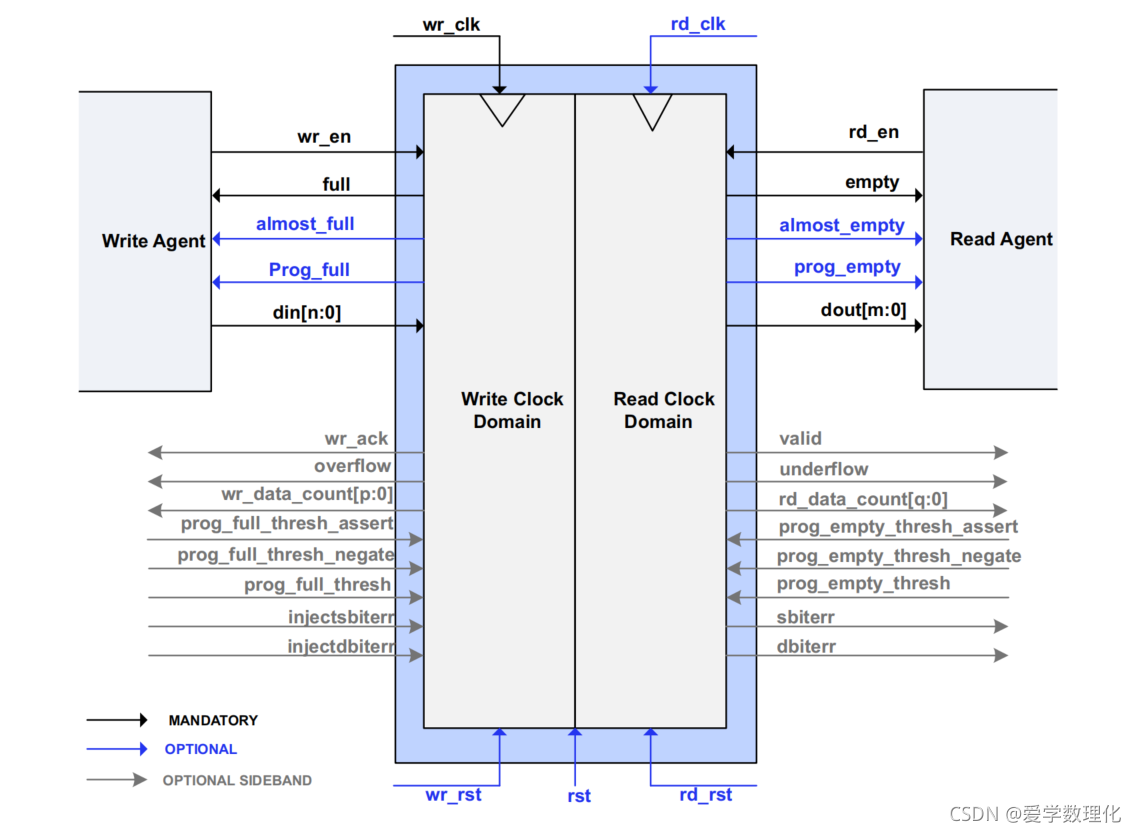

5.学习fifo必须记住的图

相关说明

:

(1)可以看到整个fifo模块分为Write Clock Domain(写时钟领域)和Read Clock Domain。

这里蕴藏杀机:

什么意思呢?

我来翻译翻译

当写模块往fifo写数据时,除了用得到full写满信号外,还用得上empty信号,对吧?

可是你看上图,empty明明是Read Clock Domain的信号呀,两个区域的时钟不一样,empty和full就是异步的,此时的empty还能直接拿来做写操作的指示信号吗?当然不能!同理,在进行读操作时,也需要对full信号进行同步处理。

full和empty的重要性我就不详说了,一旦用不对用不好就容易造成数据丢失。

这里我以写操作模块下如何抓取empty信号的上升沿为例作相关介绍:

字可能丑了点儿,字丑理不丑哈哈。要是不明白,欢迎私信我再详细说明。

(2)信号介绍(wr代表写,rd代表读)

①rst:复位。

分为写复位wr_rst和读复位rd_rst。当然,也可以整体复位rst

②clk时钟。

分为写时钟wr_clk和读时钟rd_clk

③使能_en

当使能打开,才能开始读和写。

④标志信号

full、empty:分别表示已经写满fifo和将fifo中所剩数据读完。

almost_full、almost_empty:快要写满/读空。二者相对于full、empty均提前一时钟拉高。

有什么好处呢?

你想啊,如果写满了fifo就直接将full拉高,当写模块知道时,有可能下一个数据已经发出了。这样就造成有一个数据丢失了。而almost_full,它干了个什么事儿呢?当检测到almost_full时,写模块知道下一个时钟fifo就写满了,与此同时,当前发送的这个数据是没有问题的。

⑤Prog_full、Prog_empty

可编程的写满、写空

例如

:我们把fifo容量设置为1024个数据,现在想写512个数据。此时就需要给一个标志:当写入数据个数>512时,拉高Prog_full.<512时,将其拉低。

⑥din[n:0]人为设定的向fifo写入的数据位宽

dout[m:0]人为设定的往fifo中读出数据的位宽

⑦wr_ack:虽然时钟是连续给的,但每一个时钟只能处理一次使能。这个ack信号就相当于一个反馈信号,每成功处理一次使能,就给一次回馈。

valid:用于判断读出来的数据是否是有效的

⑧overflow:上溢出。写满了的标志,告诉你不要再写了,写不下啦!!

underflow:下溢出。读空了的标志,告诉你不要再读了,一滴也没有了!!

⑨统计作用:

wr_data_count[p:0]指示往fifo中存了多少数据

wr_data_count[q:0]:指示fifo中含有多少数据可让你读出

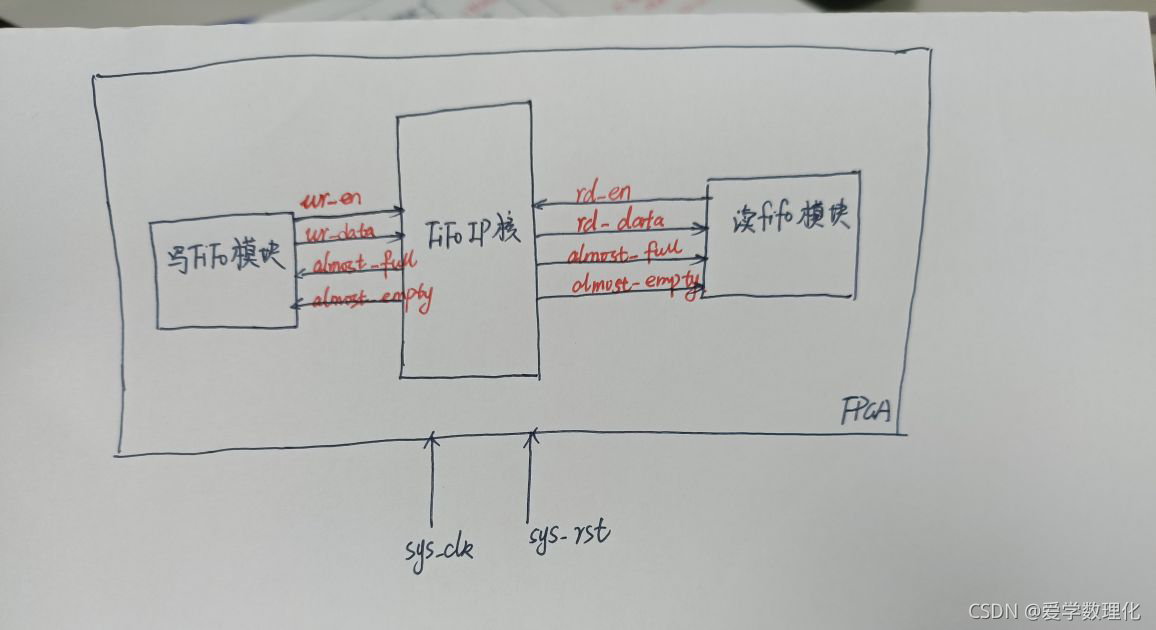

6.本工程实现的功能

向fifo中写数据,写满了再读,读空了又写。循环往复

具体实现框图如下:

注意

:(1)具体的代码编写已经详细批注;

(2)由于读fifo模块与写fifo模块具有很高的对称性,完全可以在写完写fifo,在其基础上改读fifo

(3)工程文件源码获取:q群:410397287

(4)感谢创龙和正原电子博主的相关分享。作为初学者,也希望得到大家的批评指正,希望大家不吝赐教。