目录

第一章引言本章介绍处理器。

它包含以下部分:

关于Cortex-M7处理器,请参阅1-2页。

1-6页上的组件块。

1-11页的接口信息。

支持的标准见第1-13页。

1-14页的设计过程。

1-15页的文档。

1-16页的产品修订。

1.1关于Cortex-M7处理器

Cortex-M7处理器是一款高效、高性能的嵌入式处理器,具有低中断延迟、低成本调试和向后兼容现有Cortex-M配置文件处理器的特点。处理器有一个有序的超标量管道,这意味着许多指令可以双重发出,包括加载/加载和加载/存储指令对,因为有多个内存接口。

处理器支持的内存接口包括:

- 紧耦合内存接口。

- 哈佛指令和数据缓存。

- AXI主(AXIM)接口。

- 专用的低延迟AHBP (low-latency AHB-Lite peripheral)接口。

- AHB-Lite从(AHBS)接口,为tcm提供DMA访问。

处理器有一个可选的内存保护单元(MPU),可以配置为保护内存区域。用于错误检测和纠正的纠错码(ECC)功能在实现时包含在数据和指令缓存中。TCM接口支持实现外部ECC,以提高可靠性和解决与安全相关的应用。

Cortex-M7处理器包括可选的浮点运算功能,支持单精度和双精度运算。参见第8章浮点单位。该处理器适用于需要快速中断响应特性的高性能、深度嵌入式应用。

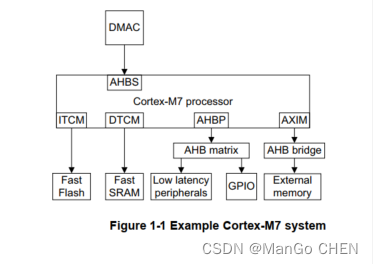

典型系统的处理器如图1-1所示。

1.1.1特性

Cortex-M7处理器的主要特点包括:

- 一个有序问题,具有动态分支预测的超标量管道。

- DSP扩展。

- ARMv7-M Thumb指令集,在ARMv7-M架构参考手册中定义。

- 堆栈指针(SP)。

- 硬件整数除法指令,SDIV和UDIV。

- 处理程序和线程模式。

- 拇指和调试状态。

- 自动处理器状态保存和恢复低延迟中断服务程序(ISR)的进入和退出。

- 支持ARMv7-M大端字节不变访问或小端访问。支持ARMv7-M不对齐访问。

- 实现低延迟中断处理的方法:

- 嵌套的矢量中断控制器(NVIC)与处理器紧密集成。

- 支持异常可持续性指令,如LDM, LDMDB, STM, STMDB, PUSH, POP和VLDM, VSTN, VPUSH, VPOP(如果处理器有浮点单元(FPU))。

- 一个低成本的调试解决方案,可选的能力:

- 实现断点。

- 实现观察点、跟踪和系统分析。

- 通过Instrumentation Trace Macrocell (ITM)支持printf()风格的调试。

- 可选TPIU (Trace Port Interface Unit)。

- 可选调试访问端口(DAP)。

- 支持可选的嵌入式跟踪宏单元(ETM)。有关更多信息,请参阅Arm* CoreSight” ETM-M7技术参考手册。

- 一个存储系统,包括一个可选的MPU和哈佛数据和指令缓存ECC。

- 可选的FPU (Floating Point unit)。

- 低功耗特性包括架构时钟门控,睡眠模式和唤醒中断控制器(WIC)。

- 可选的AXI到AHB桥,用于支持遗留内存系统。

1.1.2接口

Cortex-M7处理器有许多外部接口。

Cortex-M7处理器的外部接口如图1-4所示。

1.1.3配置选项

Cortex-M7处理器具有可配置选项,您可以在实现和集成阶段对其进行配置,以满足您的功能需求。

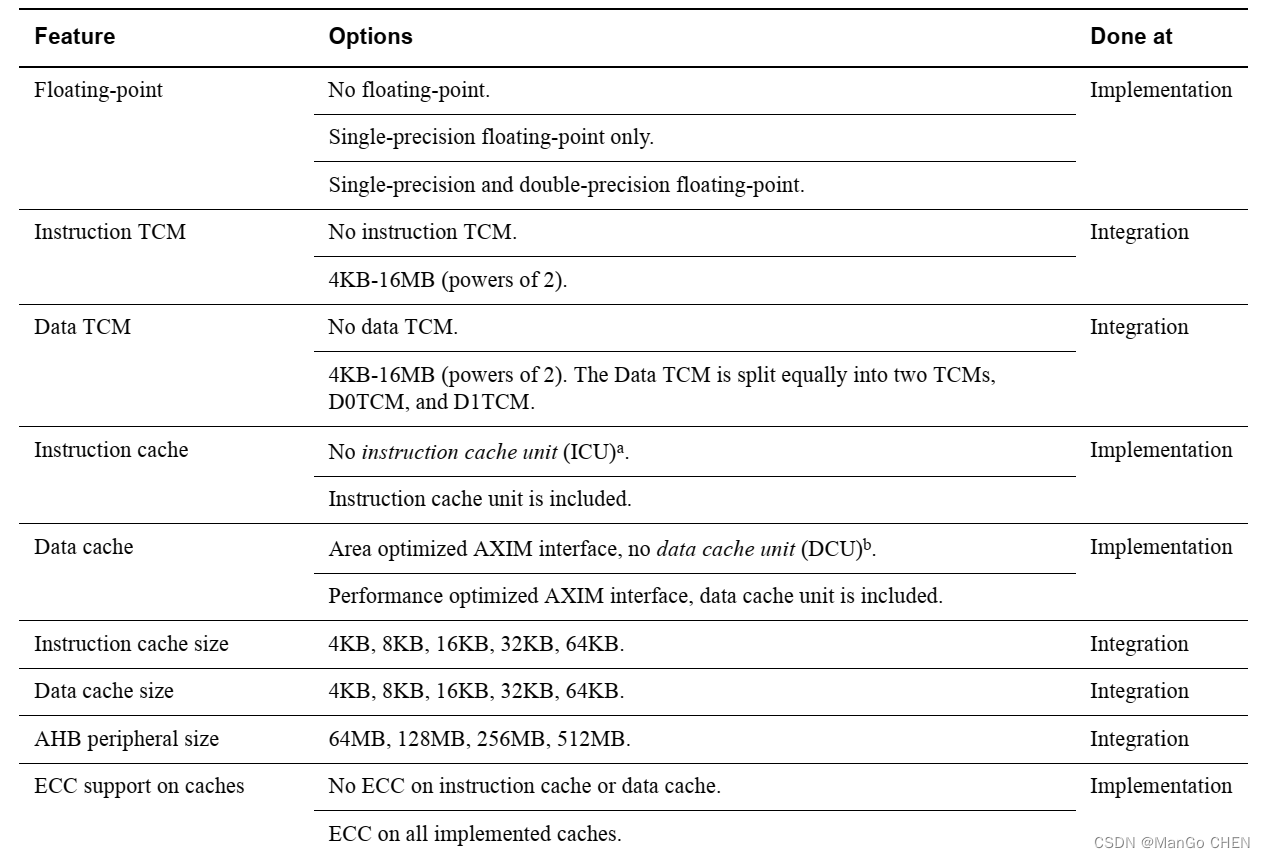

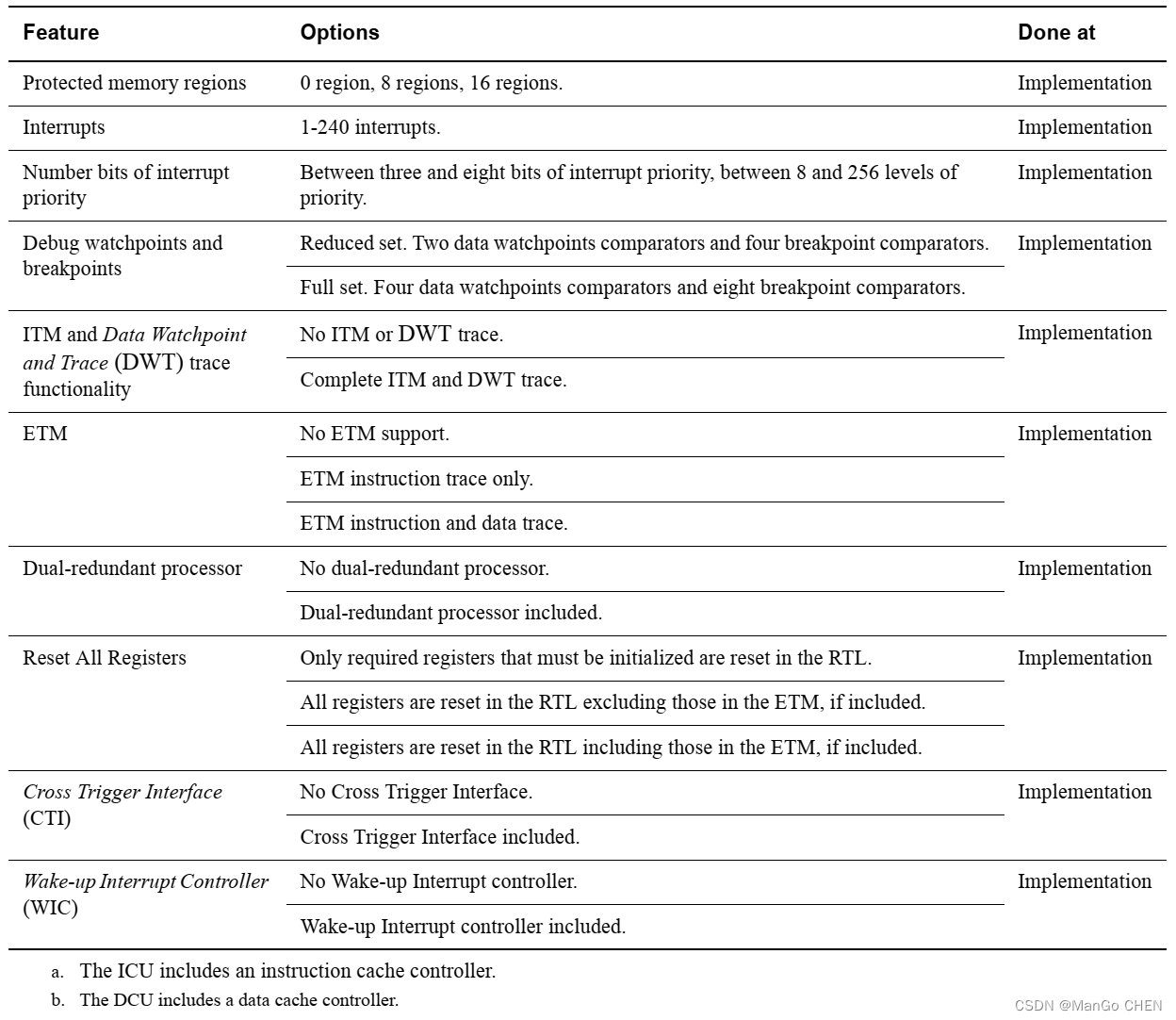

表1-1显示了处理器构建时的可配置选项。

1.2组件模块

Cortex-M7处理器有固定和可选的组件块。可选组件有:

唤醒中断控制器(WIC)

ITM。

FPU。

MPU。

指令缓存单元(Instruction cache unit)。

数据缓存单元(Data cache unit)。

CTI (Cross Trigger Interface)接口。

ETM。

所有其他组件都是固定的。

表1-1显示了处理器实现时的可配置选项。

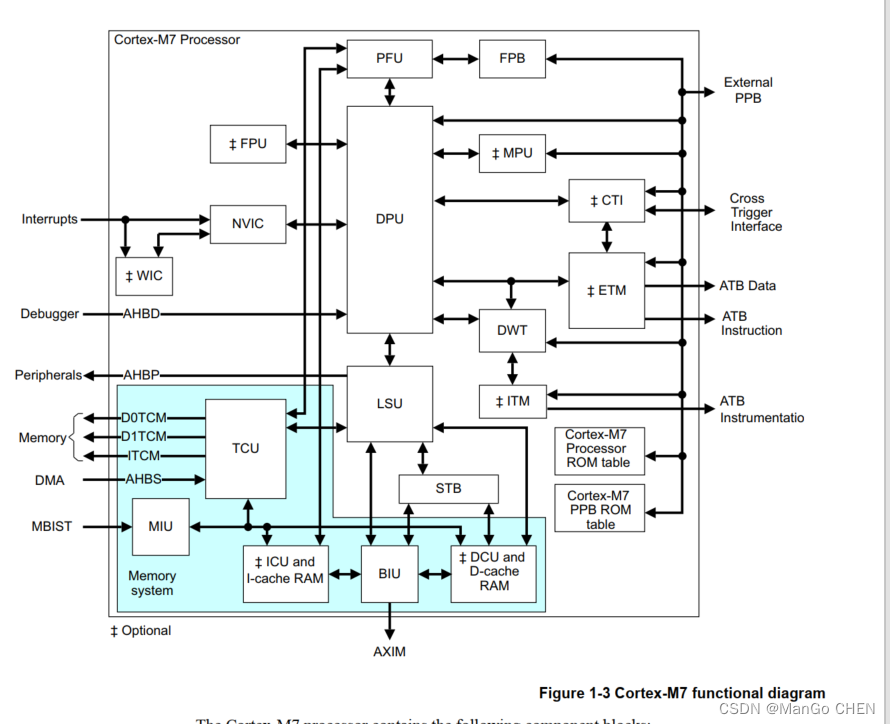

Cortex-M7处理器的可选部件和固定部件如图1-3所示。

Cortex-M7处理器包含以下组件块:

- 1-8页的数据处理单元。

- 1-8页的“预取单位”。

- 加载存储单元1-8页。

- 第1-8页的浮点单位,

- 嵌套矢量中断控制器在第1-9页。

- 唤醒中断控制器在第1-9页。

- 1-9页的内存系统。

- 1-10页的内存保护单元。

- 1-10页的Cortex-M7处理器和PPB ROM表。

- 交叉触发接口单元在第1-10页。

- ETM在1-10页。

- 调试和跟踪1-10页中的组件。

1.2.1数据处理单元

数据处理单元(DPU)提供:

- 具有六个读端口和四个写端口的并行整数寄存器文件,用于大规模双问题。

- 广泛的转发逻辑,以尽量减少联锁。

- 两个ALU,其中一个ALU能够执行SIMD操作。

- 单个MAC管道能够32×32位+64位→64位,具有两个周期结果延迟和每个周期一个MAC吞吐量。

- 支持与操作数相关的早期终止的单除法单元。

1.2.2预取单元

PFU (Prefetch Unit)

提供:

- 64位指令获取带宽。

- 4×64位预取队列,从DPU管道操作中解耦指令预取。

- 分支目标地址缓存(BTAC)用于分支预测器状态和目标地址的单周期转换。

- 未指定BTAC时的静态分支预测器。

- 在解码器和处理器管道的第一个执行阶段转发直接分支的早期解析标志。

1.2.3负载存储单元

负载存储单元(LSU)

提供:

- 双32位负载通道通往TCM、数据缓存和AXIM接口,提供64位负载带宽和双32位负载能力。

- 到AHB接口的单个32位加载通道。

- 单个64位存储通道。存储缓冲以提高存储吞吐量,并最大限度地减少数据和指令读取的RAM争用。

- 为TCM、AHBP和AXIM提供单独的存储缓冲,以实现服务质量(QoS)和特定接口的优化。

1.2.4浮点单元

可选的

FPU (Floating Point Unit)

提供:

- 延迟浮点上下文保存。浮点状态的自动堆叠被延迟到ISR尝试执行浮点指令。这减少了进入ISR的延迟,并删除了浮点上下文(不使用浮点的ISR除外)。单精度(C语言浮点型)数据处理操作说明。

- 双精度(C双类型)数据处理操作的可选指令。

- 结合乘法和累积指令,提高精度(融合MAC)。硬件支持转换,加法,减法,乘法可选累加,除法和平方根。

- 硬件支持标准和所有IEEE标准754-2008舍入模式。

- 32位单精度寄存器或16位双精度寄存器。

- 更多信息请参见第8章浮点单元。

1.2.5嵌套矢量中断控制器

NVIC与核心紧密集成,实现低延迟中断处理。功能包括:

- 外部中断,可配置从1到240。这是在实现时配置的。可配置的中断优先级从8到256。

- 在实现时配置。中断的动态重优先级。

- 优先级分组。这使得可以选择抢占中断级别和非抢占中断级别。

- 支持尾链和延迟到达中断。这样可以实现背靠背的中断处理,而不需要在中断之间保存和恢复状态。

- 参见第7章嵌套矢量中断控制器了解更多信息。

1.2.6唤醒中断控制器

可选的WIC提供超低功耗睡眠模式支持。

- 更多信息请参见7-3页的低功耗模式。

1.2.7记忆系统

可选的存储系统包括:

- 一种总线接口单元(BIU),具有可配置的amba4 AXI接口,可以支持高性能L2内存系统。

- 扩展的AHB-Lite接口,支持低延迟系统外设。

- TCU (TCM Control Unit),具有TCM接口,支持外部ECC逻辑用于系统访问tcm的AHB从(AHBS)接口。

- 指令缓存和数据缓存单元,可选纠错码(ECC)。

- 内存内置自检(MBIST)接口,由MBIST接口单元提供(个人)。

- 内存系统支持在线MBIST,在处理器运行时,可以通过MBIST接口访问RAM阵列。

- 在生产测试期间也支持MBIST。

- 更多信息参见第5章内存系统。

1.2.8存储缓冲区

当存储操作离开加载/存储管道并被DPU提交时,存储缓冲区(STB)保存这些操作。从STB,存储可以请求访问DCU中的缓存RAM,请求BIU初始化补码,或者请求BIU在AXIM接口上写数据。STB可以将多个存储事务合并为单个事务,如果它们位于相同的64位对齐地址。

1.2.9内存保护单元

可选的MPU具有可配置的内存保护属性。它包括多达16个内存区域和子区域禁用(SRD),可以有效地使用内存区域。它还能够启用实现默认内存映射属性的后台区域。有关更多信息,请参阅第6章内存保护单元。

1.2.10 Cortex-M7处理器和PPB ROM表

这两个ROM表使调试器能够识别并连接到CoreSight调试组件。有关更多信息,请参见第9章调试。

1.2.11交叉触发接口单元

可选的CTI使调试逻辑和ETM能够相互交互,并与CoreSight的其他组件进行交互。参见第10章交叉触发器接口。

1.2.12 ETM

可选的ETM在配置时提供仅指令或指令和数据跟踪功能。在Cortex-M7处理器中没有实现跟踪延迟特性。看到Arm“CoreSighr”ETM-M7技术参考手册了解更多信息。

1.2.13调试和跟踪组件

- 可配置断点单元(FPB)实现断点。

- 用于实现观察点、数据跟踪和系统分析的可配置数据监视和跟踪(DWT)单元。

- 可选ITM,用于支持printf()风格的调试,使用instrumentation跟踪接口适用于。

- 将片上数据传递到跟踪端口分析仪(TPA),包括单线输出(SWO) 模式。

- 调试器对系统中所有内存和寄存器的访问,包括对内存映射设备的访问,在内核停止时对内部内核寄存器的访问,以及在断言重置时对调试控制寄存器的访问。

1.3接口

处理器包含以下外部接口:

- AHBP接口

- AHBS nterface。

- AHBD接口。

- 外部专用外围总线。

- 作为接口TCM mterface。

- 交叉触发界面在1-12页。

- MBIST接口,页面1-12。

- 1-12页的AXIM接口。

1.3.1AHBP接口

AHBP (AHB-Lite外设)接口提供适合低延迟系统外设的访问。

它支持非对齐内存访问、用于缓冲写数据的写缓冲区以及多处理器系统的独占访问传输。

更多信息请参见第5-25页的AHB外设接口。

1.3.2AHBS接口

AHB-Lite从接口(AHBS)使系统能够访问tcm。更多信息请参见第5-33页的AHB从接口。

1.3.3AHBD接口

AHB-Lite调试(AHBD)接口提供对Cortex-M7处理器和完整内存映射的调试访问。有关更多信息,请参见第9-7页的关于AHBD接口。

1.3.4外部专用外设总线

APB外部PPB (EPPB)可以在连接到处理器的系统中访问与coresight兼容的调试和跟踪组件。

1.3.5ATB接口

ATB接口输出用于调试的跟踪信息。ATB接口兼容CoreSight架构。有关更多信息,请参阅Arm“CoreSight”架构规范(v2.0)。

1.3.6TCM接口

处理器最多可以有两个TCM内存实例,指令TCM (ITCM)和数据TCM (DTCMD)。访问ITCM是通过ITCM 64位宽接口。通过DiTCM 32位wade接口和32位wide DOTCM接口访问DTCM。DTCM访问是分开的,这样低的单词总是访问DOTCM,高的单词总是访问DITCM。两个TCM实例的大小都是可配置的,4KB-16MB的2次方。更多信息请参见5-36的TCM接口nformation。

1.3.7交叉触发接口

处理器包括一个可选的交叉触发接口单元,其中包括一个适合使用交叉触发矩阵连接到外部CoreSight组件的接口。参见第10章交叉触发接口了解更多信息

1.3.8MBIST接口

MBIST接口用于生产测试时对ram进行测试。Cortex-M7处理器还允许ram在正常执行期间使用MBIST接口进行测试。这被称为在线MBIST有关MBIST接口和在线MBIST的更多信息,请联系您的实现团队

1.3.9AXIM接口

AXI主(AXIM)接口提供对外部存储器系统的高性能访问。AXIM接口支持使用Arm CoreLink L2C-310 2级缓存控制器。L2C-310不支持独占缓存配置。有关更多信息,请参阅第5-8页的AXIM接口。

1.4支持标准

处理器符合或实现下列所述的规范:

Arm的体系结构。

总线架构。

调试嵌入式跟踪宏单元浮点单元。

本书补充了架构参考手册、架构规范、协议规范和相关的外部标准。

它不会复制这些来源的信息。

1.4.1Arm架构

Cortex-M7处理器实现了ARMv7E-M架构配置文件。参见Arm“v7-M架构参考手册”。Cortex-M7处理器FPB实现了Flash补丁断点版本2架构修订

1.4.2总线架构

处理器提供了一个:外部接口是amba3 AHB-Lite协议的一种变体。符合amba4axi标准的外部接口该处理器还使用amba3 APB协议和amba3 ATB协议实现了CoreSight和其他调试组件的接口有关更多信息,请参见:Arm“AMBA”AXI和ACE协议规范。Arm“AMB4°3 AHB-Lite协议(v1.0)。Arm amba3 APB协议规范。Arm“AMBA”3 ATB协议规范

1.4.3调试

处理器的调试特性实现了Arm调试接口架构。参见Arm“调试接口v5架构规范”。

1.4.4嵌入式跟踪宏单元

在实现时,处理器的跟踪特性实现了Arm Embedded trace Macrocell (ETM)v4架构。参见arm嵌入式跟踪宏单元结构光谱ETM4。

1.4.5浮点单元

根据您的实现,具有FPU的Cortex-M7处理器可以仅具有单精度或单精度和双精度浮点数据处理,这是ARMv7E-M架构的一部分,由FPv5架构定义。它提供了符合ANSI/IEEE Sid 754-200s (IEEE二进制浮点算术标准)的浮点计算功能。

1.5设计过程

Cortex-M7处理器作为可合成的RTL交付,必须通过实现、集成和编程过程,然后才能在产品中使用它。以下定义描述了设计流中的每个顶级流程。实现实现者配置并综合RTL集成集成商将实现的设计连接到SoC中。这包括将其连接到存储系统和外设。编程系统程序员开发配置和初始化处理器所需的软件,并测试所需的应用软件。流程中的每个阶段都可以由不同的一方执行。实现和集成的选择会影响处理器的行为和特性。对于mcu,通常由一个设计团队在合成完整的设计之前集成处理器。或者,团队可以自己合成处理器或部分集成处理器,以产生一个macrocell,然后由一个单独的团队集成。最终装置的运行取决于:构建配置实现者选择影响RTL源文件预处理方式的选项。这些选项通常包括或排除影响产生的宏单元的一个或多个区域、最大频率和特征的逻辑。配置输入积分器通过将输入绑定到特定值来配置处理器的某些特性。在进行任何软件配置之前,这些配置会影响启动行为。他们还可以限制软件的可用选项。软件配置程序员通过将特定的值输入寄存器来配置处理器。这会影响处理器的行为。请注意本手册参考了适用于构建配置选项的实现定义的特性。引用包含的功能意味着适当的构建和pir。选择配置选项。对启用特性的引用是指已由软件配置的特性。

1.6文档

Cortex-M7处理器文档可以帮助您完成正确使用该产品所需的顶层实现、集成和编程过程。Cortex-M7处理器文档包括《技术参考手册》、《集成与实现手册》和《用户指南参考资料》。技术参考手册技术参考手册(TRM)描述了功能和功能选项对Cortex-M7处理器行为的影响。在设计流程的所有阶段都需要它。由于Cortex-M7处理器的实现和集成方式不同,TRM中描述的一些行为可能不相关。如果您正在对Cortex-M7处理器进行编程,请与实现者联系以确定。实现的构建配置。在实现处理器之前执行了什么集成(如果有的话)。集成与实施手册整合与实施手册(IIM)描述:可用的构建配置选项和选择它们时的相关问题如何使用生成配置选项配置注册传输级别(RTL)。如何将处理器集成到SoC中。这包括对集成套件的描述,并描述了积分器必须连接的引脚,以便为所需的集成配置宏单元。如何在设计中实现处理器。这包括地板规划指南,内存自动测试(MBIST)和测试设计(DFT)信息,以及如何在处理器上执行网表动态验证。完成设计的集成和实现的过程。Am产品交付包括参考脚本和使用它们来实现您的设计的信息EDA工具供应商提供的参考方法文档是对IIM的补充。IIM是一本保密的书,只对被许可方开放。用户指南参考资料本文档提供了Arm合作伙伴可以配置的参考资料,并包含在Arm Cortex-M7处理器的用户指南中。一般。本参考资料中的每一章都可能对应于用户指南本参考资料中的每个顶级部分可能对应于用户指南中的一章。但是,您可以以任何方式组织这些材料,但要遵守Arm提供这些材料的许可协议的条件有关与Cortex-M7处理器相关书籍的更多信息,请参阅第11页的附加阅读。

1.7产品修改

本节介绍各产品版本在功能上的差异:ROP0第一个版本。罗普尔更新内容如下:修复了各种工程勘误表。更新CPUID复位值,@x410FC271。ROP2本版本修改内容如下:更新CPUID复位值,@x410FC272。修复各种工程勘误表。rlpo本次发布的变更内容如下更新CPUID复位值,@x411FC270。增加CTLPPBLOCK[3:0]允许寄存器锁定ITCMCR。DTCMCR, AHBPCR, VTOR防止不必要的更新。增加了ACTLR位功能,允许低能力的AXI系统禁用对DEV/SO内存的AXI读取,并禁用对共享内存的独占读/写,直到AXI上所有未完成的读/存储完成。增加MBISTIMPERR[2]输出到MBIST接口,当试图访问未实现的内存时提供一个错误改进了与同一TCM相关的AHBS和软件活动的同时处理。RLP2本版本修改内容如下:更新CPUID复位值,@x411FC272。增加了描述推测访问的部分,处理器使用推测访问来提高性能。更新了描述为强排序内存或设备内存生成的AXI事务的部分。