计算机组原,系统总线,总线概念,结构,分类,特性指标,总线举例

总线的基本概念

一、什么是总线

1、总线是连接各个部件的信息传输线,是各个部件共享的传输介质

二、总线上信息的传送

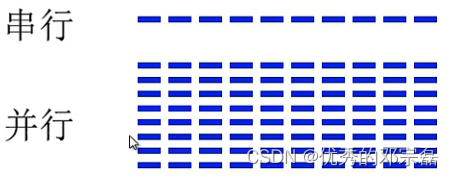

1、串行传输,单条线路一个个比特传输,稳定性强

2、并行传输,多条线路同时传输。

三、总线结构

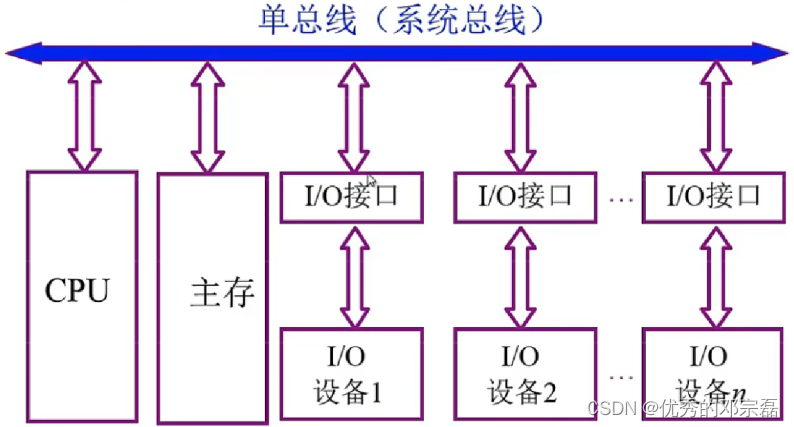

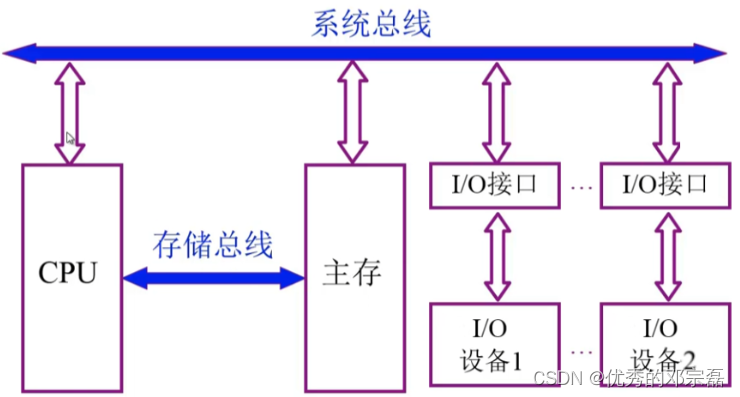

1、单总线(系统总线)

1.1、这里的主存就是内存,对应的,辅存或外存,就是如硬盘,U盘之类的外部存储器

1.2、任意时刻只能有一对部件在总线上传递信息,如果IO设备接收了消息并将其传递至总线,就会中断当前在使用总线的其他部件,比如中断正在和内存进行运算的CPU

1.3、总线性能将成为整体性能的瓶颈

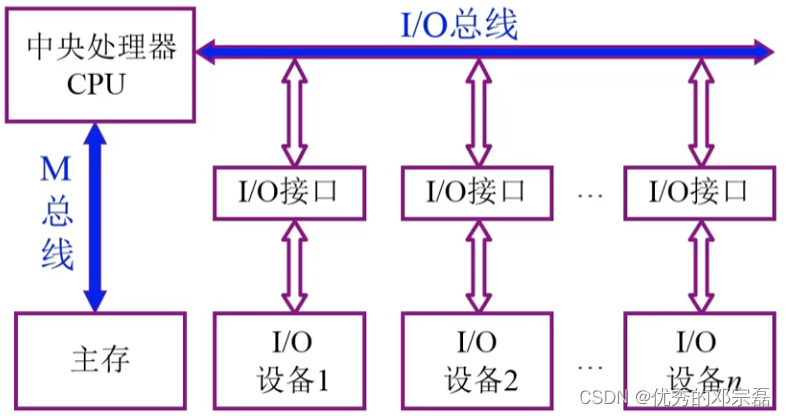

2、面向CPU的双总线结构

2.1、从CPU引申出两条总线,一条IO总线与各种IO设备进行信息交互,一条M总线和内存进行信息交互

2.2、由于内存和IO之间没有直接的交互通路,当出现需要让IO设备和内存直接交互的情况时,CPU还是会被打断当前运算而去进行内存和IO的数据交互

3、以存储器为中心的双总线结构

3.1、所有设备均通过系统总线相连,CPU和内存单独使用存储总线相连

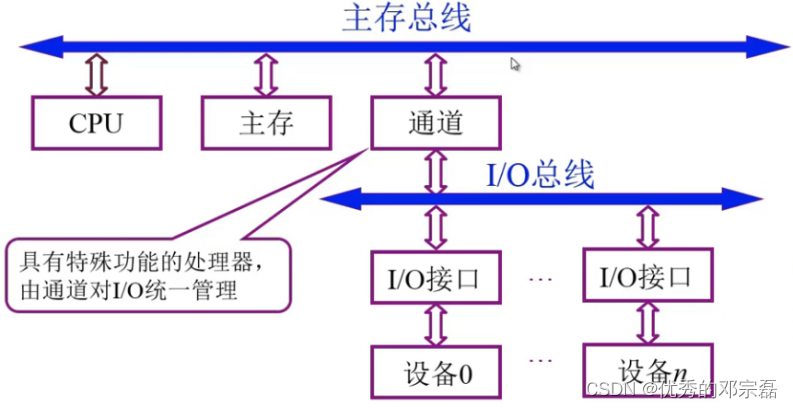

4、双总线通道交互的结构

4.1、CPU和内存使用主存总线交互,IO设备统一使用IO总线交互

4.2、IO总线和主存总线之间通过通道交互,通道本身是一个具有特殊功能的处理器,由通道对IO统一管理

4.3、通道的相关程序一般由操作系统编写

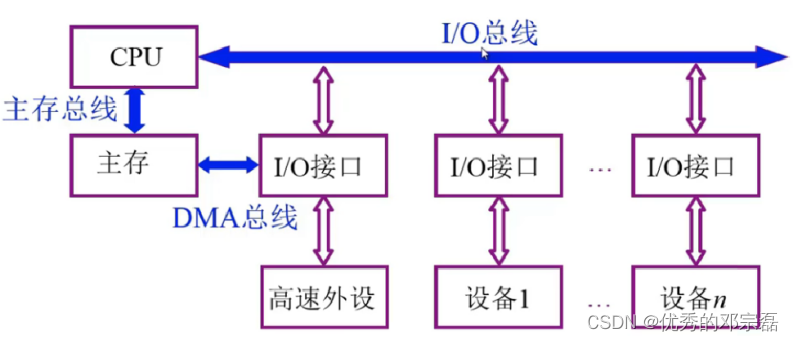

5、三总线结构(DMA总线)

5.1、在以CPU为中心的双总线结构中引入DMA总线用于提供内存和高速的IO设备之间的交互

5.2、高速IO外设与IO总线和DMA总线相连,其余外设与IO总线相连

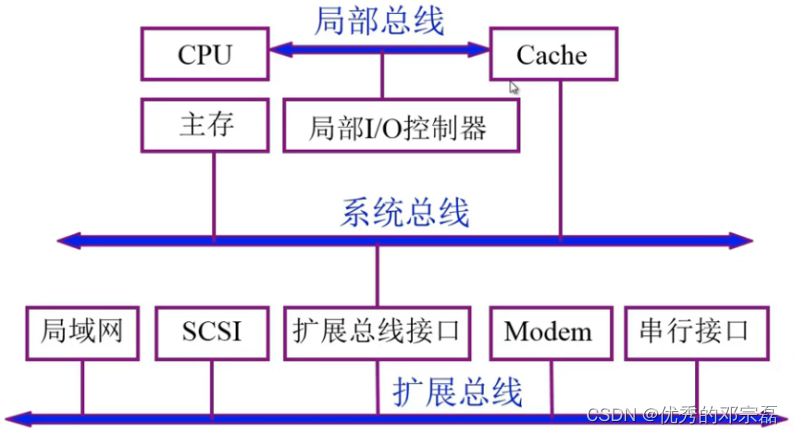

6、三总线结构(局部总线)

6.1、CPU的运行速度成长性远高于内存速度的成长性,导致在发展中内存的速度成为了整体性能的瓶颈

6.2、引入小容量,高速度的存储器:高速缓存区cache,先于内存和CPU交换数据,各部件与各总线的连接结构如下

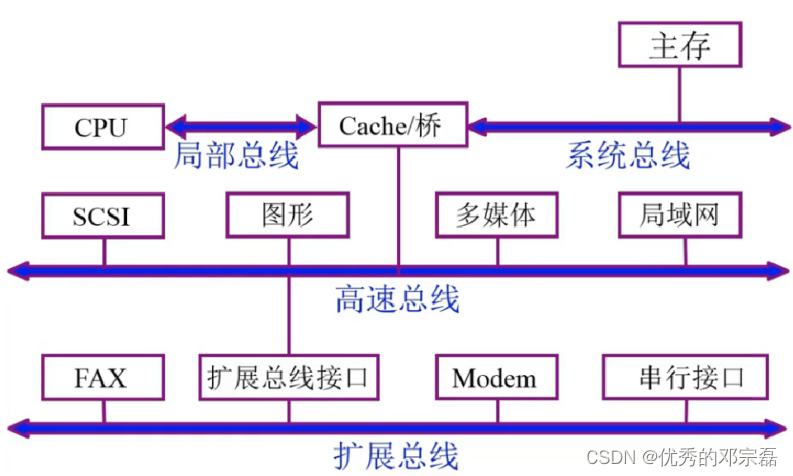

7、四总线结构

7.1、将高速设备用高速总线相连,低速设备用低速总线相连

7.2、CPU和高速缓存区cache用局部总线相连,cache和内存用系统总线相连

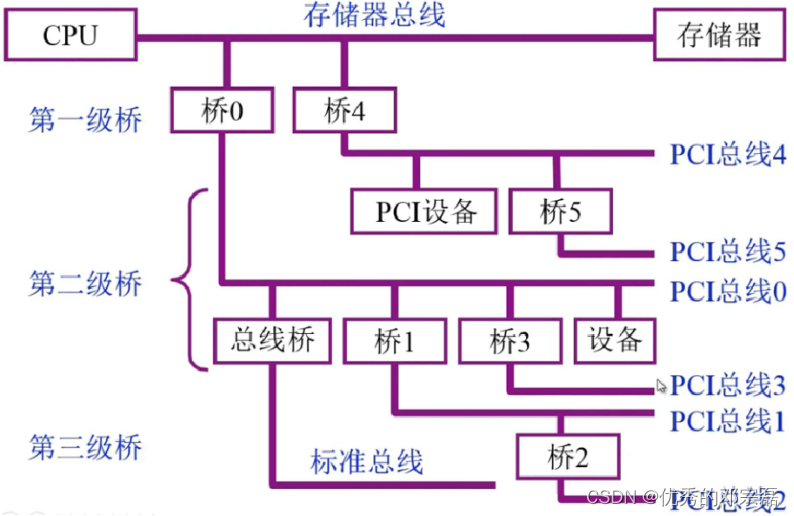

8、多级CPI总线结构

8.1、通过PCI桥扩展出总线以适配繁多的部件速度

四、总线的分类

根据位置划分

1、片内总线:位于芯片内部的总线

2、系统总线:计算机各个部件之间的信息传输线

2.1、数据总线:传送数据信号,一般而言是双向的,与机器字长,存储字长有关(一般是数据总线宽度小于等于机器字长)

2.2、地址总线:传送地址信号,一般是单向的,与存储地址,IO地址有关(一般是地址总线的宽度小于等于地址寄存器的宽度)

2.3、控制总线:传送控制信号,有出有入,控制功能如:存储器读、写,总线允许,中断确认

3、通信总线:用于计算机系统之间或计算机系统与其他系统(如控制仪表,移动通信等)之间的通信,按照传输的方式划分有:串行通信总线,并行通信总线

五、总线特性以及性能指标

1、机械特性:尺寸,形状,管脚数和排列顺序

2、电气特性:传输方向和有效的电平范围

3、功能特性:每根传输线的功能,如:地址总线,数据总线,控制总线以及其他类型的总线

4、时间特性:信号的时序关系

5、总线的性能指标:

5.1、总线宽度:同时可以传输数据的位数,就是总线数据线的根数。

5.2、标准传输率:每秒传输的最大字节数

5.3、时钟同步/异步:同步和不同步

5.4、总线复用:地址线和数据线复用(如8086,20根地址总线中的16条同时作为数据总线),复用可以减少管脚的数量,进而减小芯片的大小

5.5、信号线数:地址线,数据线和控制线的总和

5.6、总线控制方式:突发、自动、仲裁、逻辑、技术

5.7、其他指标:负载能力,如可挂载的IO设备的数量

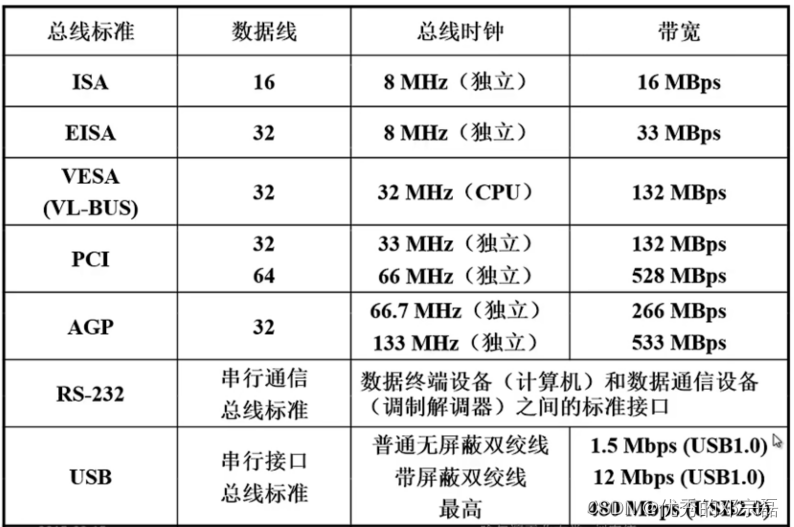

六、总线标准举例