set_property BITSTREAM.CONFIG.SPI_BUSWIDTH 4 [current_design]

set_property BITSTREAM.CONFIG.EXTMASTERCCLK_EN div-1 [current_design]

set_property BITSTREAM.GENERAL.COMPRESS TRUE [current_design]

set_property CONFIG_VOLTAGE 3.3 [current_design]

set_property CFGBVS VCCO [current_design]

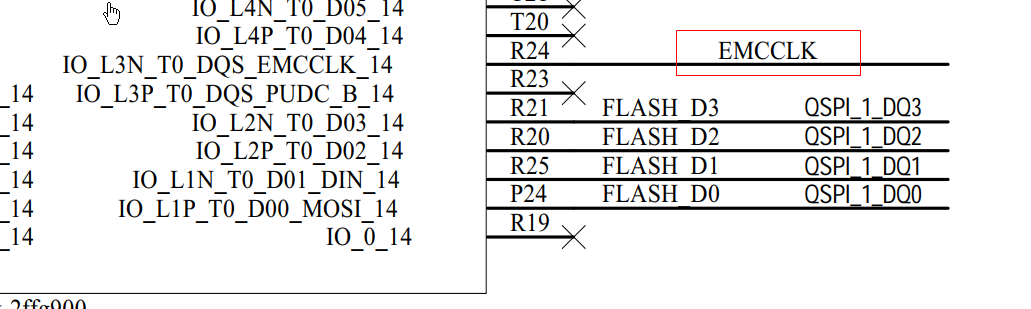

外部主配置时钟(EMCCLK)选项

默认情况下,主配置模式使用内部生成的配置时钟源CCLK。使用此时钟选项很方便,因为不需要外部

时钟发生器

源。但是,对于配置时间缩短至关重要的应用,应使用外部主配置时钟(EMCCLK)。EMCCLK时钟允许使用比具有主CCLK频率容差(FMCCKTOL)的FPGA内部时钟更精确的外部时钟源。例如,当主CCLK的最大频率为100 MHz时,50%的容差意味着ConfigRate设置不能超过66 MHz。但是,外部时钟源可以在规范允许的情况下以最快的速度应用。7系列FPGA支持在主模式下动态切换到外部时钟源(EMCCLK)的能力。使能EMCCLK时钟可以通过:

-

使能ExtMasterCclk_en比特流产生选项;将FPGA上的EMCCLK连接到主板的

振荡器

或其他时钟源;定义EMCCLK目标电压。以下方法可以实现这一点:

- Bank14具有另一个已定义IOSTANDARD的管脚。Bank14上定义的电压自动应用于EMCCLK; EMCCLK信号在配置后的设计中使用,并定义了IOSTANDARD。

EMCCLK信号必须实例化,并在提供I/O标准定义的设计中使用,因为EMCCLK是一个多用途引脚,或者电压电平将取自Bank14中定义的另一个引脚。

将EMCCLK输入连接到板上的振荡器或其他时钟源,并当做关键信号进行布线处理,使用良好的信号完整性设计实践,特别是对于非常高速的时钟,以避免配置过程中出现错误。