SDRAM:

Synchronous Dynamic Random Access Memory

同步动态随机存储器传输

优点:空间存储量大、

读写速度快、

价格相对便宜

缺点:控制逻辑复杂

所以我的大小为:4 x 2^13 x 2^9 x 16 = 268435456 bit = 262144 kbit = 256Mbit = 32M b

SDRAM初始化:

1.200us的稳定期

2.L-Bank预充电

3.8个刷新

4.寄存器设置

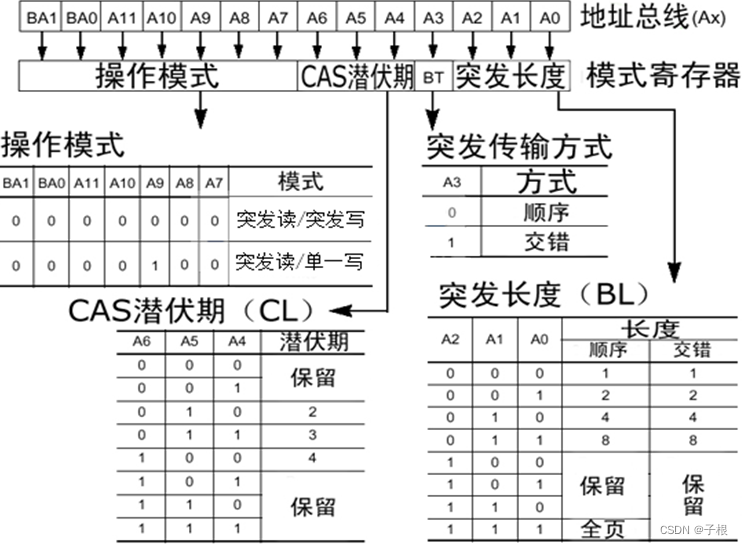

寄存器设置(MRS)

模式寄存器设置周期

(

tRSC

)

设置好寄存器需要等待一段时间

SDRAM读写:

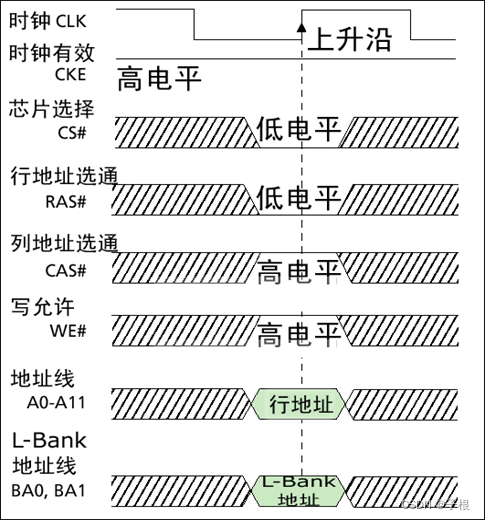

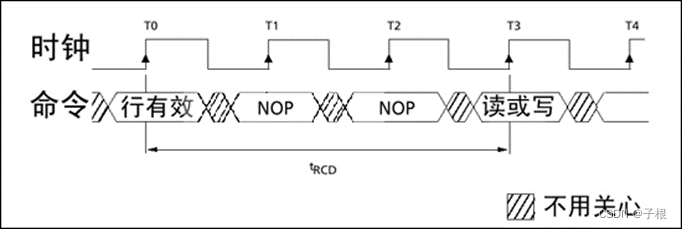

行激活:

CKE是高电平有效

#意为低电平有效

SDRAM

芯片的“片选”和

L-Bank

的“定址”与行激活同时进行

CKE: 1

CS#: 0

RAS#: 0

CAS#: 1

WE#: 1

A0-A11: 行地址

L_Bank: bank地址

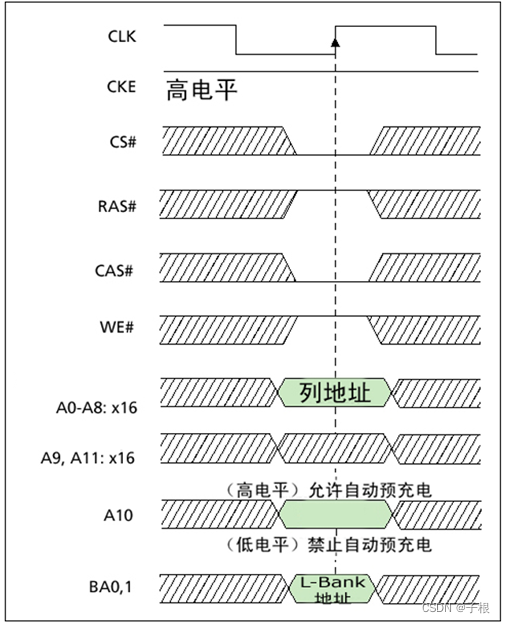

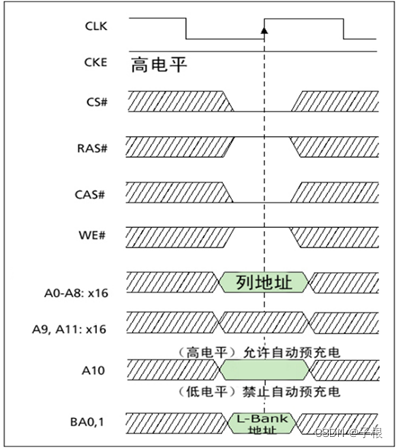

列读写:

CKE: 1

CS#: 0

RAS#: 1

CAS#: 0

WE#: 1

A0-A8: 列地址

L_Bank: bank地址

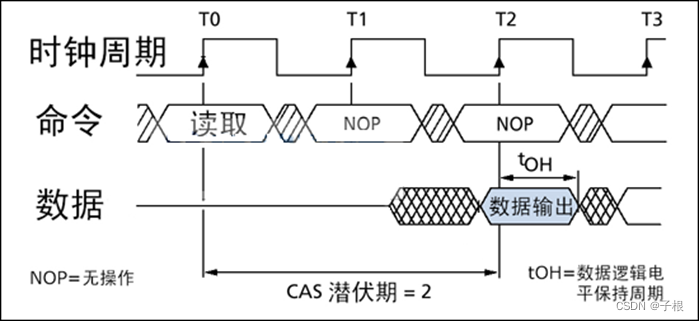

数据读出

列地址发出后,需要经过一段潜伏期才有数据输出

数据写出:

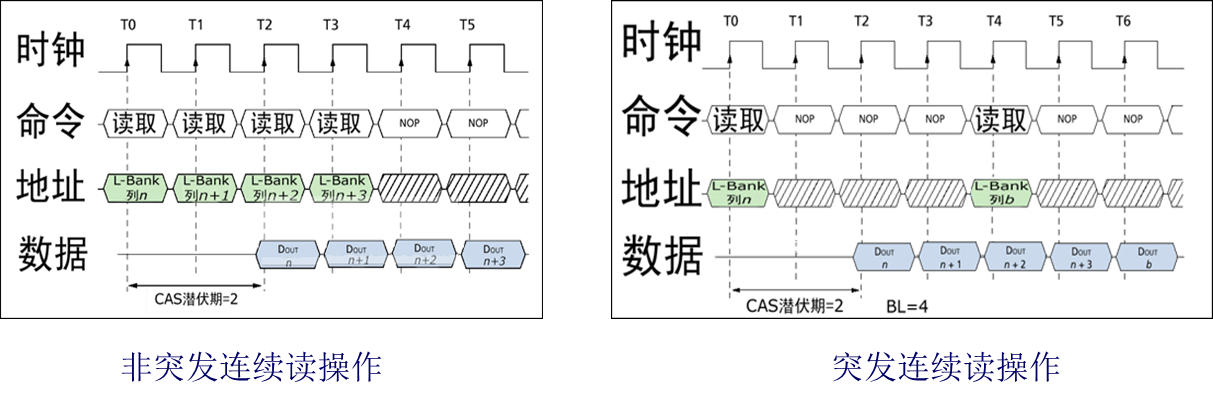

突发长度

突发(

Burst

)是指在同一行中相邻的存储单元连续进行数据传输的方式,连续传输所涉及到存储单元(列)的数量就是突发长度(

Burst Lengths

,简称

BL

)。

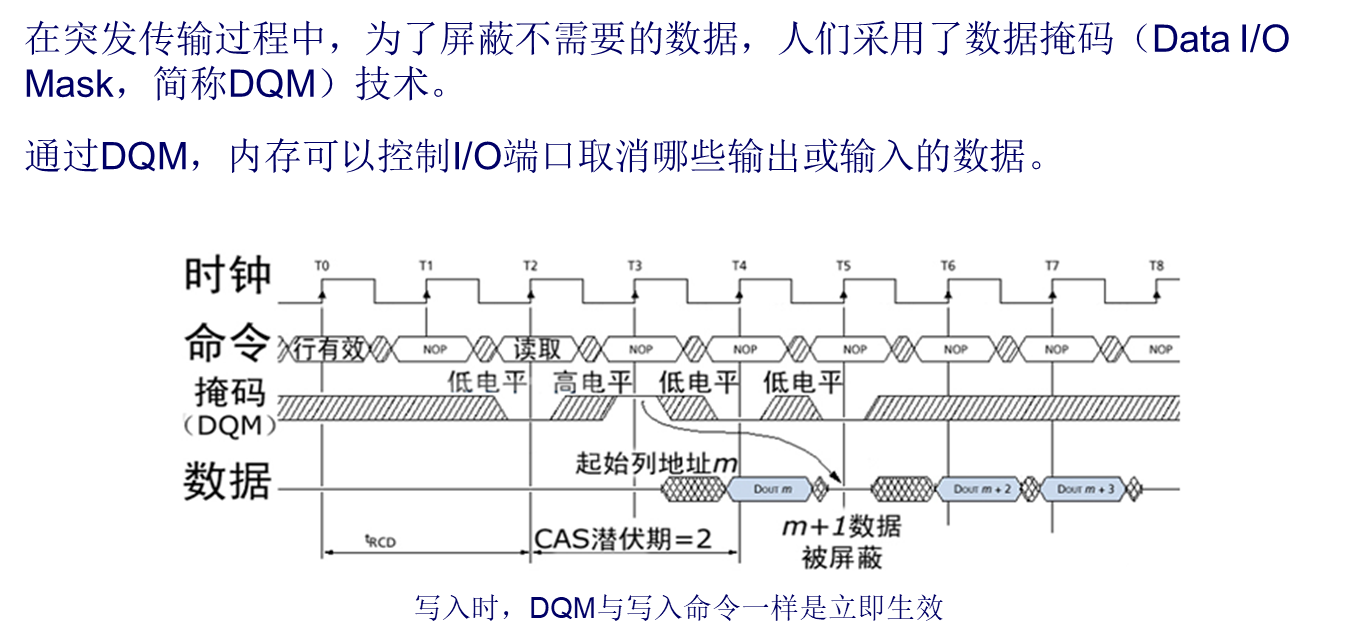

数据掩码

DQM高电平有效,一次只能屏蔽8位数据,

预充电:

关闭这行,打开下一行

刷新

SDRAM

之所以称为同步“动态”随机存储器,就是因为它要不断进行刷新(

Refresh

)才能保留住数据,因此刷新是

SDRAM

最重要的操作。

一般是至少60ms刷新一下,刷新主要是为了之前的行不掉电,不丢失数据