1、将工程移植位置后,结果报 Black Box问题。

例:[DRC INBB-3] Black Box Instances: Cell ‘xillybus_ins/system_i/vivado_system_i/xillyvga_0/inst/xillyvga_core_ins’ of type ‘xillyvga_core’ has undefined contents and is considered a black box. The contents of this cell must be defined for opt_design to complete successfully.

在网上查找,回答基本上都是手动添加一下ngc文件可解决问题,但我添加后依然报相同错误。

删除并重新配置该IP核解决问题。

2、仿真时出现多个模块25MHZ时钟信号一直为0的现象。

查看后发现之前调用pll锁相环时采用了默认设置的复位高电平有效,因为系统的复位信号是低电平有效,直接将系统复位信号连接到了锁相环上,导致了此现象。

3、VHDL 语言编写模块调用代码时应注意各个上层模块所调用的底层模块名称需要不同,否则更换某个底层模块时容易出现其他上层模块所调用的模块也被替换掉的现象。

4、VHDL 语言编写模块调用代码时应注意各个上层模块所调用的底层模块名称需要不同,否则在配置ILA上板调试环境中添加debug信号时容易出现设置多个重复debug信号的现象,导致系统资源不足。

5、[Opt 31-67] Problem:A LUT2 cell in the design is missing a connetion on input pin 10, which is used by the LUT equation. This pin has either been left unconneded in the design or the connedtion was removed due to the trimming of unused logic. The LUT cell name is: Inst_top_XXXAnst_XXX1Anst_ XXX_toplu3_XXfitorUOinst_fito_gen/gconwfitfo.r/grt.rtigntv_or_sync_fifo.gl0.wr/gwas.wsts/DEVICE_7SERIES.NO_BMM_INFO.SDP.WIDE_PRIM18.ram__2

此问题是由于某一处模块调用的输入信号为空导致的,需要给该输入信号赋给实际的输入可解决问题。

6、使用modelsim仿真时报错:

Error: hdl/XXXXX_top.vhd(1277): Type error resolving infix expression “+” as type ieee. std _logic_1164. std_logic vector.

此错误是缺少包含运算符的库导致的,加上相应的库即可解决。

7、使用simlation仿真时出现X未知数红色波形。

大概率表示该信号是多驱动。

8、使用modelsim仿真时点击 run all 时波形无变化。

原因可能是代码逻辑有问题。

9、使用ram读取数据后数据有一个小的延迟,若用分位宽的方式截取数据需要给ram读取的数据打一拍。

10、使用Vivado对工程实现时,当出现[DRC MDRV-1]多驱动报错时,错误位置不一定是其提示的那一个信号,要往上层模块或往下层模块中查找。

11、使用Xilinx的fifo IP核的空信号产生读使能信号后发现每一个读使能信号产生了两个时钟周期的高电平,导致同一个数据读取两遍,原因是该空信号本身在读空后和非空前之间必定有两个时钟周期。

后续对读使能信号采用了边沿信号,解决了此问题。记得打一拍让使能信号要与数据同步。

12、fifo IP核复位信号直接置0后,导致fifo IP核没有产生复位信号,fifo的满信号和空信号可能一开始都是高电平,导致无法产生写进infifo的写使能信号。

后续使fifo有一段时间的复位信号,可以正常实现功能。

13、综合时报错[Synth 8-3493]

例如:module not have matching formal for component port “full”[XXX_top.vhd]:326。

“full”仅输入,没有给任何逻辑。

对输入信号进行逻辑处理可解决问题。

14、综合时报错[DRC REQP-1712]

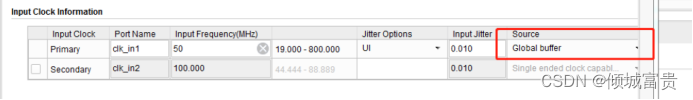

Input clock driver:Unsupported PLLE2_ADV connectivity.

PLL IP核设置出现问题。因为从代码里可以看到我的PLL的输入信号clk是来自IBUFGDS的输出信号clk,而不是来自普通的单端时钟信号。虽然我的IBUFGDS已经把差分时钟变成了单端时钟,但是它仍然不是普通的单端时钟信号,因此需要修改PLL的clk_in的source参数。

将PLL的clk_in的source参数修改为Global buffer即可。原因就是上面所说的,clk_in端口的信号不是来自一般的单端时钟信号,也不是直接来自差分时钟信号,而是来自IBUFGDS。

新问题:锁相环产生的时钟被优化掉了。

解决:有可能设置debug会自动将时钟添加到全局时钟域中,将PLL设置恢复并重新设置debug后锁相环产生的时钟正常了。

15、综合时报错:[Synth 8-549] port width mismatch for port‘addra’:port width = 8, actual width = 9[XXX_top.vhd:60]

端口数据位宽对应不上,查看得知该ip核设置参数不正确。

修改数据位宽后解决问题。

16、实现时报错[Place 30-389]IO port“XXX”does not have an associated IO buffer driver or load.Check port connection to a vaild IO buffer.

发现是BUFG不够用。

暂时以去除XDC文件中的debug约束的方式以减少BUFG的使用。

17、Vivado使用 Debug 标记创建 ILA 调试环境并将程序下载到FPGA板子后,Vivado显示There are no debug cores。ILA无法正常启用。

ILA的输入时钟信号不正常,时钟应为差分时钟信号,但未经过差分转单端操作,直接输入给ILA,导致ILA也无法正常工作。

在代码里使用IBUFDS原语将差分时钟信号CLK_P和CLK_N转化为单端的CLK_IN。

18、在配置波形仿真时报错[USF-XSim-62]‘compile step failed with errors(s).Please check the Tcl console output or ‘D:XXXX/XXXX.sim/sim_1/behav/xsim/xvhdl.log’for more information.

根据提示打开xvhdl.log文件发现是多个顶层信号未声明,对其进行声明后解决问题。

19、跨时钟域处理中快时钟域到慢时钟域时,由于快时钟域中窄脉冲的有效脉冲宽度小于慢时钟时钟周期,使用慢时钟域直接去采集这种窄脉冲信号,有可能会采集不到。

可以采用“快时钟域脉冲扩展+慢时钟域延迟打拍”的方法进行同步。