1. 前言

从FPGA的设计,仿真,综合,布局布线,嵌入式开发,烧录固化过程中的一系列文件后缀

2. 设计

- .v 最基本的Verilog设计文件

- .hdl VHDL设计文件

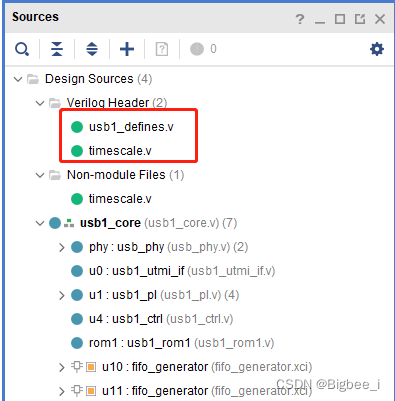

很多主流设计会定义一个.v文件专门用来define一些全局的参数,方便进行移植。

3. 仿真

-

不同版本的vivado适配的第三方仿真工具和版本都存在差异,可以参考如下博客:

各个版本Vivado适配的第三方仿真软件

-

大部分场合使用Modelsim与Vivado进行联合仿真,可以参考博客:

FPGA学习之路—Vivado与Modelsim联合仿真

3.1 Xcelium parallel simulator

官方文档:

Xcelium Parallel Simulator

4. 综合

4.1 Vivado

- .xdc 约束文件,可以约束时钟和管脚,设置延时驱动模式等。

- .ucf 约束文件,在ISE14.7时代被广泛使用,vivado兼容

通常情况下,我并不会自己编写.xdc文件,而是使用vivado的图形工具,管脚约束在IO Port中,压缩在setting中设置。

可以参考这篇博客:

FPGA Vivado XDC 约束文件编写方式语法笔记

4.2 Synplify

- .prj 工程文件,以tcl格式保存

- .fdc 约束文件

- .ssr Synplify综合完成后的日志文件

深入了解可以参考我的一片汇总:

Synplify参考资料整理

5. 布局布线

待了解

6. 嵌入式开发

- .c ps端开发,.c为设计文件;

- .h ps端开发,定义包含声明一般都放head文件中;

- .fsbl 引导文件,ZYNQ开发时,需要从PS端引导启动,然后再将PL端的数据流加载;

- .elf MicroBlaze和ZYNQ开发时,生成的可执行文件,用来完成逻辑的文件。

7. 烧录固化

几种文件的差异:

FPGA中可执行文件:bit/bin/mcs/elf

7.1 烧录:断电易失

- .bit bit流文件,包含PL端的所有信息,烧录通常是一次性的,断电就会消失

- .ltx 在添加ila ip后,进行在线调试时,会要求将ltx文件一同烧录进去

vivado中,以上两文件默认保存在如下路径下

"D:\工程目录\工程名.runs\impl_1"

7.2 固化:不易失

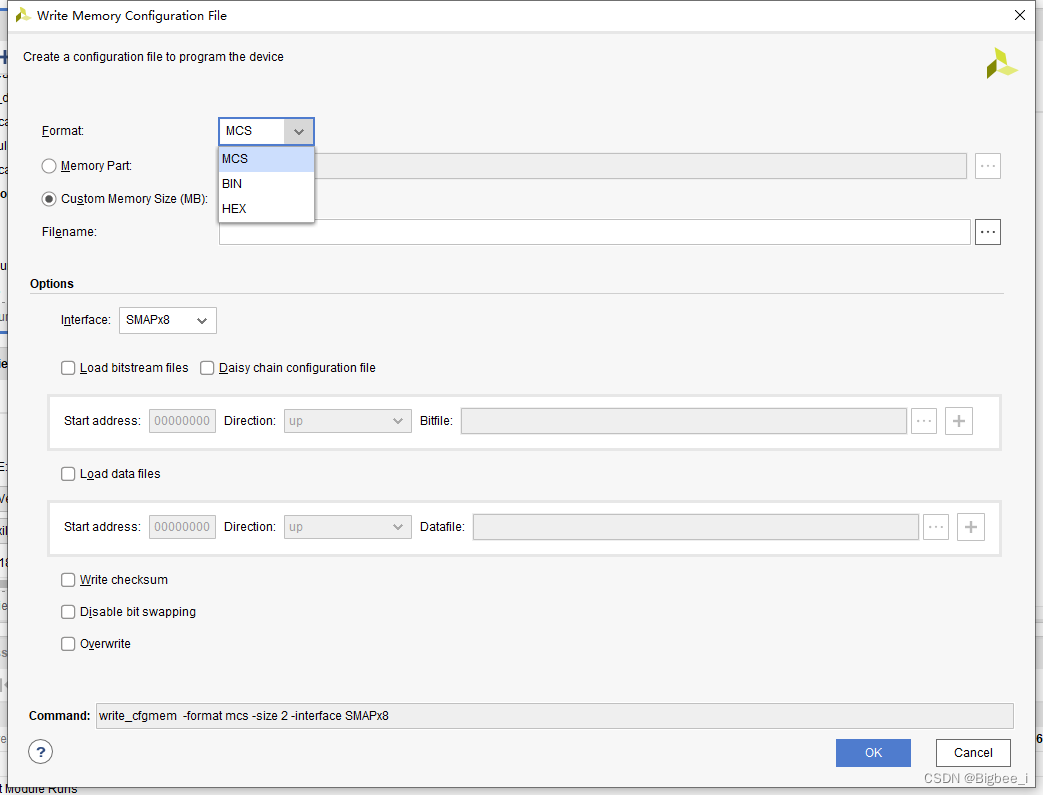

- .bin 二进制文件,由bit文件生成而来,必须被烧录到Flash中,上电后自动对FPGA进行初始化

- .mcs ASCII文件格式,也是由bit文件生成,但是在固化时还有一个.pxx文件,在生成mcs文件时会自动生成

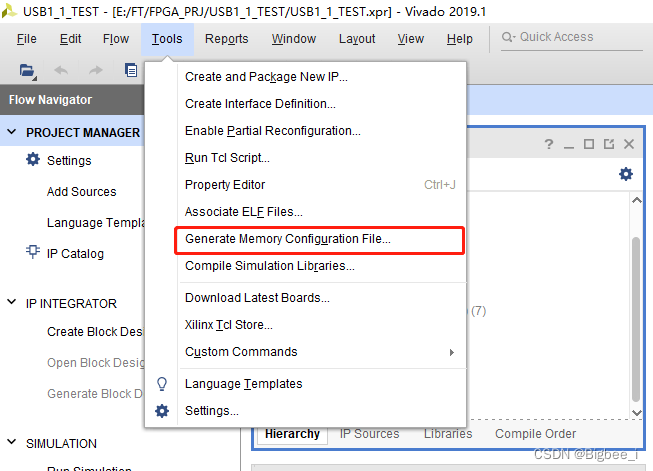

bin文件和mcs文件的生成我常常在tools-> Generate Memory Configuration File中生成。

版权声明:本文为liuhandd原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接和本声明。