FPGA学习-vivado软件的使用

1.杂谈

又被封了7天。

正好封控前领导让我改下fpga代码,趁这个机会好好学习下,虽然在这块一片空白,但是毕竟这块是我的短板,一个不会写代码的硬件工程师是一个不完整的硬件工程师。

我很喜欢体验新鲜事物,我发现体验的多了,就会发现一切都没那么难,恐惧是因为你不了解它。

所以即使不会,那又怎样,去做,时间久了你就会。要是不做,你每次碰到类似问题就会觉得,好高深莫测,其实,去了解会发现,不过如此。

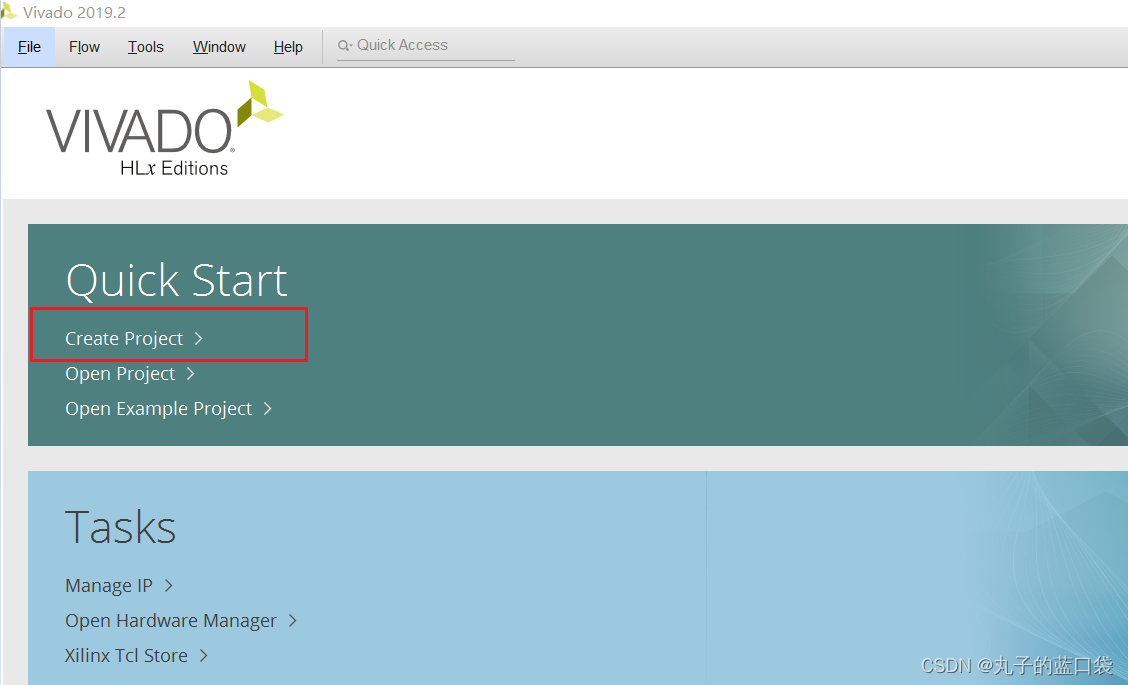

2. vivado新建工程

vivado是xlinx的集成开发环境,用来进行xlinx的fpga开发。

1.创建工程

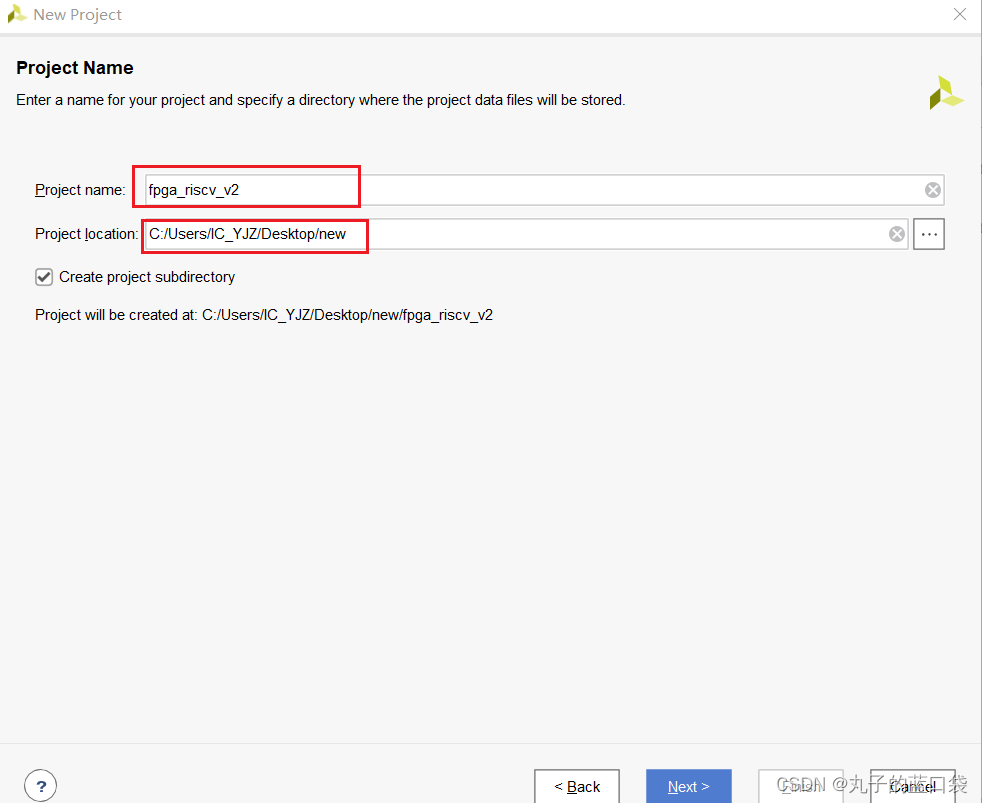

进行工程命名,next

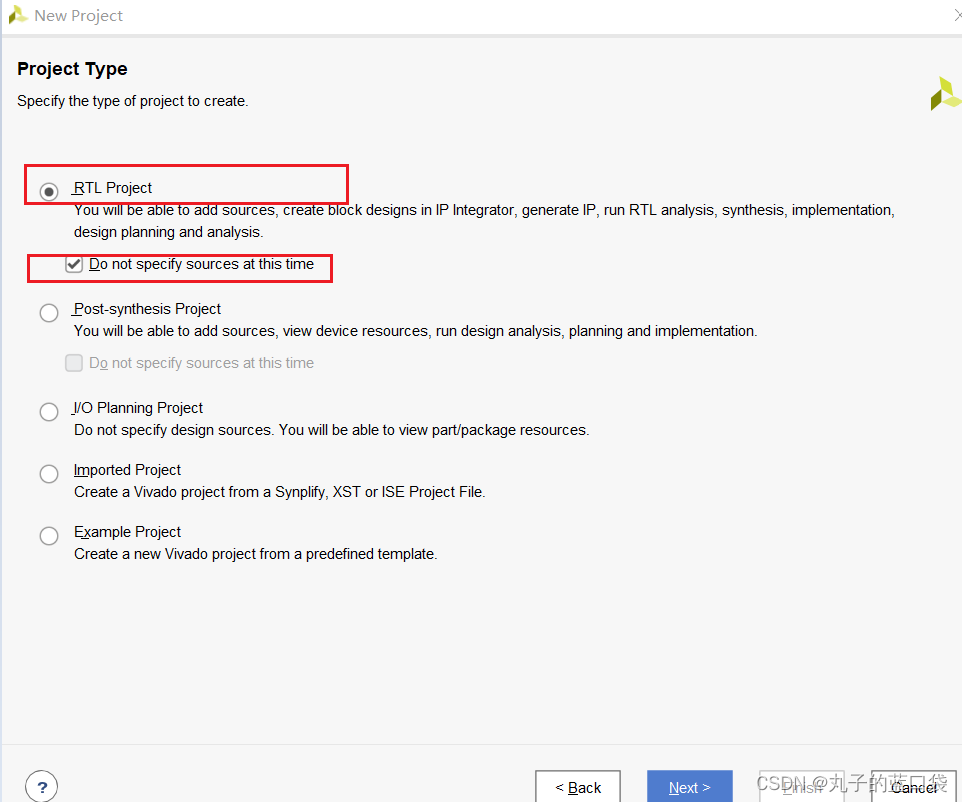

选择RTL(Register Transfer Level, 寄存器传输级)工程,并且勾选do not specify sources at this time,这次先不指定源文件。

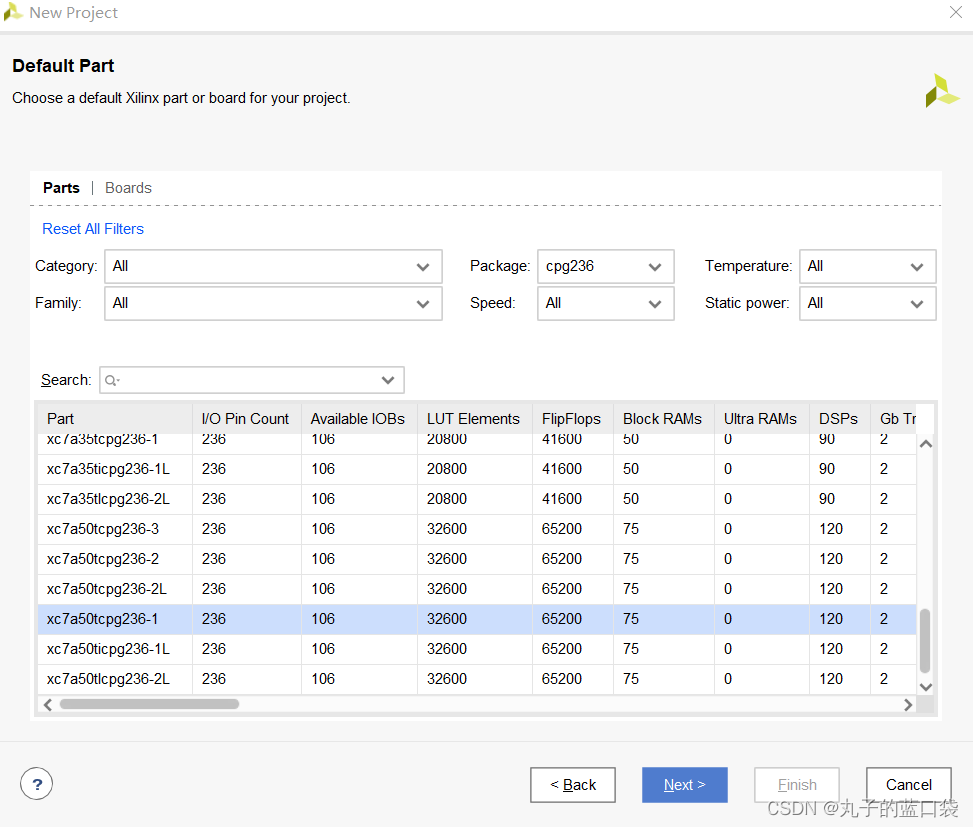

选择器件,next

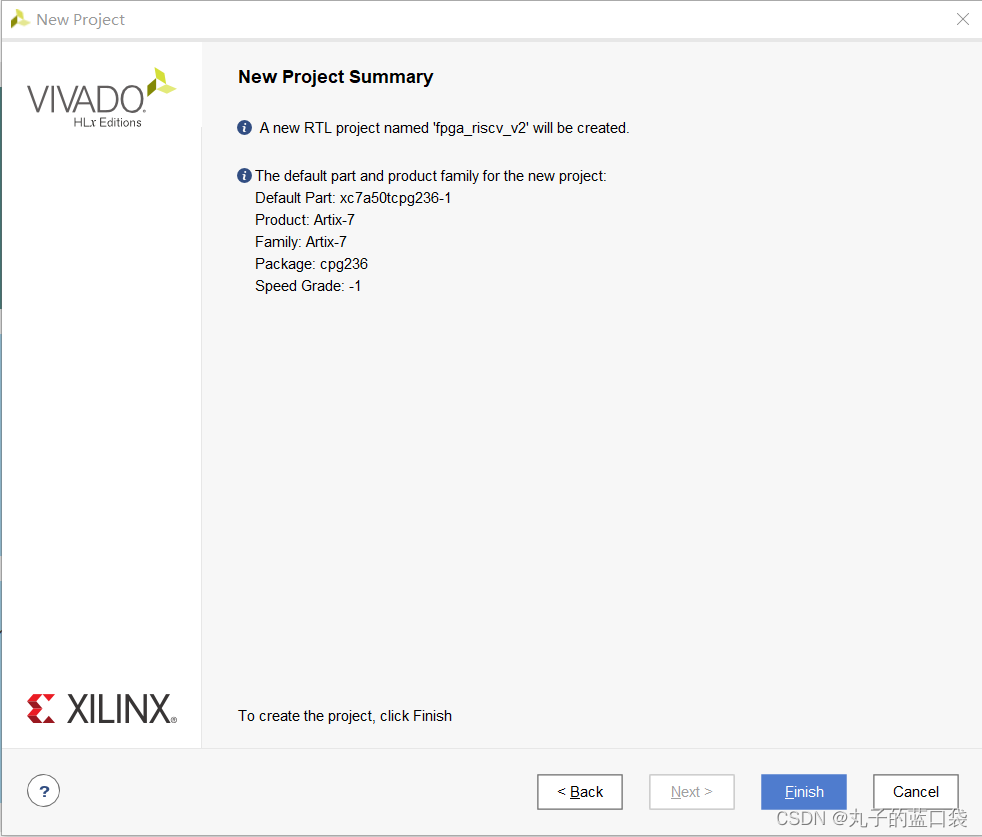

最后是新工程的总结,finish

2. 建立源文件

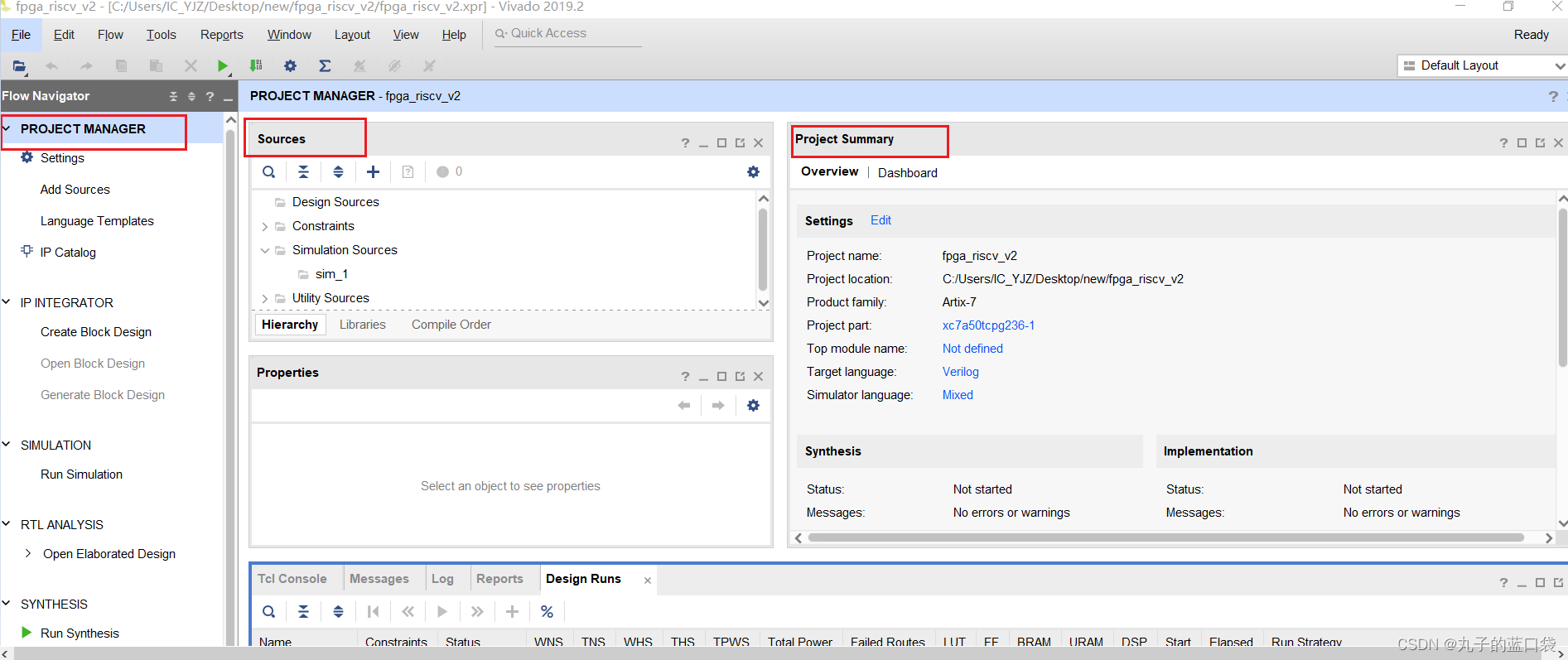

进入工程界面后,分成了工程管理、源文件管理、工程总结等几个部分。

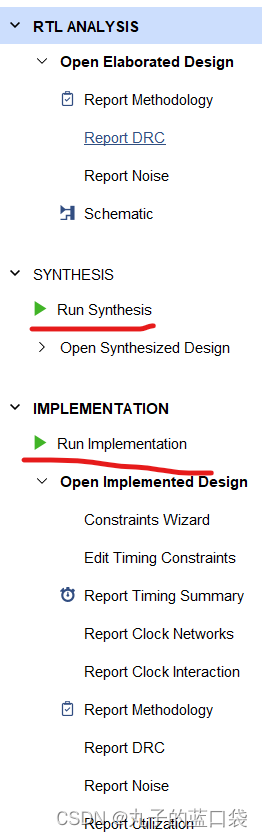

project manager中包括仿真、RTL分析、综合、实现、生成比特流的过程。

综合是将verilog代码变成fpga基本单元如ram,lut等。

实现是将基本单元进行布局布线。

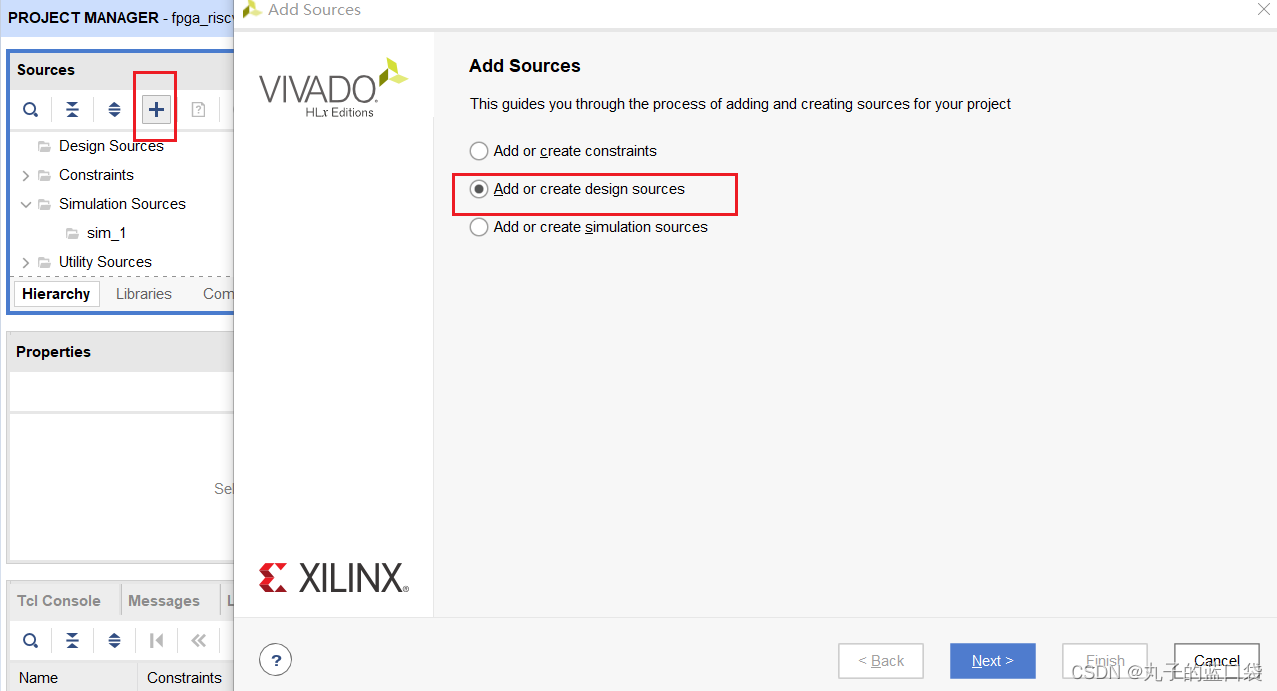

1)新建源文件

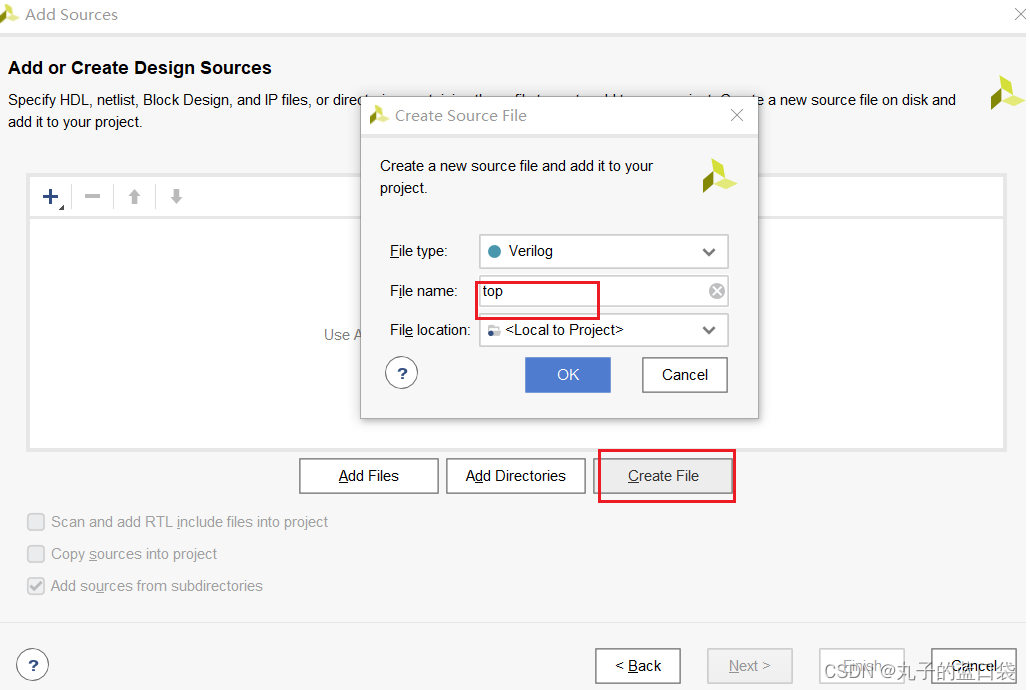

next,进行命名

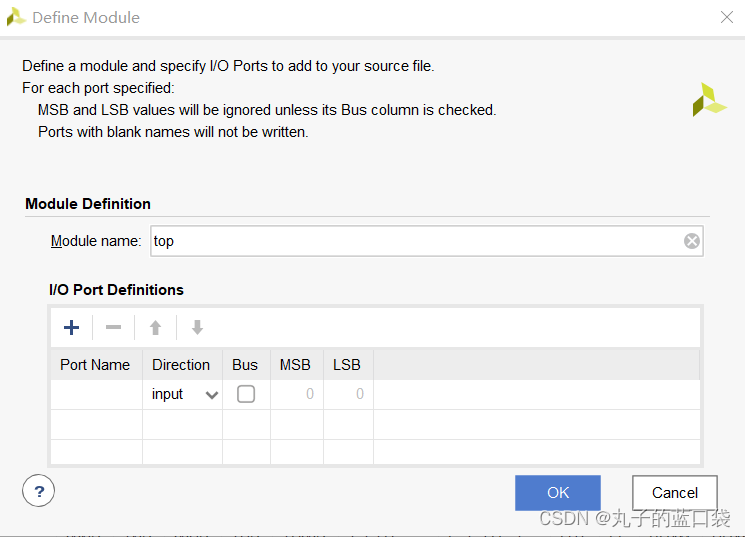

ok,finish后,对top.v里的模块进行命名,保持与源文件名一致就行。

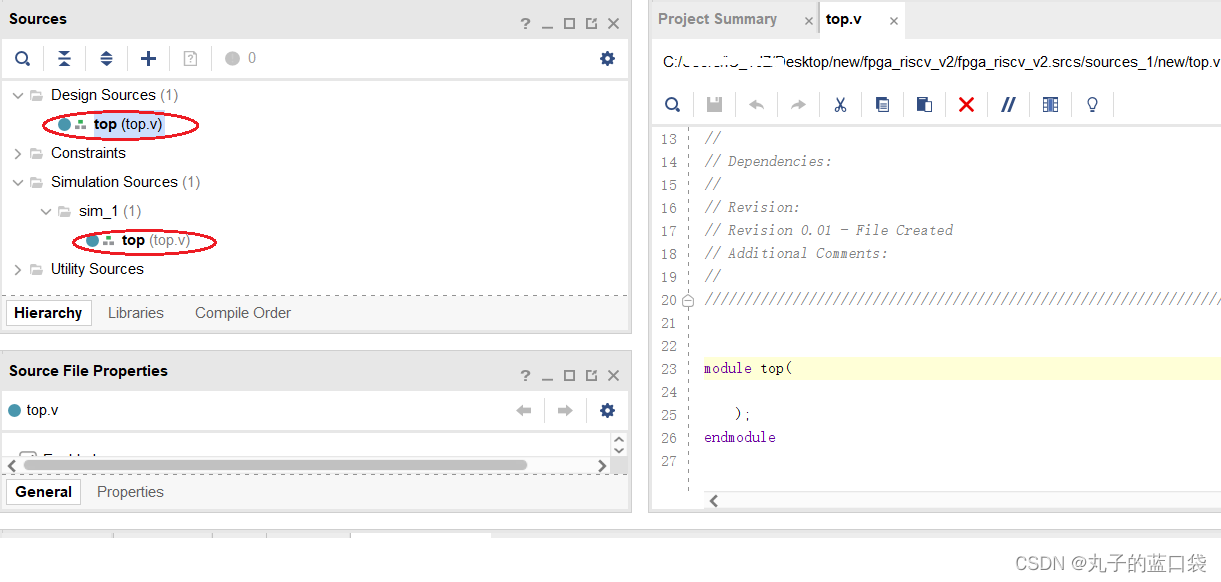

ok后可以看到design source和simulation source都出现了top.v文件。

2)建立仿真源文件

仿真文件是必要的,为了仿真你设计文件是否是自己想要的结果。

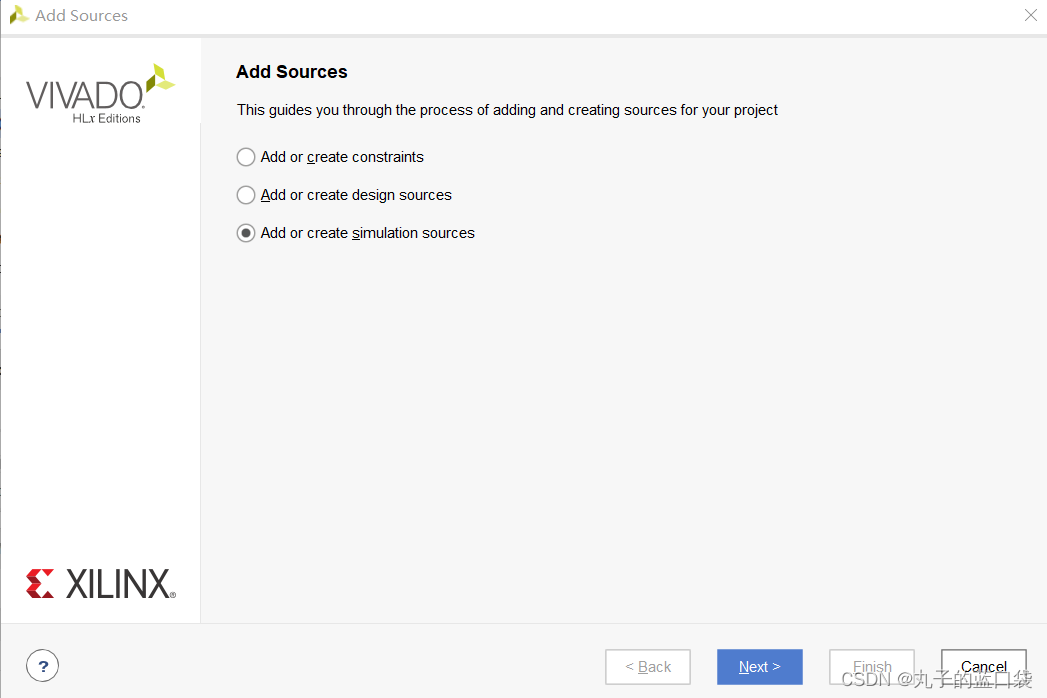

将上面add sources的类型改为simulation source。

同样进行源文件和模块命名,可以看到仿真文件只在仿真源文件里出现。

编写源文件后,进行综合和实现,可以从schematic看看是不是你想要实验的功能

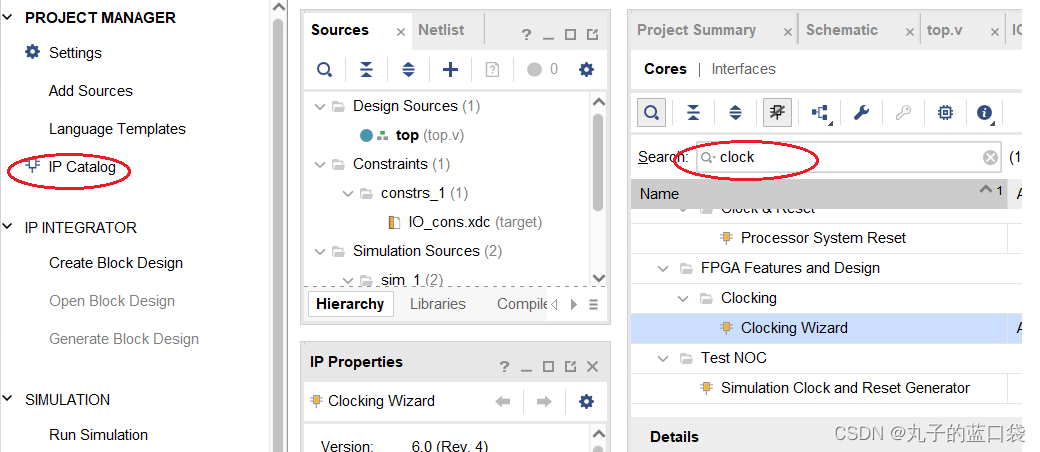

3)调用IP

若要添加时钟PLL,可以选择IP catalog里 clock wizard

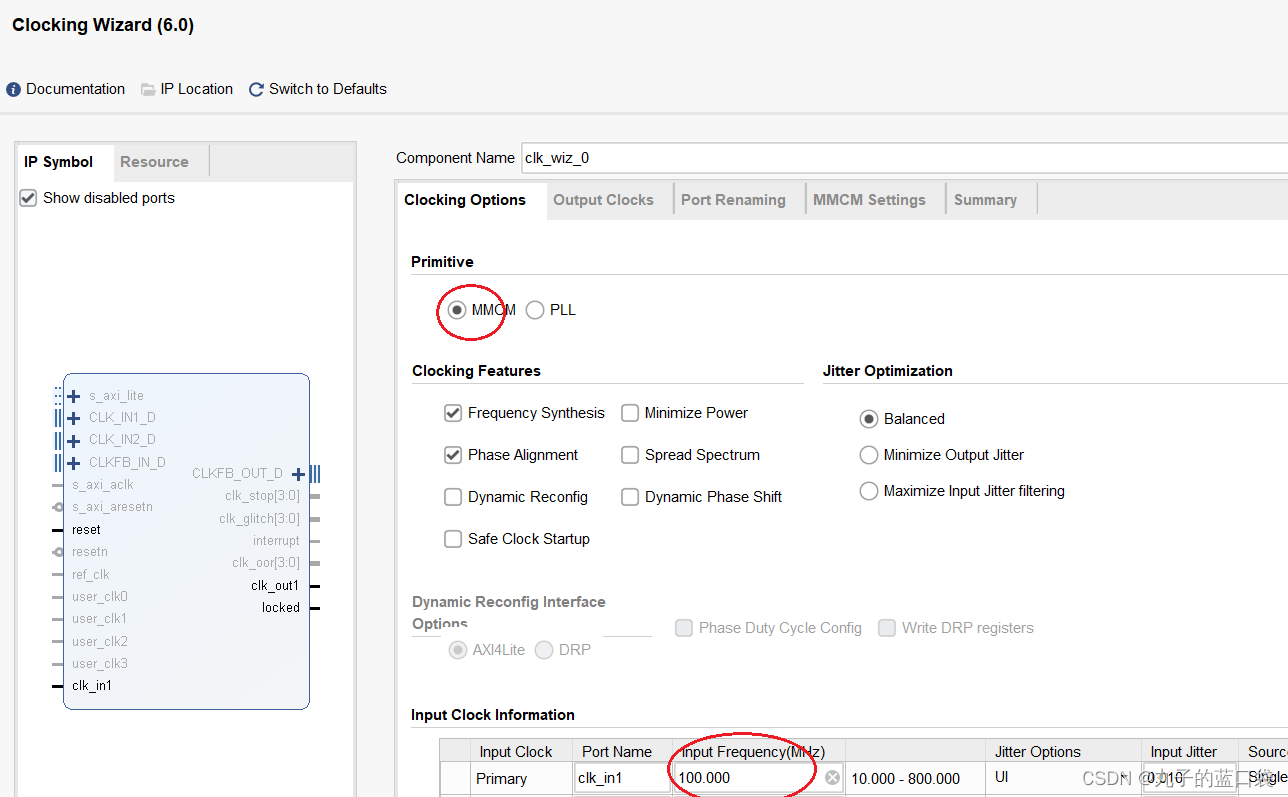

选择混合模式时钟管理器(MMCM),相对于PLL,更灵活。设置输入时钟。

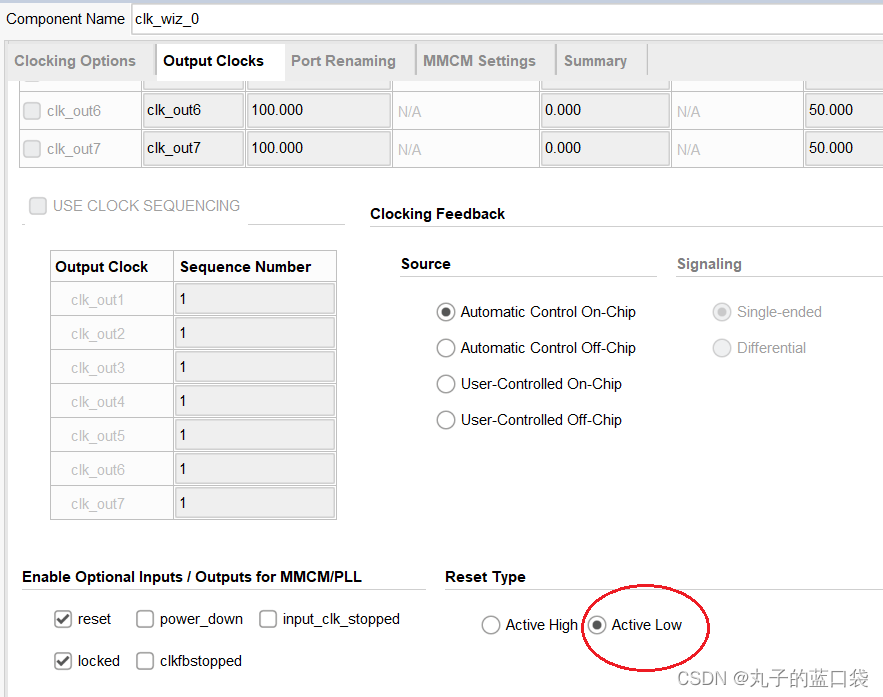

在output clocks里设置输出时钟,reset type选择active low

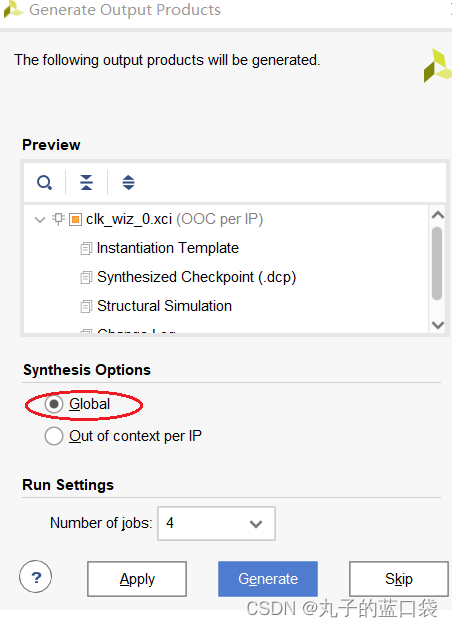

ok后,可以选择global全局综合,而out of context per IP模式被称为OOC模式,在生成综合IP核时,已经将IP核综合为网表文件和IP调用文件,在后续整个工程实现时,不再对IP核的源文件进行综合实现,而是直接将网表与其他模块一起实现。

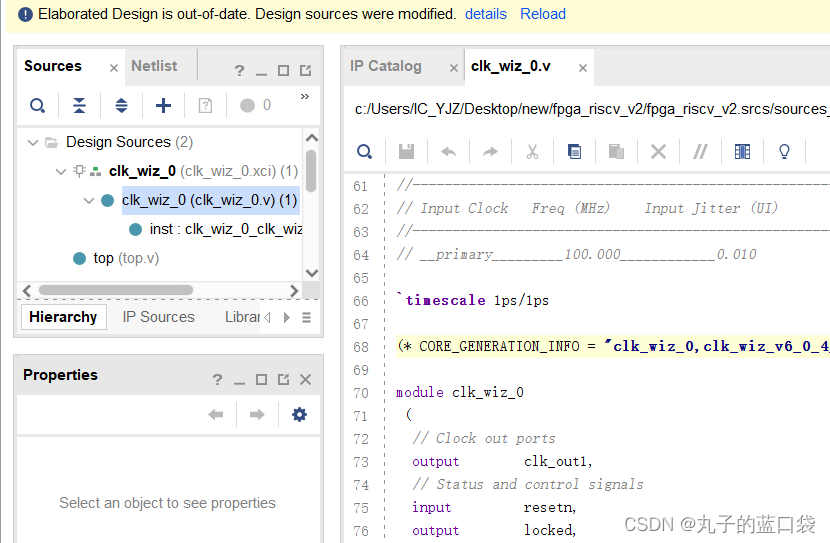

generate后可以看到时钟配置的源文件。

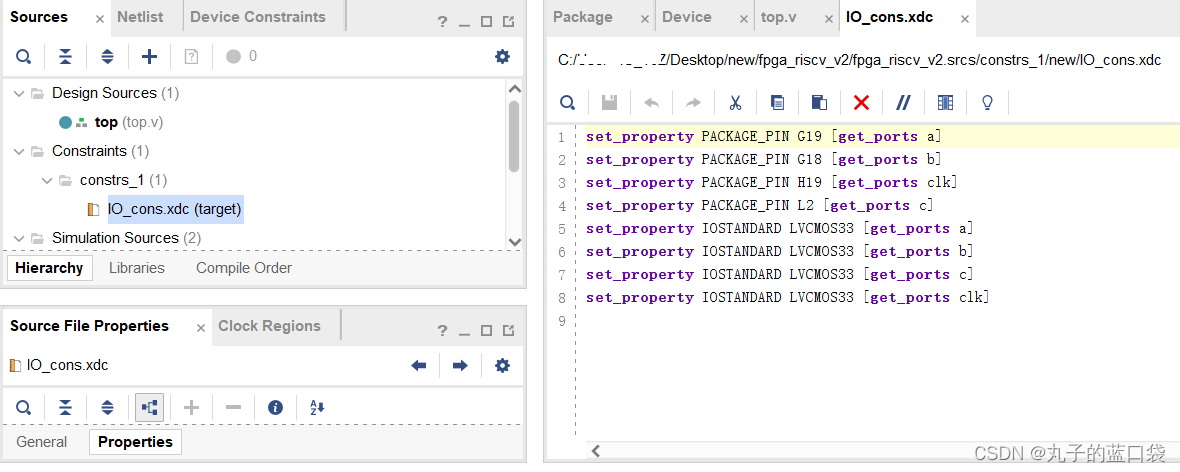

3.添加IO约束

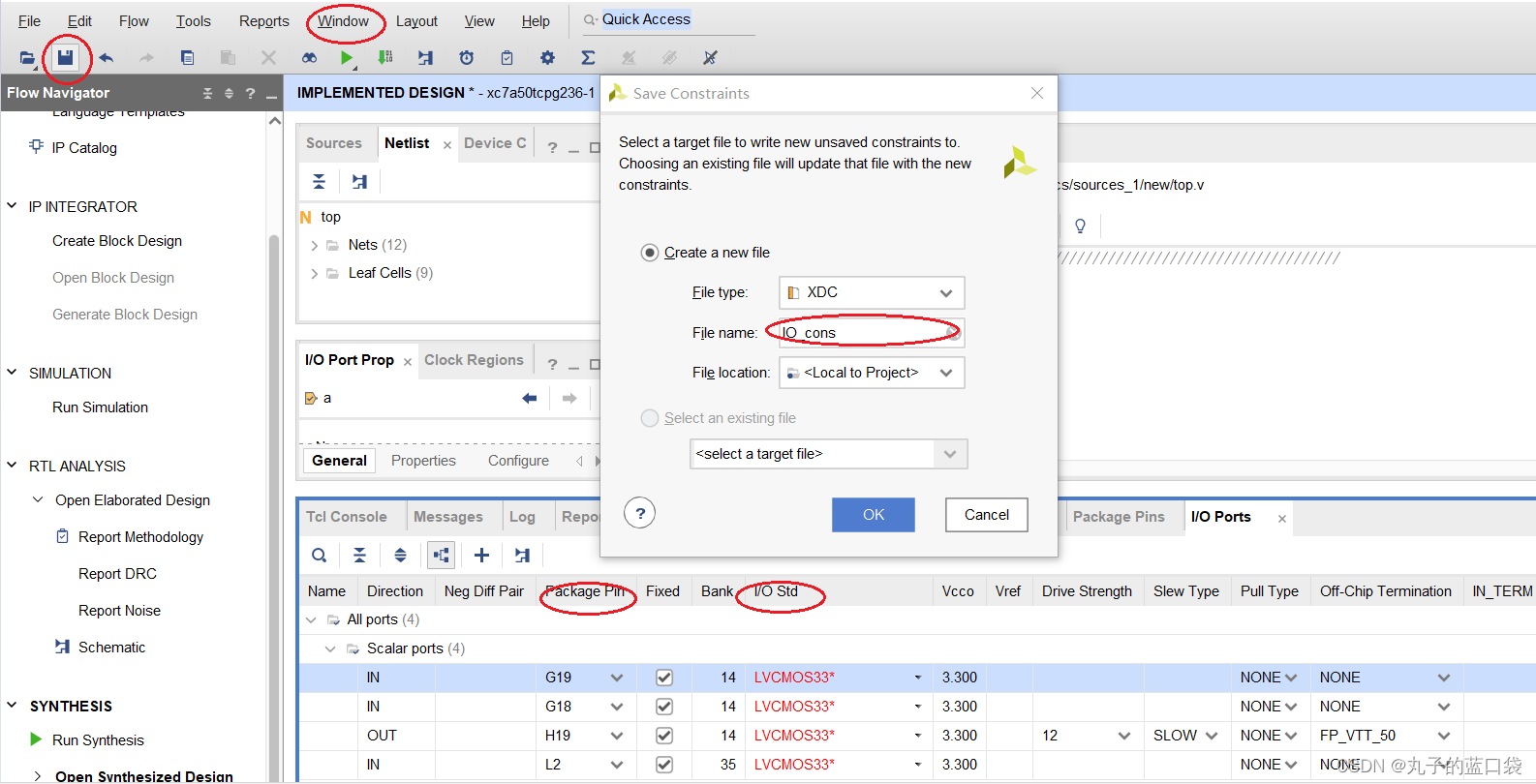

在window-IO ports中进入IO 配置页面,配置package pin封装引脚、IO std -io的电平标准。ports中其他项是自动出现,drive strengh驱动强度,默认12mA,slew type上升下降沿的快慢,默认slow,off-chip terminnation 终端阻抗,默认50Ω

点击save,进行约束文件命名,ok后,会出现约束文件。

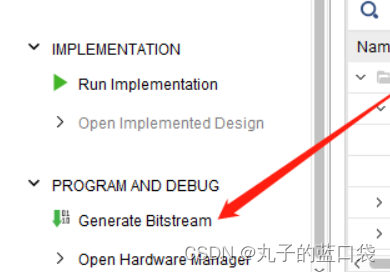

4.生成bit流

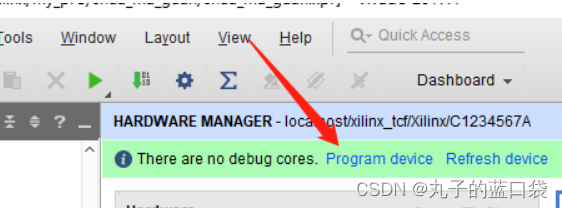

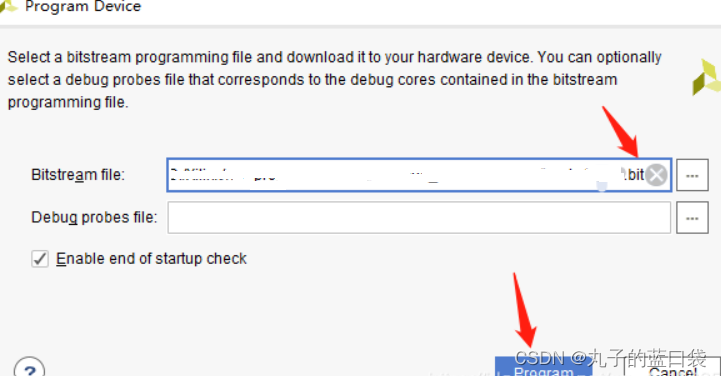

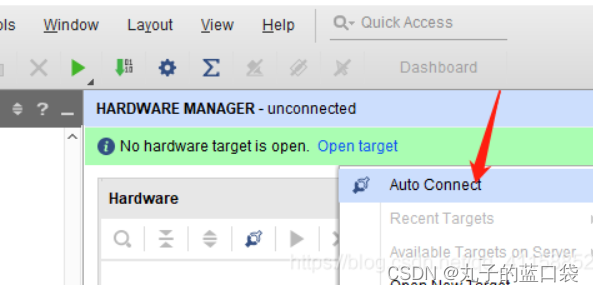

5.连接板子上的fpga

6.下载bit流