备注:本文转载自以下博主,这里仅在原有基础上优化了一些语句通畅性问题,以便于更好的学习:https://blog.csdn.net/weixin_37879993/article/details/80802974

目录

一、 Cadence Allegro PCB SI 简介

1、高速 PCB 设计流程

二、 Allegro PCB SI 仿真

1、准备仿真模型和其他需求

1.1 、获取所使用元器件的仿真模型

( 1 ) 通过官网,供应商等渠道获取 IBIS 模型

( 2 ) IBIS 模型转化为 DML 模型

( 3 ) 通过 Allegro 建立简单 DML 模型以及模型分配

( 4 ) 通过 Allegro 建立复杂 DML 模型以及模型分配

1.2、了解 PCB 的布线规则以及原理图部分逻辑

2、仿真配置

2.1、使用 SI Design Setup 配置

2.2、选择需要配置的信号线

2.3、设置仿真库

2.4、设置电源和地网络

2.5、设置叠层

2.6、设置元器件类别

2.7、为元器件分配和创建模型

2.8、设置差分对

2.9、设置仿真参数

2.10、SI Design Audit 相关

2.11、提取拓扑

3、后仿真报告结果验证

3.1、信号波形

3.2、反射报告,延时报告以及同步噪声报告

一、 Cadence Allegro PCB SI 简介

1、高速 PCB 设计流程

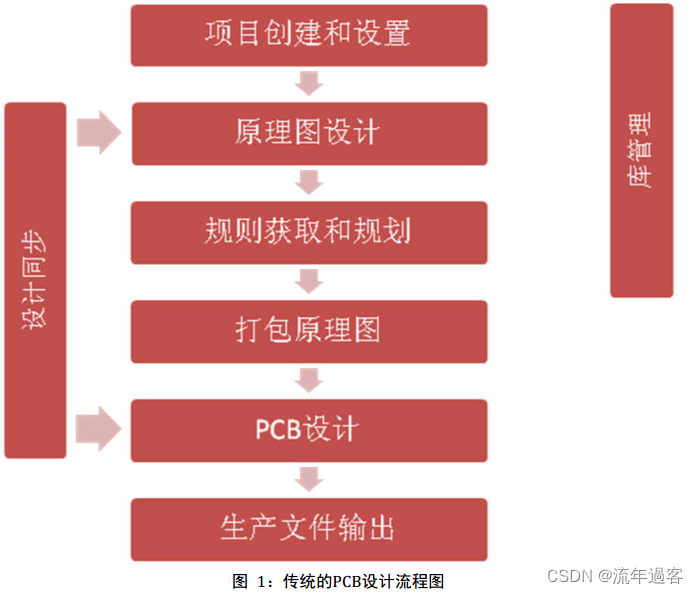

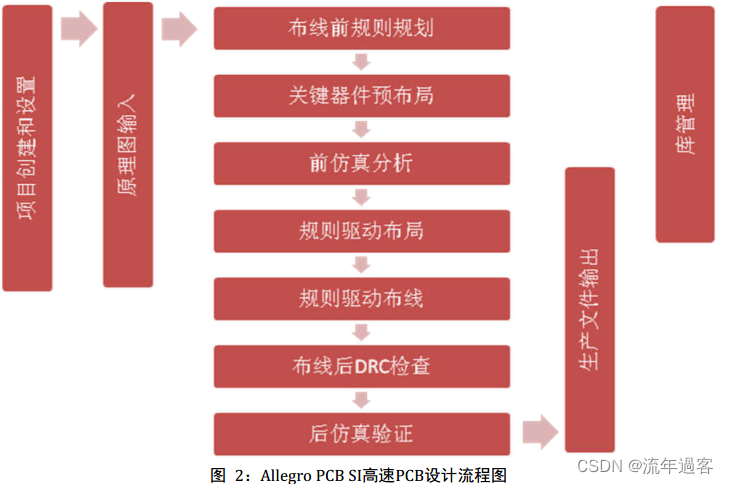

传统的PCB设计流程如下图所示:

而引入的Allegro PCB SI仿真工具后的设计流程改进为:

二、Allegro PCB SI仿真

后仿真,是在PCB布线完成以后,对已经完成的关键网络进行仿真验证的过程。可以检查实际的物理执行过程(布局布线)是否违背设计意图;或是已知的改动,通过仿真来验证这种改动给高速设计带来的影响。

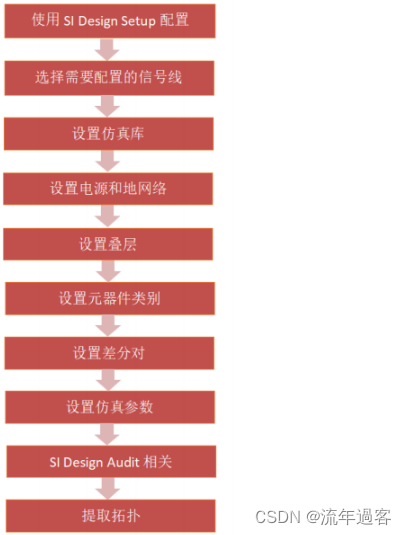

使用Allegro PCB SI进行后仿真的基本流程如下:

1、准备仿真模型和其他需求

下面,以一个实际的电路板为例,介绍后仿真在Allegro PCB SI 16.6中的具体执行过程。

案例电路板:TX2P_P0_20171225,对其HDMI的差分信号进行延时以及反射分析。

1.1. 获取所使用元器件的仿真模型

(1)通过官网,供应商等渠道获取IBIS模型

http://www.analog.com/cn/design-center/simulation-models/ibis-models.html

(2)IBIS模型转化为DML模型

信号完整性仿真大多针对由芯片IO、传输线以及可能存在的接插件和分立元件所构成的信号网络系统,为

了实现精确的仿真,仿真模型的精确性是首先需要保证的。一般情况下,Allegro PCB SI会执行传输线和分立元件的建模,而芯片IO和连接器的模型通常会由原厂提供。

当前业内常见的芯片IO模型有两种格式,IBIS模型和HSPICE模型;常见的连接器模型也是两种,SPICE

(HSPICE)模型和S参数模型。Allegro PCB SI支持包括上述四种在业界流行的仿真模型,但一般都需要

转化为Cadence自己的DML(Device Modeling Library)后才能使用。

Allegro PCB SI在仿真时需要将仿真模型都转变成DML模型格式这一做法,区别于大多数EDA软件,这种

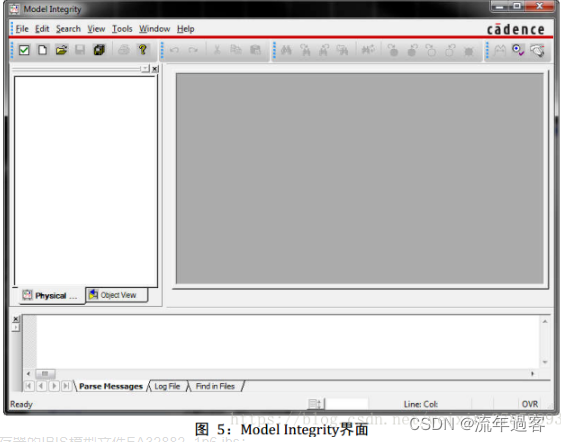

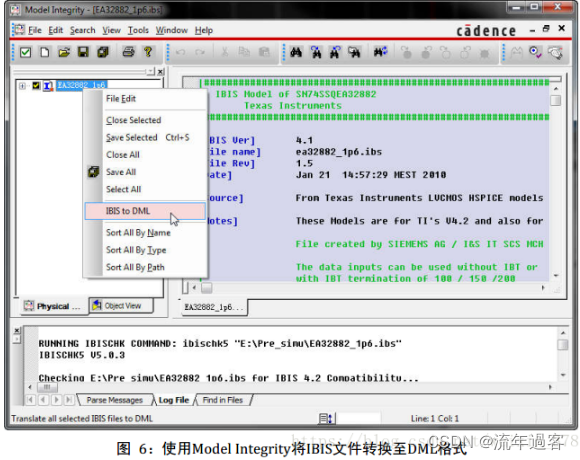

做法有利于仿真库的管理,做到仿真库和原始模型文件的隔离,并且在文件格式转换的同时也执行了模型的校验。大多数情况下,外部模型格式到Cadence DML模型格式的转换还是非常方便的,只需要用Cadence SPB系列工具包中的Model Integrity软件打开模型文件,然后点击转换到DML即可。

可以有两种方法处理:

其一,在Model Integrity界面下或Allegro PCB SI界面下将IBIS模型转换成DML格式,供之后的仿真调用;

其二,从Cadence SPB 16.5版本开始,Allegro PCB SI名义上也直接支持IBIS模型,所以可以保留现有的

IBIS文件不做转换,然后在之后的仿真中直接调用。之所以说是“名义上”,因为事实上Allegro PCB SI

还是执行了转换,只是这个转换的过程在分配模型的同时一起执行了,没有摆在明面上。

a、打开Model Integrity软件,如下图所示:

b、点击File->Open打开寄存器的IBIS模型文件EA32882_1p6.ibs;

c、右键点击浏览栏中的EA32882_1p6,选择IBIS to DML;

d、转换得到的同名DML模型会显示在Model Integrity窗口中,同名文件也出现在IBIS文件同一目录下。

(3)通过Allegro建立简单DML模型以及模型分配

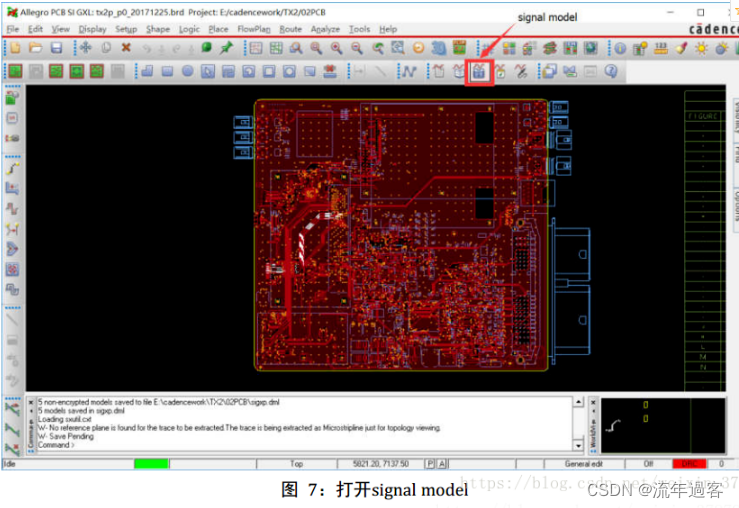

如图7所示,单击signal mode:

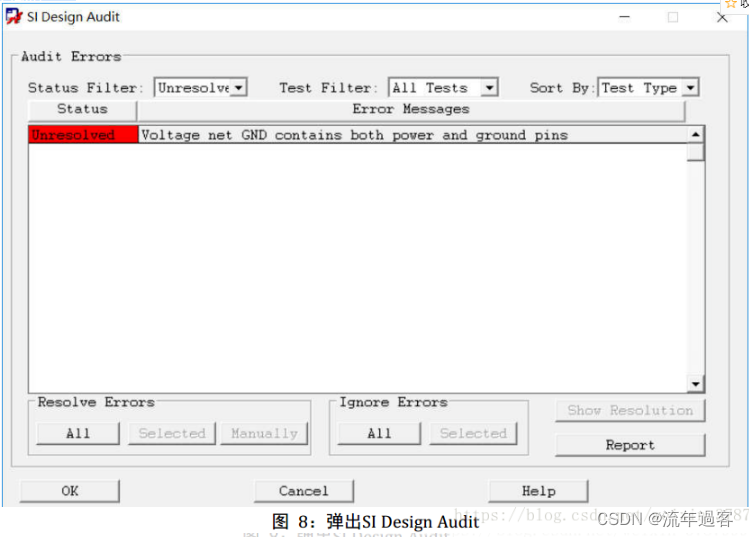

弹出如下图8所示:

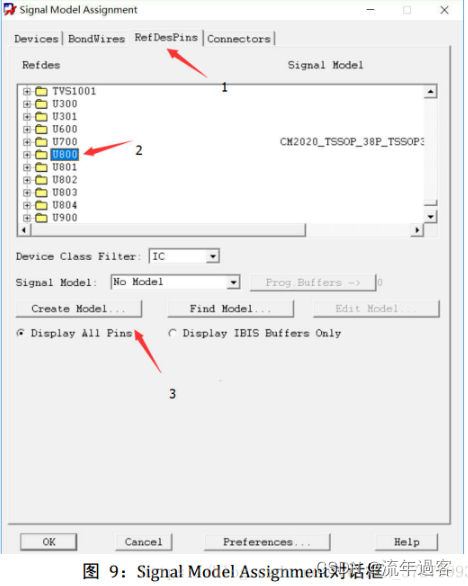

忽略error,点击OK即可,出现如下图9所示:

首先选择1: RefDesPins(元器件引脚),接着选择2: U800(所要建立模型的元件),然后单击3 : Creat Model,出现如下图10所示:

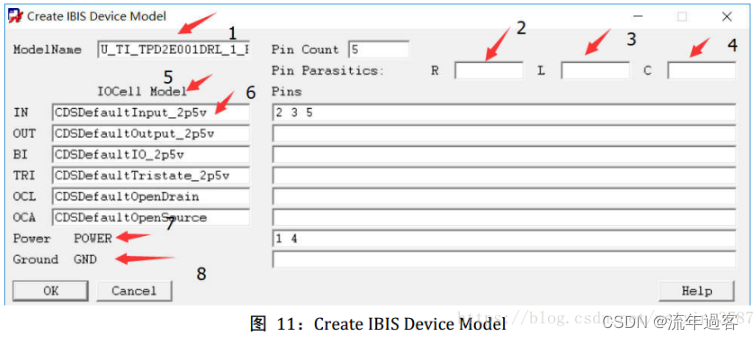

注意这里建立的是IBIS模型,选择create ibisdevice model,单击OK即可接着出现如下窗口,图11:

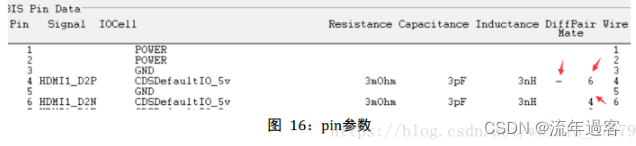

1:模型名称,2,3,4:模型pin脚寄生电阻,寄生电感,寄生电容

5:IO内部模型类型 6:IO内部模型,图中为2.05V,可以更改

7:POWER供电输入 8:GND

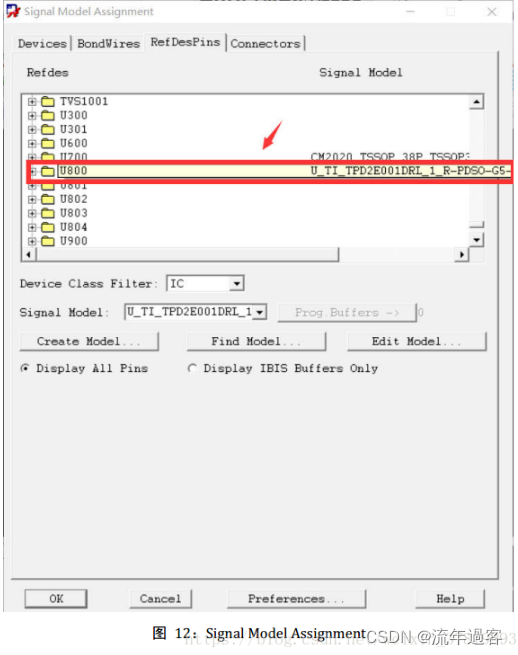

根据datasheet设置好参数后点击OK即可。如图12,可以看到U800已经分配刚刚新建的模型:

(4)通过Allegro建立复杂DML模型以及模型分配

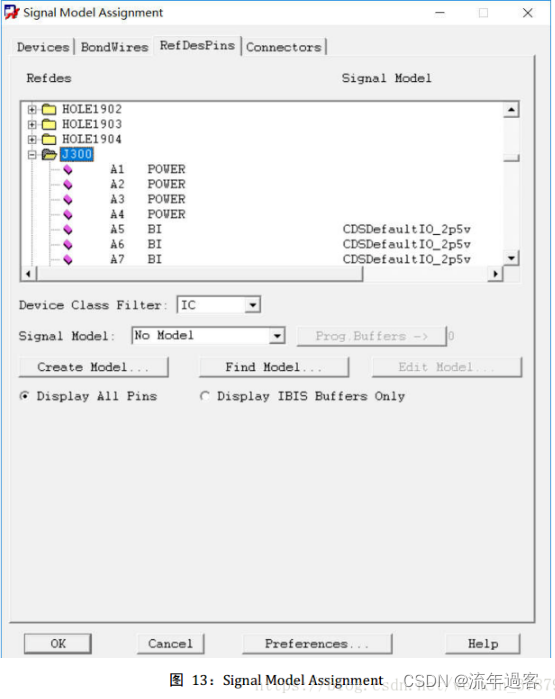

以上在pin数较少时建IBIS模型方法,如有差分线等复杂情况则如下图13所示:

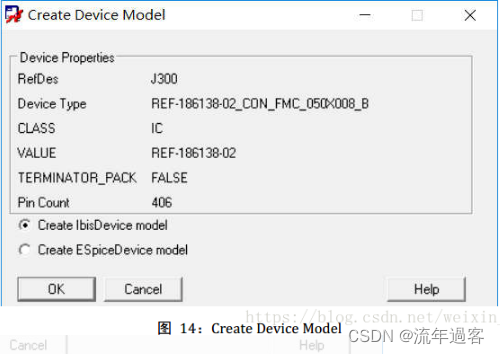

点击OK弹出如下图14所示:

点击OK弹出如下图15,共有406个PIN:

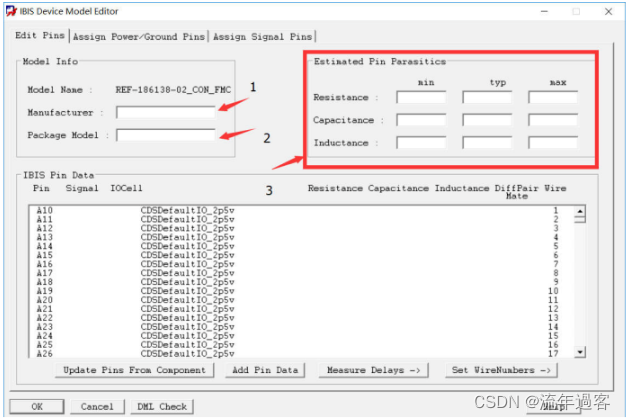

1:制造商;2:封装模型;3:寄生电阻/电感/电容;

将这些参数填好后,单击需要设置差分的网络,如下图17所示:

2:信号网络名;3:PIN电阻;4:PIN电容;5:PIN电感;

6:设置差分线的类型是正相输入还是反相输入,还是空;右侧的Mate PIN是与此PIN互为差分对的PIN号。

设置好点击OK,如图18:可以看到设置的参数,以及相互匹配的差分对PIN号

1.2.了解PCB的布线规则以及原理图部分逻辑

做仿真分析前,了解相关PCB布线规则,相关电路和接口的原理是必须的。

2.仿真配置

在本章节中,将会依次介绍如何在Allegro PCB SI界面下进行模型加载和仿真配置,并提取网络拓扑进入到SigXP界面。仿真配置流程如下:

2.1.使用SI Design Setup配置

无论使用哪一种仿真软件,在执行仿真以后,一般都需要对电路板进行一定的配置,配置仿真的环境、模型的分配和参数的设定等等,目的是使仿真能够按照我们所要求的进行下去。

在Allegro PCB SI 16.6版本中,引入了新的SI Design Setup命令,能够更有效地引导用户进行仿真配置。对于16.3及以后的版本,也存在类似的命令,如Database Setup Advisor。SI Design Setup和Database Setup Advisor这些命令本身并不是直接的配置命令,它只是一个向导,引导用户一步一步地执行配置,并在每一步上给出相关配置命令的接口。所以事实上,熟练的工程师也可以不通过这些向导直接调用相关命令对电路板进行配置,效果是一样的。

Allegro PCB SI 16.6版本中的SI Design Setup命令会依次执行以下几个步骤,我们将会在随后的章节中介绍这些步骤的具体执行过程。

2.2.选择需要配置的信号线

为了方便起见,先将之后的所有文件,包括电路板brd文件和仿真模型文件(IBIS和DML)都存放到一个文件夹中,例如E:\Pre_simu。

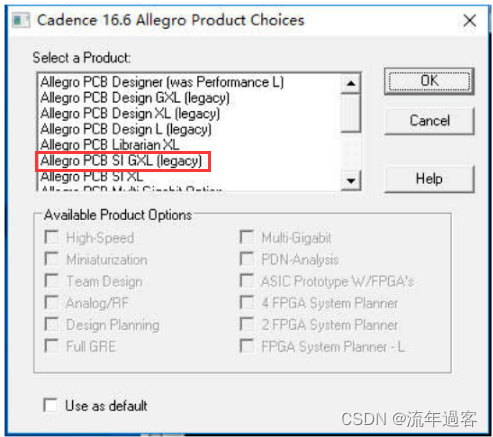

在开始菜单找到 PCB SI快捷方式,在以下窗口选择Allegro PCB SI GXL,并点击OK按钮,即打开Allegro PCB SI窗口:

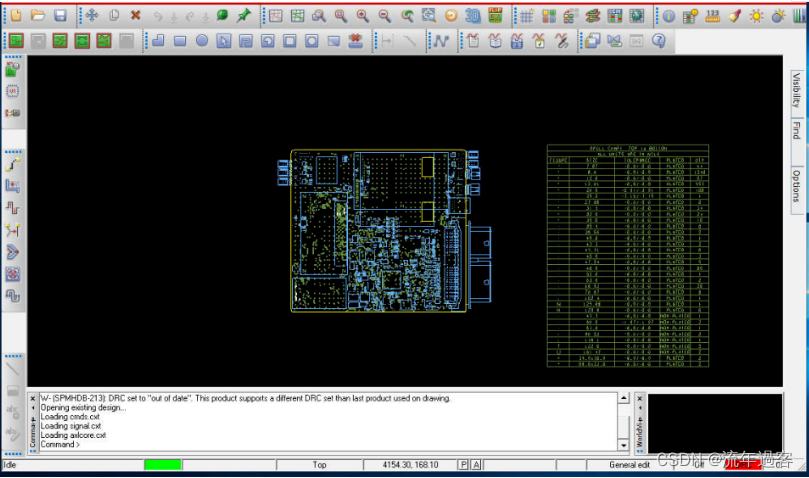

通过File->Open打开TX2P_P0_20171225.brd文件:

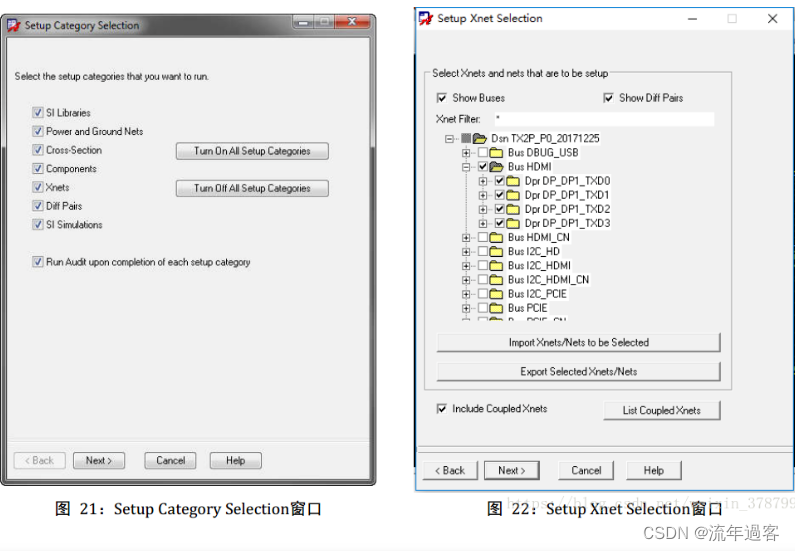

在Allegro PCB SI窗口中选择Setup -> SI Design Setup,会弹出Setup Category Selection窗口。勾选所有选项,并点击Next进入下一环节。Setup Category Selection窗口会切换Setup Xnet Selection窗口。

注意:

在Setup Category Selection窗口的选项中,除了最下面一项,其它都是我们需要通过此向导执行的配置项目;而勾选了最后一项“Run Audit upon completion of each setup categoty”则意味着我们在之后的每一项配置完成后,点击Next进入到下一环节后,都会自动执行针对此环节的仿真审核,以找出我们在配置过程中存在的问题。

而在Setup Xnet Selection窗口中,我们可以只勾选我们关心的、需要执行仿真和配置的网络,这样随后的SI Design Setup配置向导和审核就只会针对这些勾选网络相关的模型、网络和参数等,不需要花时间在无关的网络上。在本案例中,我们勾选Bus HDMI。

2.3设置仿真库

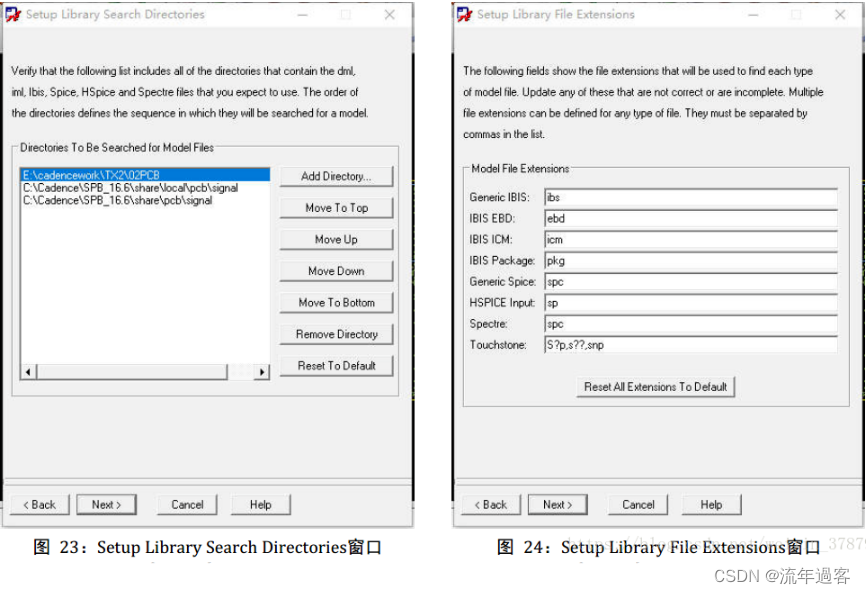

接上节,点击 Next 后 Setup Xnet Selection 窗口会切换至 Setup Library Search Directories 窗口,即设置仿真库搜索路径。默认情况下,库路径包括 brd 文件所在目录以及 Cadence 自带库所在目录,本案例的默认路径即:

E:\cadenccework\TX2\02PCB

C:/Cadence/SPB_16.6/share/local/pcb/signal

C:/Cadence/SPB_16.6/share/pcb/signal

我们可以通过 Setup Library Search Directories 窗口右方的按钮“ Add Directory ”添加新目录;在选中某一原有目录后,可以用“ Remove Directory ”按钮移除;在选中某一原有目录后,还可以用“ Move To Top ”、“ Move Up ”、“ Move Down ”和“ Move To Bottom ”调整目录的相对位置。这里需要说明的是,当所有库路径下存在同名模型时, Allegro PCB SI 会以最先找到的模型为准,也就是位置靠上的路径。

当确认了模型库所在目录都已正确设置,点击“ Next ”按钮继续。 Setup Library Search Directories 窗口将切换至 Setup Library File Extensions 窗口,即设置模型文件后缀窗口。一般而言,这里可保持所有类型的模型文件后缀名为默认,直接点击““Next”按钮继续:

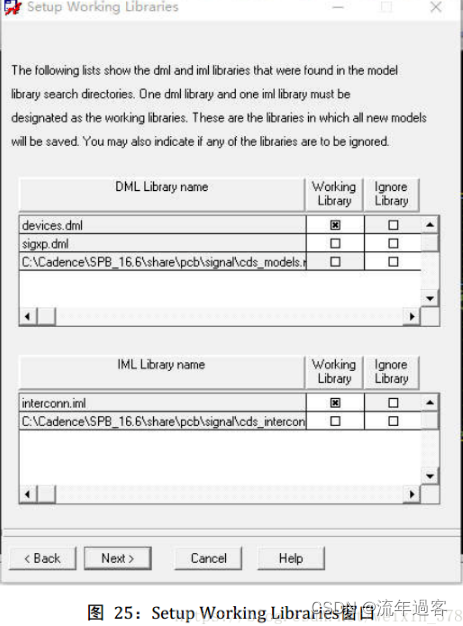

Setup Library File Extensions窗口将切换至Setup Working Libraries窗口,即设置工作模型库窗口。这里会显示之后所设定的库路径下包含的所有DML和IML(Interconnection Model Library)模型库,其中包括软件自动生成的devices.dml和interconn.iml模型库(位于brd文件所在目录,并且默认成为工作模型库)。

这里需要说明的是,所有在Allegro PCB SI中新建的模型都会保存在工作模型库中,工作模型库可以叉选切换,但同时只存在一个。另外,如果需要,我们还可以叉选Ignore Library,选中的模型库将不会在Allegro PCB SI中调用。

在本案例中,我们保持Setup Working Libraries窗口为默认不变,直接点击“Next”按钮进入到下一环节。

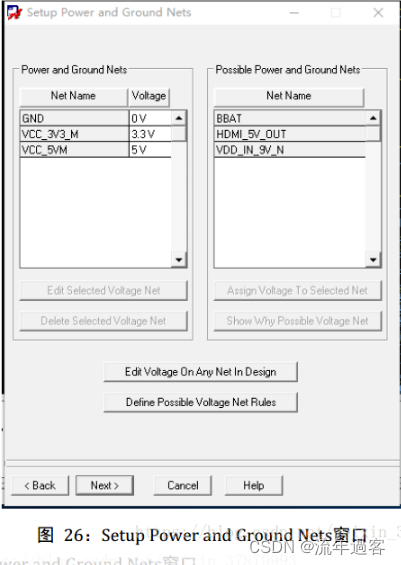

2.4.设置电源和地网络

接上节,Setup Working Libraries窗口会切换至Setup Power and Ground Nets窗口,即设置电源和地网络窗口。Allegro PCB SI会在窗口中显示已经辨识为电源和地的网络(窗口左方),以及疑似电源和地网络(窗口右方)。如果网络和原理图中定义为Power Pin或Ground Pin的管脚相连,则会认为是电源和地网络;如果网络虽然没有和Power Pin或Ground Pin直接相连,但命名中带有VDD、VTT、VSS等关键字符串,则会认为是疑似电源和地网络。

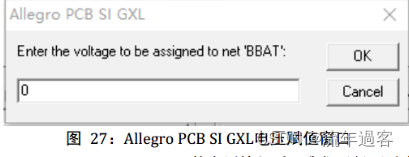

在本案例中,软件给出的电源和地网络是GND和VCC_3V3_M, VCC_5VM,给出的疑似电源和地网络是BBAT, HDMI_5V_OUT, VDD_IN_9V_N。我们在左方的Voltage栏中直接输入电压值0和3.3V, 5V,然后点击BBAT,选择下方的Assign Voltage To Selected Net,然后在弹出的窗口中输入BBAT的电压值0并OK确认,HDMI_5V_OUT, VDD_IN_9V_N同上。

当完成了BBAT, HDMI_5V_OUT, VDD_IN_9V_N的电压输入后,我们以及可以点击“next”进入下一环节。对于其他未知的网络,也可以通过以下操作分配电源和地。

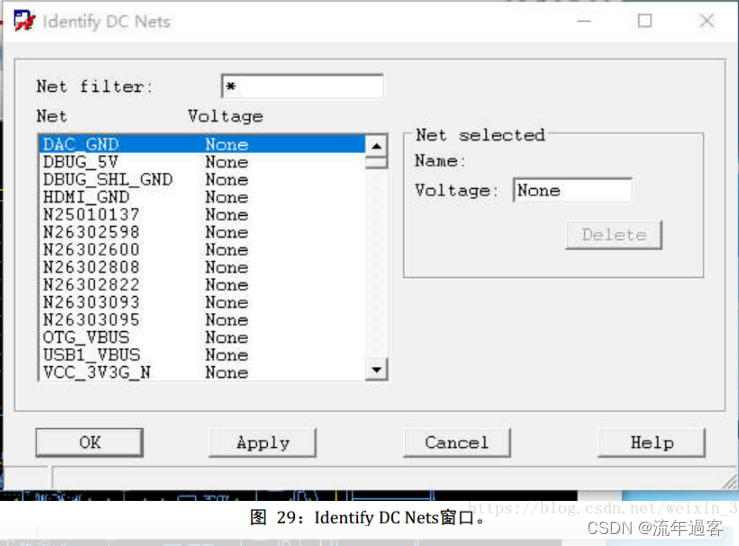

点击Setup Power and Ground Nets窗口下方的“Edit Voltage On Any Net In Design”按钮,会弹出Identify DC Nets窗口,如下:

在Identify DC Nets窗口中找到需设定的电源和地网络,依次在右方的Voltage栏中输入电压值,然后Apply或OK确认。Allegro PCB SI会弹出警告窗口提示网络与非电源或地管脚相连,不去管它,确认即可。

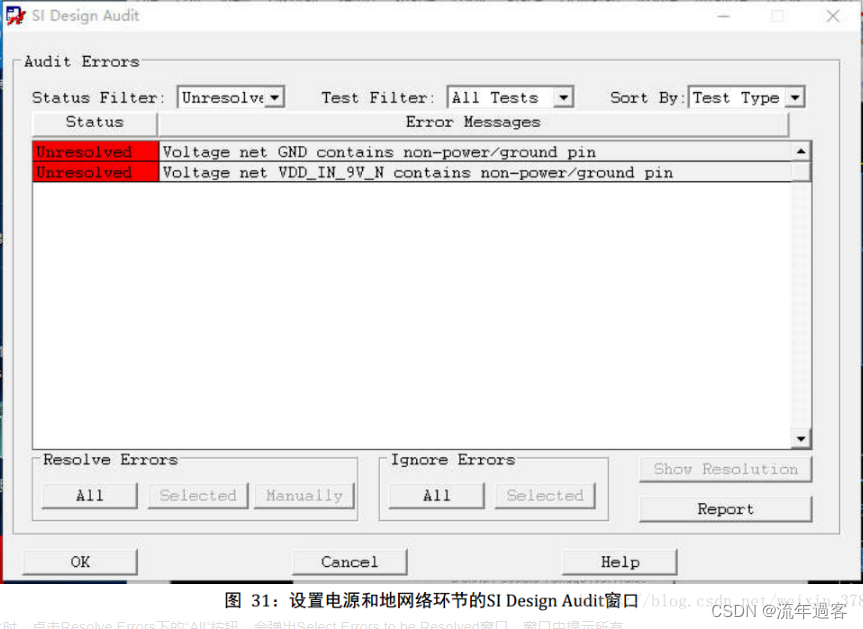

回到Setup Power and Ground Nets窗口,点击“Next”按钮进入下一环节。不过在本案例中,由于本环节的设置存在疑似问题,而之后在Setup Category Selection窗口又勾选了最后一项“Run Audit upon completion of each setup categoty”,因此SI Design Audit窗口会弹出,并显示此环节存在的疑似问题。

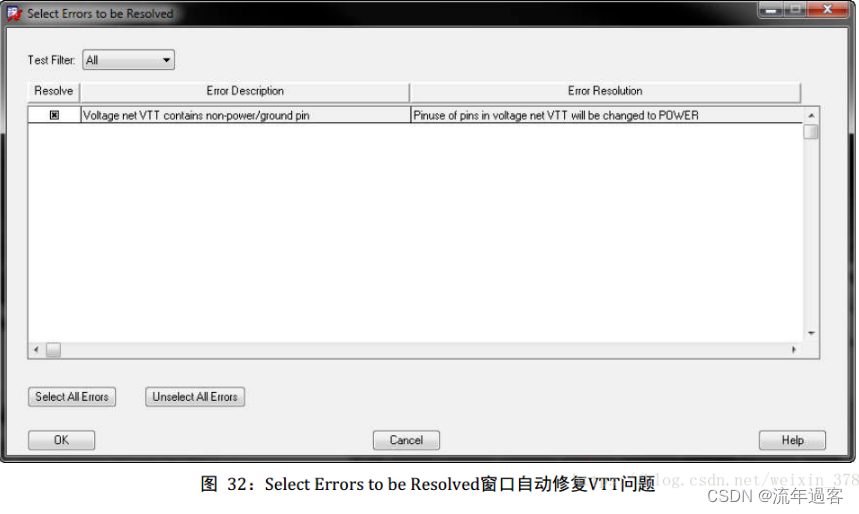

本案例本环节中,疑似的问题是我们在Setup Power and Ground Nets窗口将GND和VDD_IN_9V_N设定为电源和地网络并赋值,而Allegro PCB SI却检查到GND和VDD_IN_9V_N并没有和任何电源和地管脚直接相连。由于GND和VDD_IN_9V_N确实是电源,我们可以选择Ignore Errors忽略它,或者Resolve Errors修复它。此时,点击Resolve Errors下的“All”按钮,会弹出Select Errors to be Resolved窗口,窗口中提示所有VDD_IN_9V_N连接的管脚Pinuse属性会被修改为POWER,所有GND连接的管脚Pinuse属性会被修改为GND,选择OK确认。

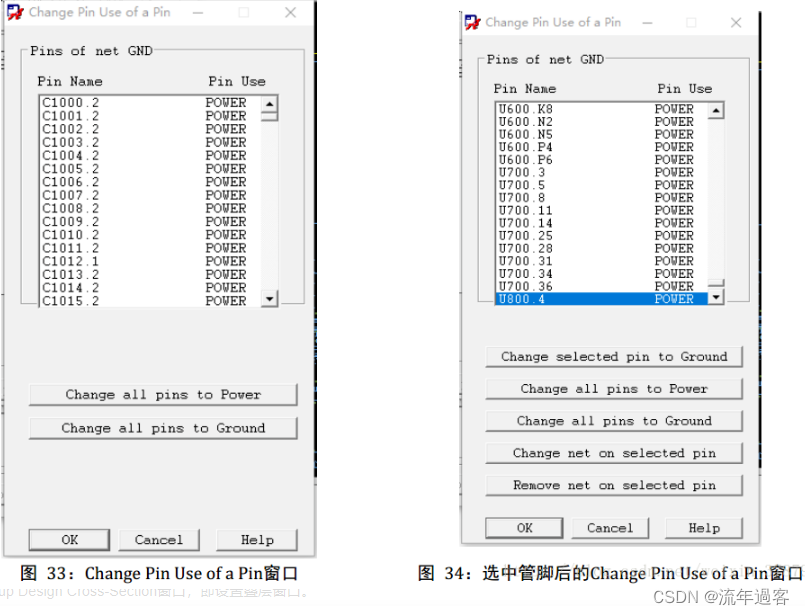

如果希望保持GND和VDD_IN_9V_N电容和匹配电阻管脚的UNSPEC属性不变,只把GND和VDD_IN_9V_N相连的金手指管脚属性修正,可以采用手动地方式执行。选中此错误,点击Resolve Errors下的“Manual”按钮,会弹出Change Pin Use of a Pin窗口。

在Change Pin Use of a Pin窗口中,可以简单地通过下方的按钮将所有管脚改为电源或地属性,也可以点击选中某一管脚后,通过下方的按钮单独修改为电源或地属性。

2.5.设置叠层

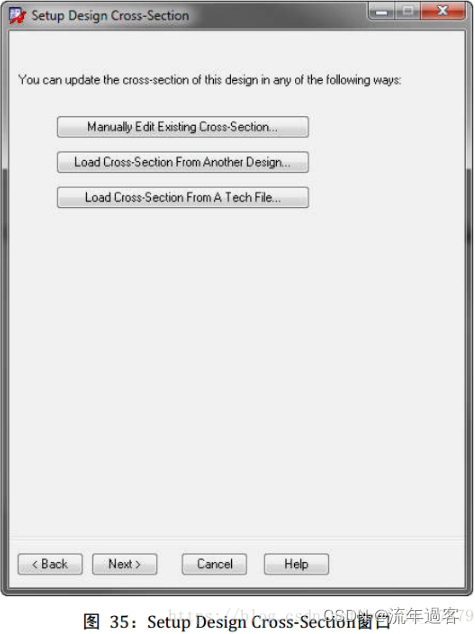

接上节,当我们完成针对上一环节的SI Setup Audit并OK确认后,Setup Power and Ground Nets窗口会切换至Setup Design Cross-Section窗口,即设置叠层窗口:

准确设置电路板的叠层,不仅是仿真的需要,对高速PCB的布线本身,也有一定的必要,例如Allegro的约束管理器(Constraint Manager)是支持用传输延迟来控制“等长”的,这也是相对于控制传输线长度更精确匹配控制方式,但如果叠层没有准确设置,传输延迟的计算也就不再准确,延迟匹配也就无从谈起了。

一般而言,叠层的设计需要依据项目的具体情况,综合成本、结构、密度、电源、信号完整性等多方面因素进行考虑。设计是一个复杂的过程,不过如果是叠层已经确认,只是需要在Allegro PCB SI中输入,就很简单了。叠层的方案可以来自于业界规范,可以来自于已有的设计,也可以来自于PCB板厂的推荐。

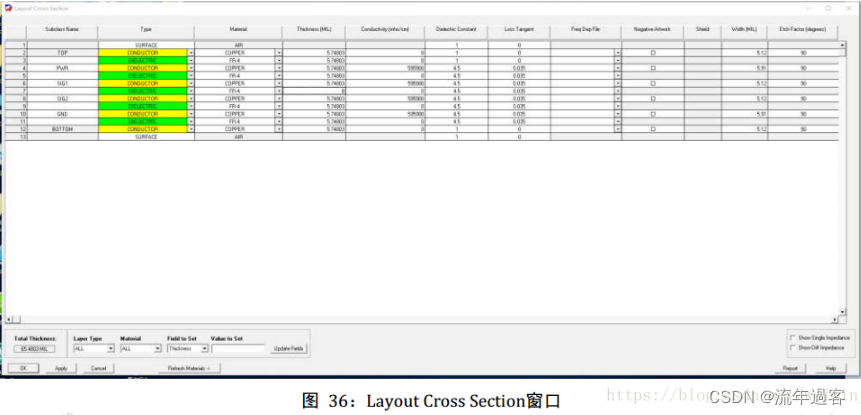

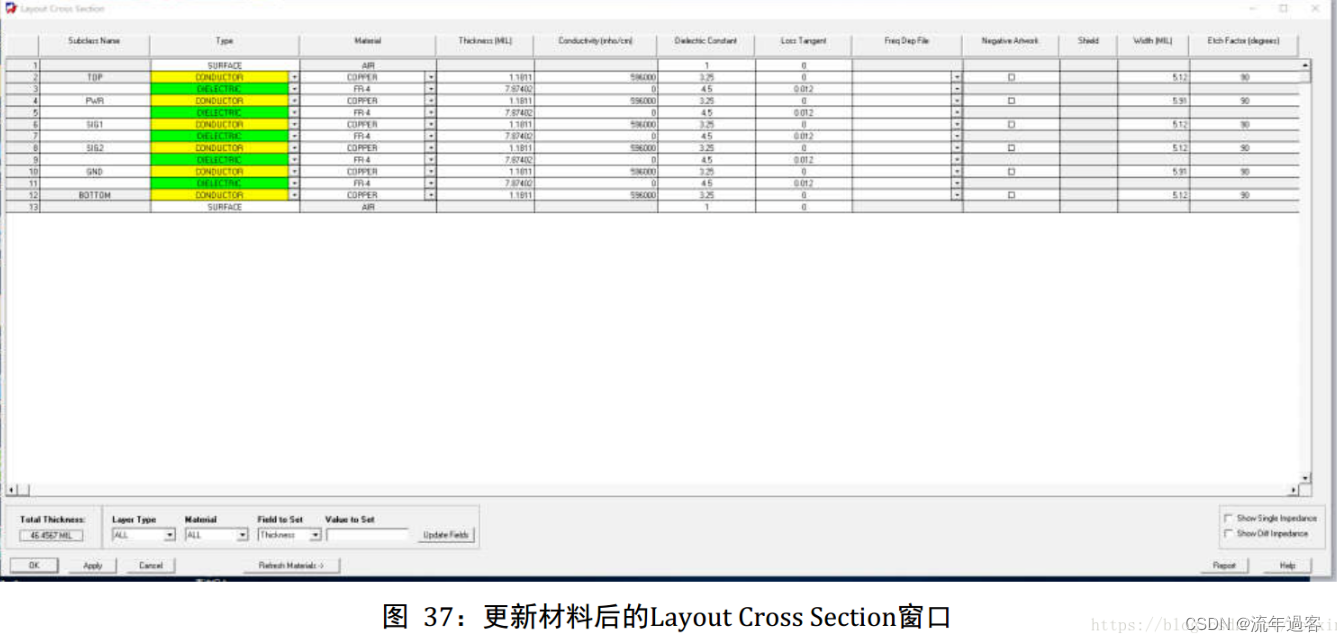

对于本案例,是根据PCB板厂的参数来设置的。在Setup Design Cross-Section窗口中,我们可以点击“Manually Edit Existing Cross-Section”按钮手动设置叠层,也可以点击“Load Cross-Section From Another Design”按钮从现有brd文件中导入叠层信息,或者点击“Load Cross-Section From A Tech File”按钮从现有tch文件中导入叠层信息。在此,我们点击“Manually Edit Existing Cross-Section”按钮,打开Layout Cross Section窗口。我们可以看到这里的叠层设并不合理,点击底部Refresh Materials按钮,选择Refresh All Value,即可。

(Materials的库如何添加见附件:materials问题解决方法.docx)

选中错误消息后点击Resolve Errors栏下方的“ALL”按钮,然后OK确认进入下一环节。

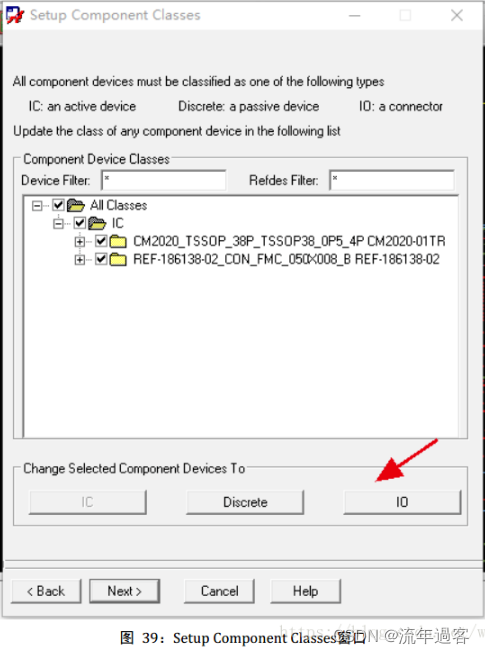

2.6.设置元器件类别

接上节,当我们完成针对上一环节的SI Setup Audit并OK确认后,Setup Design Cross-Section窗口会切换至Setup Component Classes窗口,即设置元器件类别窗口。

这个环节的目的是使随后的仿真中,Allegro PCB SI能够正确的识别元器件的类型,对后续的自动分配元器件模型也有帮助。一般而言,规范的原理图已经对元器件进行了正确的分类,这里只需要确认一下即可,并不需要做多少改正。本案例中,我们可以维持默认不变,也可以本着更严谨的态度,将金手指(指的是PCB与其它设备如主板、机箱等相连接的电连接插脚,因在其铜箔镀镍层上再镀上了薄薄的一层金,英文“bonding finger”)从原先的IC类别改为IO类别。然后点击“Next”按钮进入到下一环节。

2.7.为元器件分配和创建模型

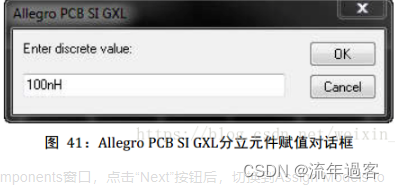

接上节,当所相关的分立元件中包含没有正确赋值的(或者说Value值不符合Allegro要求的)元件时,Setup Component Classes窗口会切换至Assign Values to Discrete Components窗口,即设置分立元件值窗口。如果都已赋值,则直接进入Assign Models to Components窗口

在本案例中,有一个磁珠L1没有赋值。由于此磁珠位于寄存器芯片的模拟电源输入电路上,对我们要仿真的信号无关,所以可简单的赋值,例如100nH,或是忽略也可。在Assign Values to Discrete Components窗口选中L1,点击下方的“Assign Value to Selected Components”按钮,在弹出的赋值框中输入“100nH”,并确认退出。

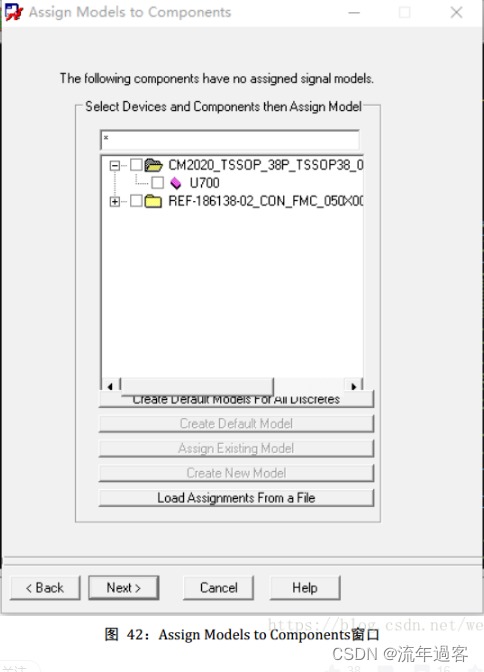

回到Assign Values to Discrete Components窗口,点击“Next”按钮后,切换到Assign Models to Components窗口。

点击Assign Models to Components窗口中“Create Default Models For All Discretes”按钮,Allegro PCB SI会自动给所有已识别的分立元件(指电阻、电容和电感等被动元件)创建默认模型。然后依次给需要设置的元器件分配或创建模型。

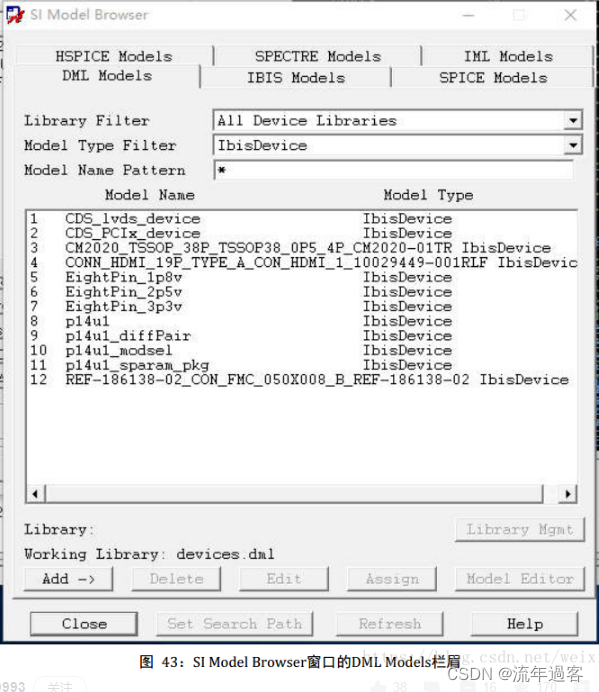

对于本案例,勾选中芯片(“CM2020_TSSOP_…”),然后点击下方的“Assign Exiting Model”按钮,会弹出SI Model Browser窗口并已经自动切换到DML Models栏眉。

选中芯片对应 CM2020_TSSOP_38P_TSSOP38_0P5_4P_CM2020-01TR 模型,然后点击下方的“Assign”按钮,确认弹出的提示栏后,芯片的模型就指定好了。回到Assign Models to Components窗口,选中芯片(“REF-186138-02_CON_FMC_…”),然后点击下方的“Assign Exiting Model”按钮,在弹出SI Model Browser窗口选中REF-186138-02_CON_FMC_050X008_B_REF-186138-02,再点击下方“Assign”按钮,确认弹出的提示栏后,芯片的模型就指定好了。

回到Assign Models to Components窗口后,点击“Next”按钮以进入下一环节。

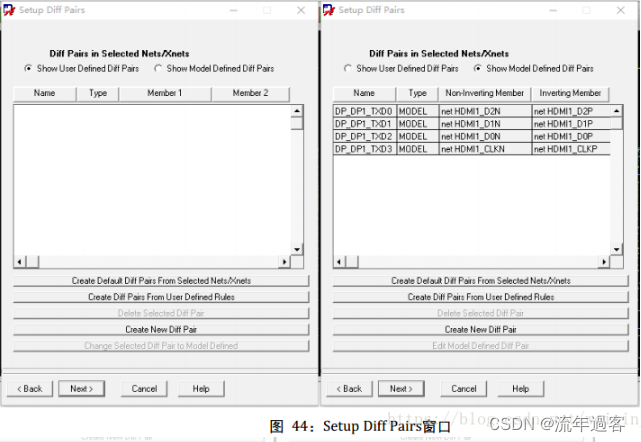

2.8.设置差分对

接上节,当我们完成针对上一环节的SI Setup Audit并OK确认后,Setup Component Classes窗口会切换至Setup Diff Pairs窗口,即设置差分对窗口。

Allegro PCB SI在右边窗口是模型上定义的差分对;左边窗口上并不是要显示brd中存在的差分对,而是会显示已经在Allegro中定义为差分对却在所分配的芯片模型中没有差分定义的网络。本案例中没有出现这样的情况(差分对已经在公版中正确设置),所以可以直接点击“Next”按钮进入下一环节。

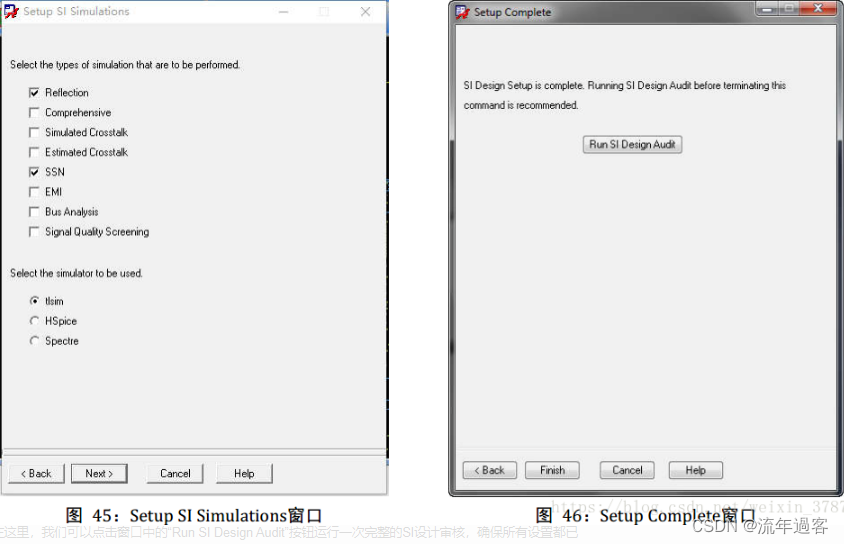

2.9.设置仿真参数

接上节,当完成差分对的设置后,Setup Diff Pairs窗口会切换至Setup SI Simulations窗口,即设置仿真窗口。上半部分设置需要仿真的类型,包括Reflection(反射),Comprehensive(综合),Simulated Crosstalk(串扰仿真),Estimated Crosstalk(串扰评估),SSN(同步开关噪声),EMI(电磁辐射),Bus Analysis(总线分析),Signal Quality Screening(信号质量筛选);下半部分设置仿真器类型,分别是tlsim(Allegro PCB SI自带),HSpice Spectre(后两者都是外部仿真器)。这里我们选择最普遍的反射仿真,同步开关噪声和tlsim仿真器,然后点击“Next”按钮。

在点击“Next”按钮后,Setup SI Simulations窗口将直接切换至Setup Complete窗口,即设置完成窗口。

在这里,我们可以点击窗口中的“Run SI Design Audit”按钮运行一次完整的SI设计审核,确保所有设置都已确认无误后,点击下方的“Finish”按钮结束SI Design Setup。虽然这里完成了SI Design Setup的所有环节,但是我们的仿真设置并没有真正完成,还需要进行仿真参数设置。

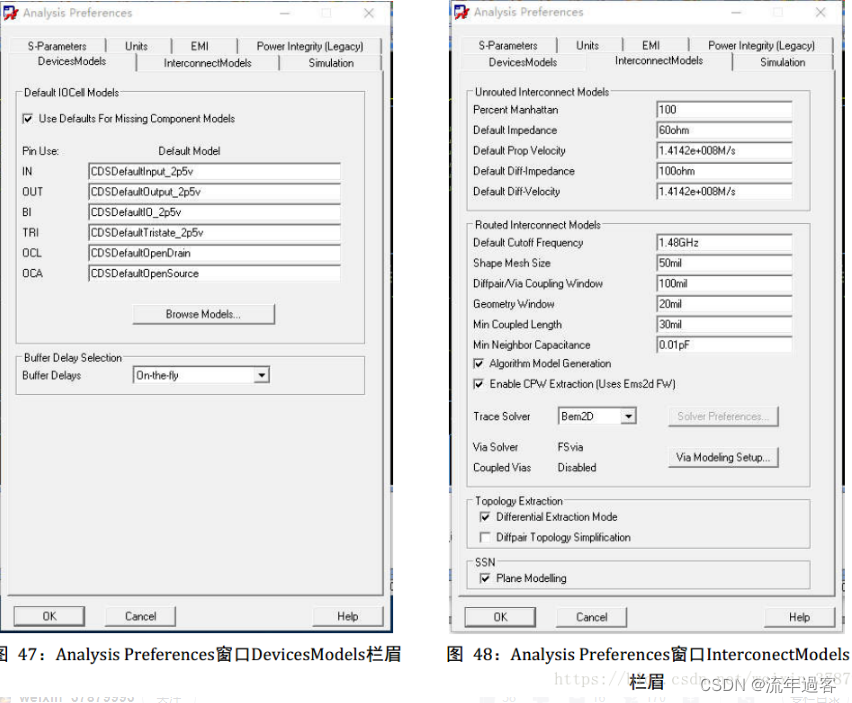

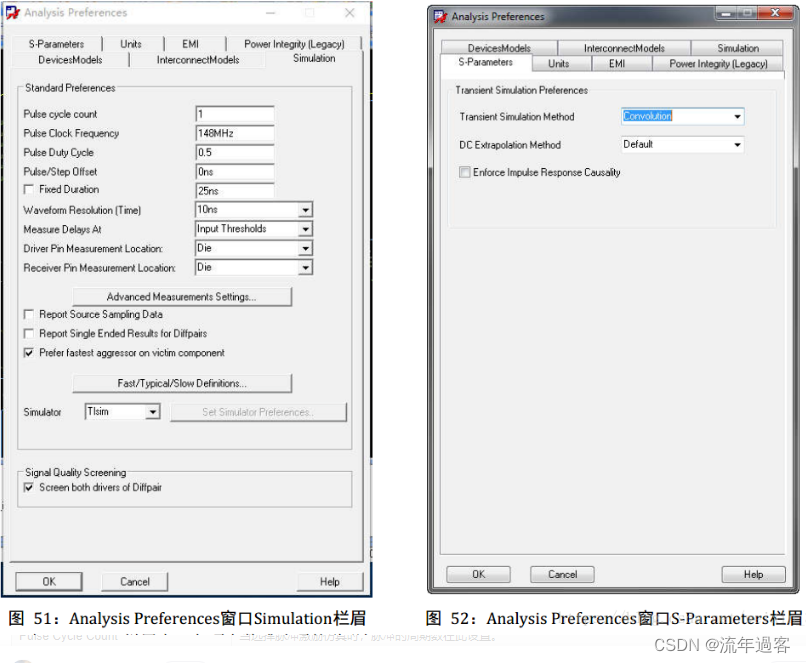

选择Allegro PCB SI GXL中的命令Analyze -> Preferences,会弹出Analysis Preferences窗口,其中包含七个栏眉,分别是DevicesModels、InterconnectModels、Simulation、S-Parameters、Units、EMI和Power Integrity,依次列在下文中。

DevicesModels 栏眉中可设置当元件模型缺失时默认的缓冲器模型,以及 Buffer Delays 缓冲器延迟。可以在此选择 On-the-fly ,会在仿真的同时计算 Buffer Delays ,而无需事先仿真计算出 Buffer Delays 。

InterconnectModels 栏眉中,可以设置传输线模型过孔模型等。在上半部分 Unrouted Interconnect Models ,即未布线互联模型中,可保持默认, Allegro PCB SI 在处理尚未连接的传输线(也就是鼠线)时,会按照这里的参数建模。在中部是 Routed Interconnect Models ,即已布线互联模型,需要根据建模精度的要求调节,具体如下表。

表格 1 : Routed Interconnect Models 参数

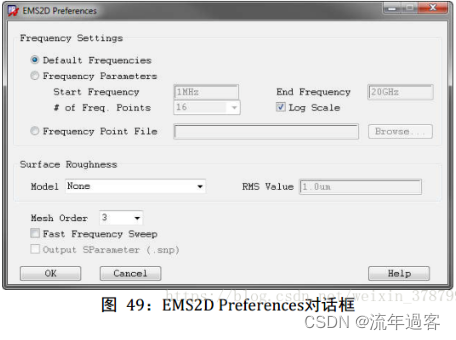

另外,当在 Field Solver 栏选择 EMS2D 场求解器时,可通过右方的“ Preferences ”按钮打开 EMS2D Preferences 对话框,设定 EMS2D 场求解器的参数。

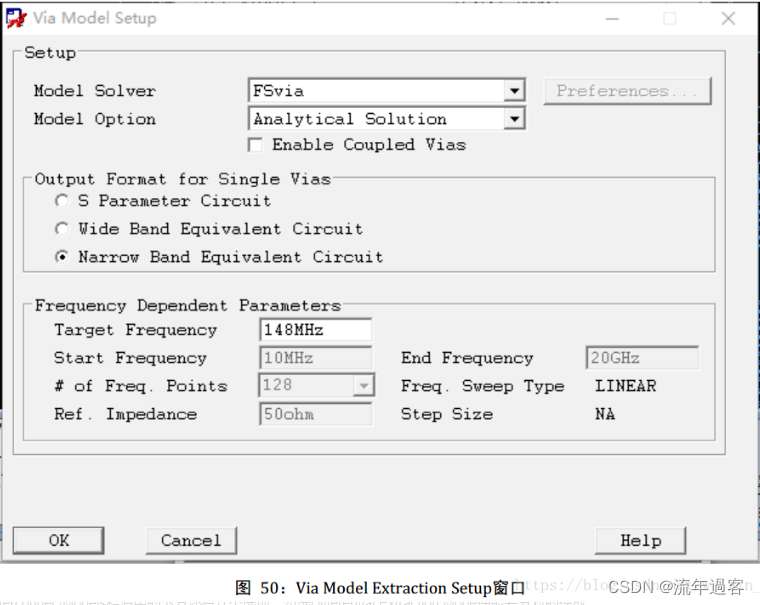

而通过下方的Via Modeling Setup按钮可打开Via Model Extraction Setup窗口,设置过孔模型的提取。

在InterconnectModels栏眉中的下方还有几个选项,勾选Differential Extraction Mode使能差分对的提取,不选Diffpair Topology Simplification禁用差分对模型简化功能,Plane Modeling用于SSN同步开关噪声仿真,本案例中需要勾选。

在Simulation栏眉中,各项参数或选项的说明如下:

表格 2 : Simulation 栏眉仿真参数

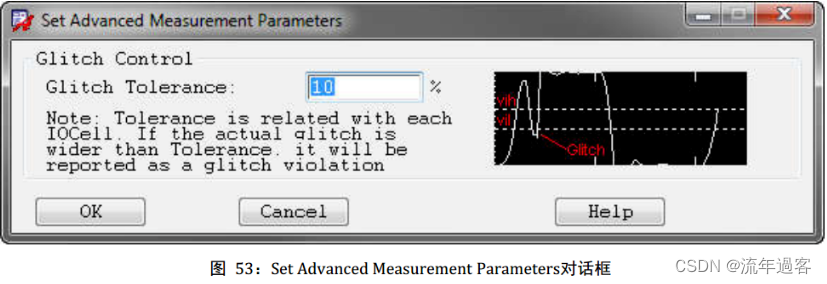

在 Simulation 栏眉中还有两个设置按钮,点击“ Advanced Measurements Settings ”按钮会打开 Set Advanced Measurement Parameters 对话框,主要用于设置 Glitch( 故障 ) 容差。

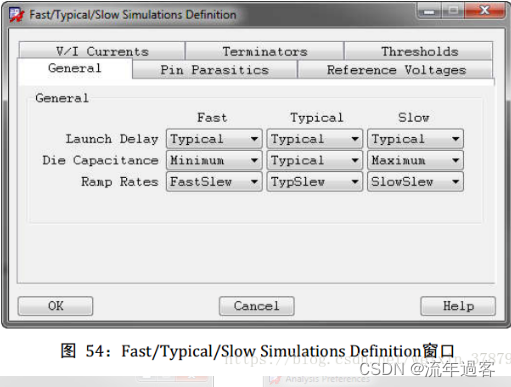

点击“Fast/Typical/Slow Definitions”按钮会打开Fast/Typical/Slow Simulations Definitions窗口,用于设置Allegro PCB SI 在选择Fast/Typical/Slow 类型执行仿真时,所对应的模型数据。

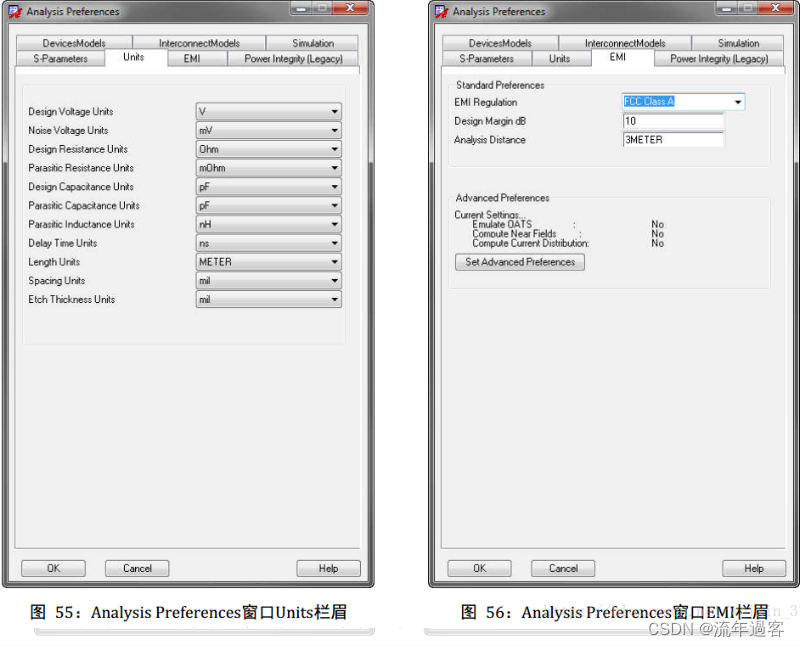

Units栏眉中可设定仿真中的默认单位,一般保持默认即可。

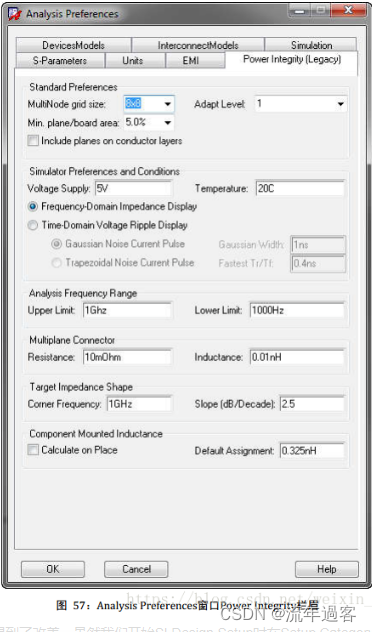

EMI栏眉在执行EMI仿真时使用,用于设置EMI等级,设计裕量和分析距离等。与本案例无关。

Power Integrity 栏眉是设定 PI 仿真( 16.5 版本命名为 PDN Analysis )的参数,与本案例无关,不做详解。

2.10.SI Design Audit相关

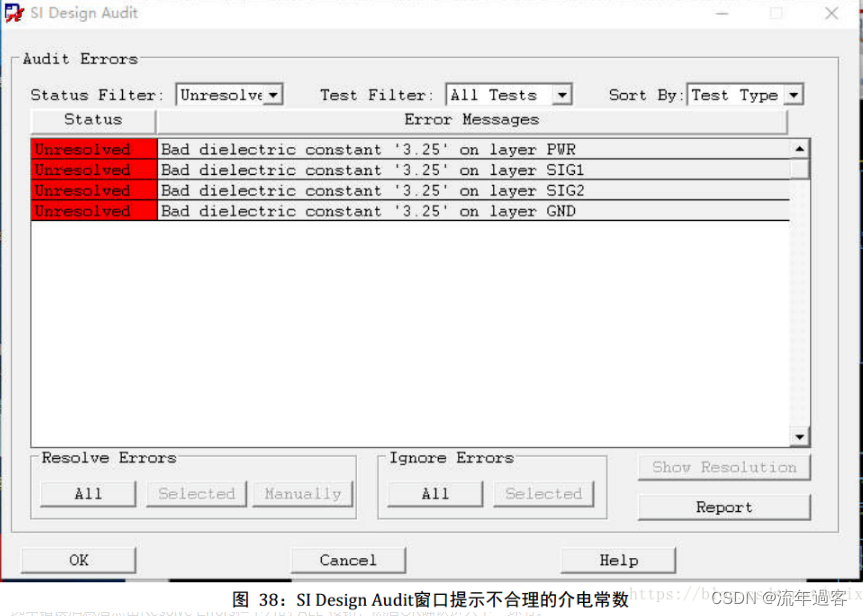

SI Design Audit命令在16.6版本中也得到了改善,虽然我们开始SI Design Setup时在Setup Category Selection窗口已经勾选了“Run Audit upon completion of each setup categoty”选项(图10),但依然建议在SI Design Setup结束后在Setup Complete窗口点击Run SI Design Audit,或者Allegro PCB SI界面下选择Setup -> SI Design Audit执行一次完成的仿真审核过程。原因是当我们按照SI Design Setup的步骤执行了靠后的环节时,部分设置可能影响到之后已有的设置,重新执行仿真审核可避免因此带来的问题。例如添加了芯片IBIS模型后,器件的PINUSE属性会依据IBIS模型中的缓冲器类型自动修改,这样就有可能出现我们之后没有注意到的电源和地管脚,有可能影响到仿真的执行。

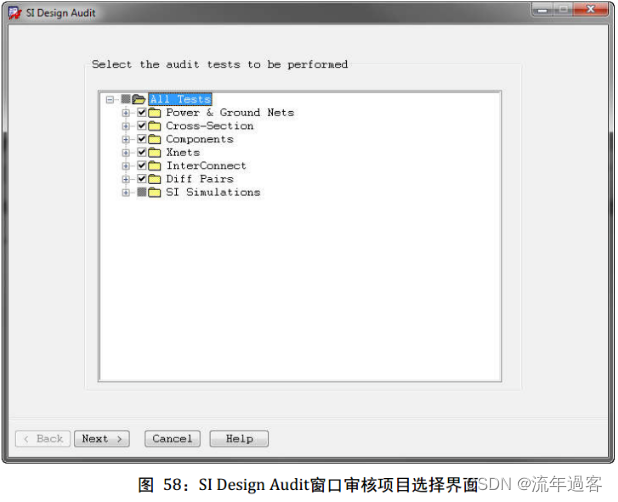

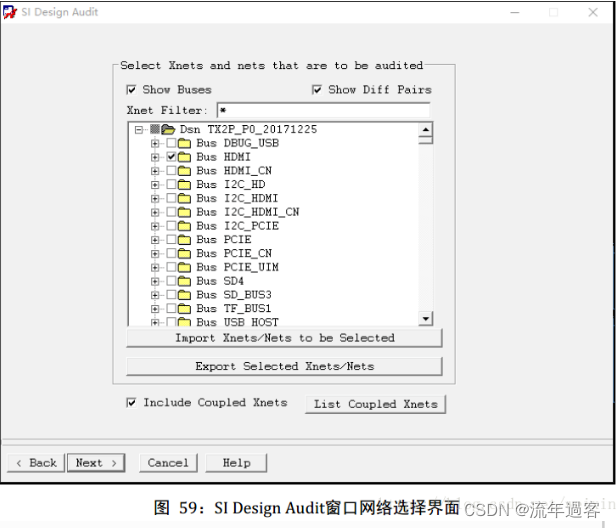

当点击SI Design Audit命令开始仿真审核时,SI Design Audit窗口会弹出并首先显示审核项目选择界面,保持默认的全选,点击下面的next,进入下一环节。

接下来,和SI Design Setup流程时类似,SI Design Audit窗口会进入到网络选择界面,选择需要执行审核的网络。在本案例中选择保持全选,然后点击下方的“Next”按钮,进入下一环节。

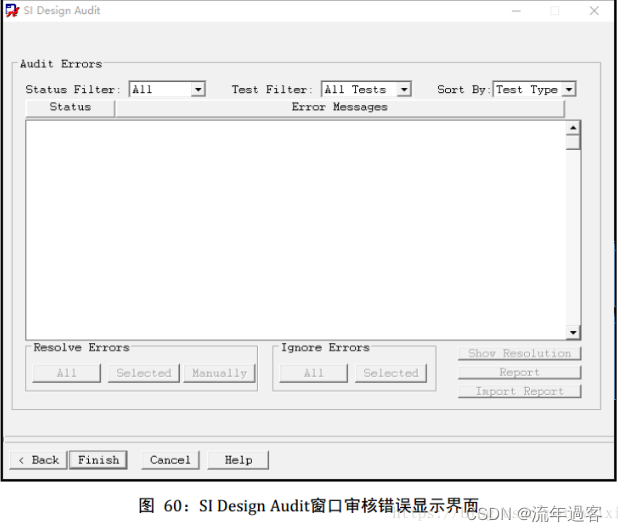

接下来,SI Design Audit在经过短暂的运行后,会将当后设计中存在的SI设置问题列举出来,我们可以描述的问题选择忽略(Ignore Error栏),或是通过自动方式(Resolve Errors栏中“All”或“Selected”按钮)或手动方式(Resolve Errors栏中“Manually”按钮)解决。

2.11.提取拓扑

提取网络拓扑的方式很简单,在16.6版本中可以采用新的简便方式或传统的方式。新的方式是,在Allegro PCB SI工作台(canvas)的空白区域右键单击,在弹出的右键菜单中选择Application Mode -> Signal Integrity切换到SI模式用户界面下。

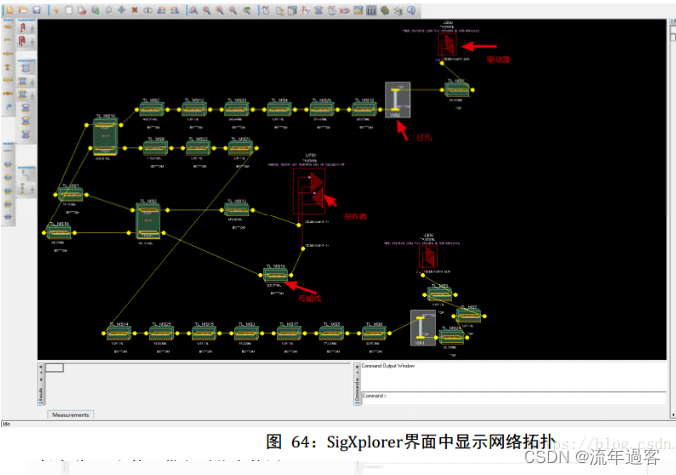

确认右方的Find Filter栏已勾选Net,鼠标移动至传输线上方,右键选择View Topology,经过一段时间的运算后,SigXplorer(也叫SigXP,或Signal Explorer)窗口就会弹出,并显示信号拓扑。

保存此top文件,供之后仿真使用。

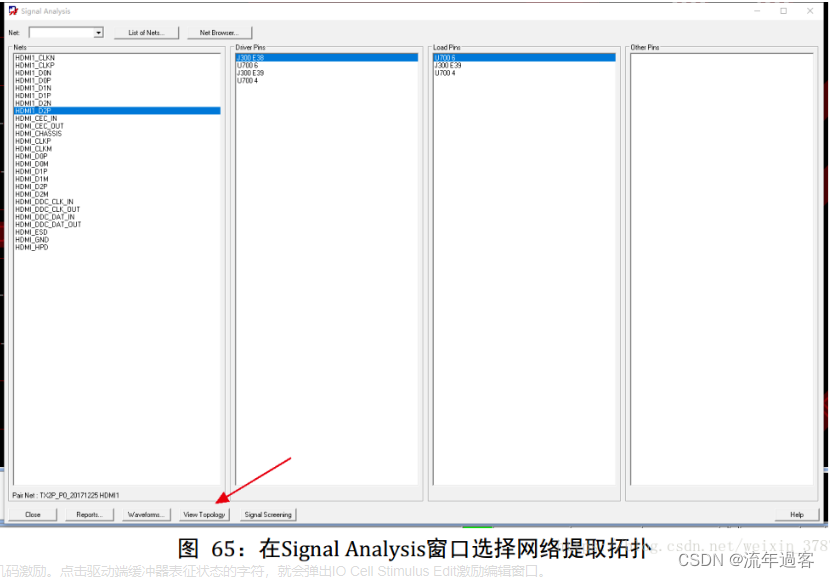

传统的方式是在Allegro PCB SI菜单中选择Analyze -> Probe,在弹出的Signal Analysis窗口中找到网络LA<9>,点击“View Topology”按钮,同样可提取出上述拓扑进入SigXplorer中。

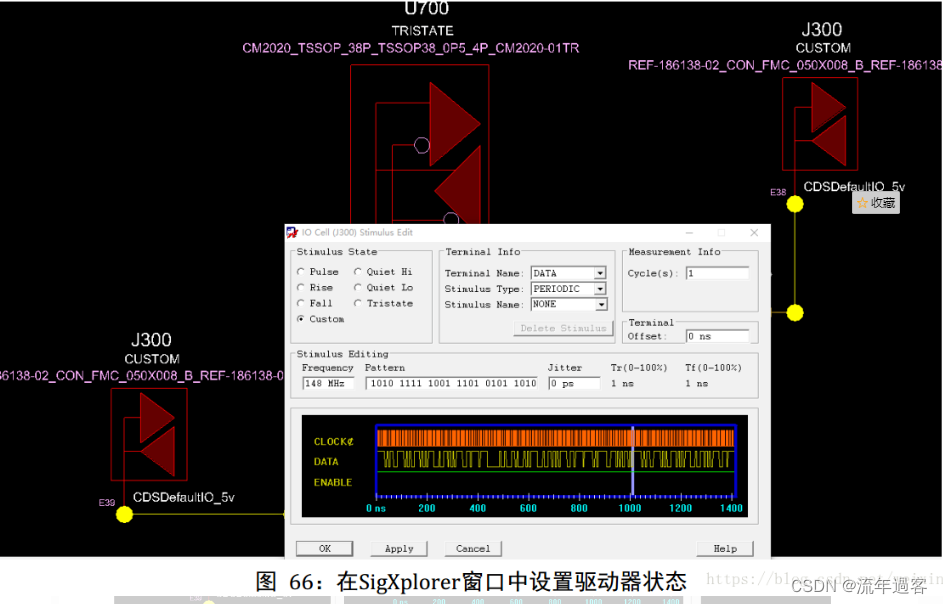

无论是手动创建拓扑,或是提取的拓扑,我们都需要给驱动端添加适当的激励,并选择所需的测量。

对于非脉冲周期性信号,例如本案例中的地址信号,为了仿真出码间串扰的影响,我们常常需要添加伪随机码激励。点击驱动端缓冲器表征状态的字符,就会弹出IO Cell Stimulus Edit激励编辑窗口。

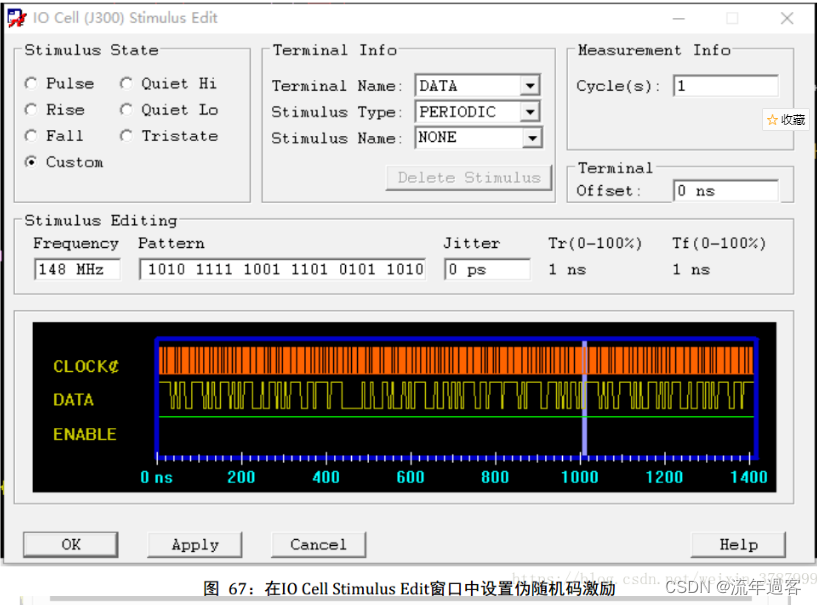

在IO Cell Stimulus Edit激励编辑窗口中,Stimulus State激励状态选择Custom,Frequency频率栏输入148MHz,Pattern栏输入127位1+X+X7 PRBS伪随机码序列,其他保持不变,然后确认退出。

说明一下IO Cell Stimulus Edit窗口的选项:

表格 3 : IO Cell Stimulus Edit 窗口中的选项

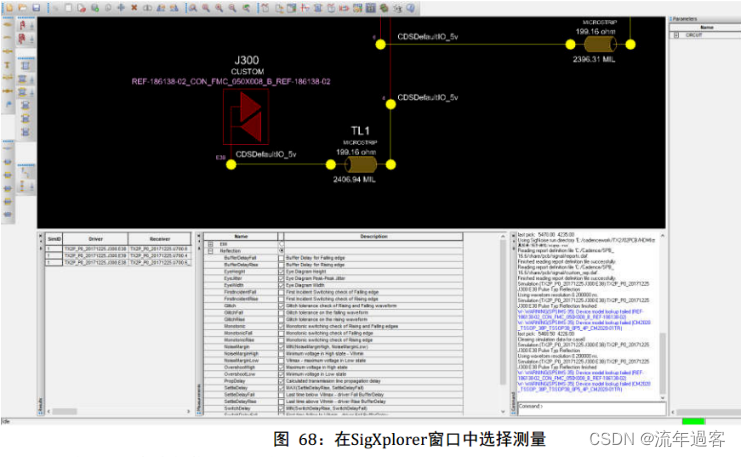

测量项的选择则是在 SigXplorer 窗口的 Measurement 栏中设置,一共有 4 个大类供选择,分别是 EMI 、Crosstalk (串扰)、 Reflection (反射)和 Custom (自定义),每一次仿真只能选择一个大类下的测量。和前文提到的一样,自定义测量需要实现创建或导入。在本案例中,我们保持默认选择的 Reflection 大类及其默认项即可。

设置完成后,保存拓扑,进入下一环节。

3.后仿真报告结果验证

3.1.信号波形

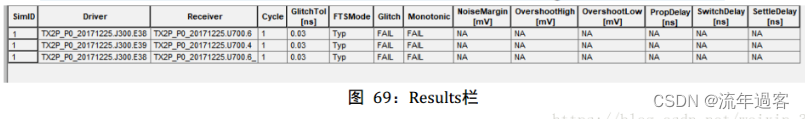

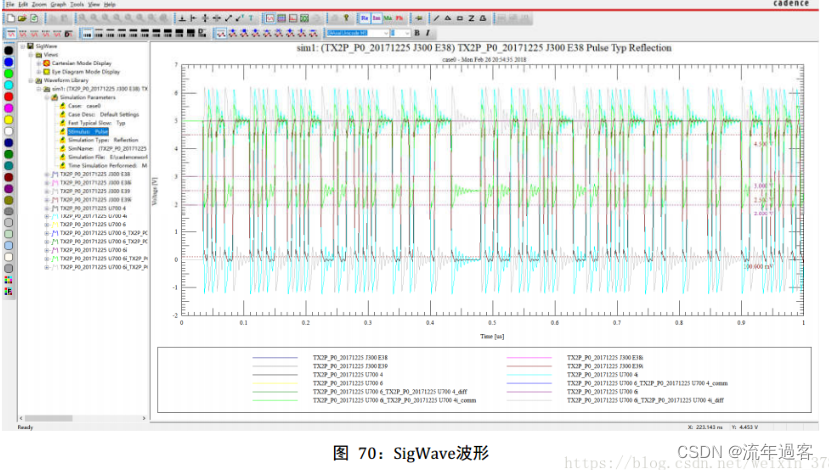

创建或提取并设置好仿真拓扑,就可以执行仿真了。点击Analyze -> Simulate或者 快捷按钮,在一段时间之后仿真完成,测量结果显示在Results栏,同时也会弹出SigWave窗口显示波形。

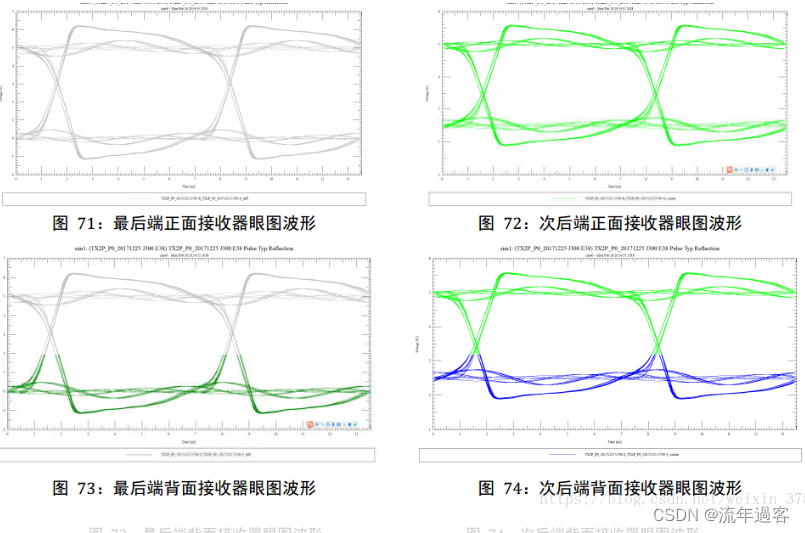

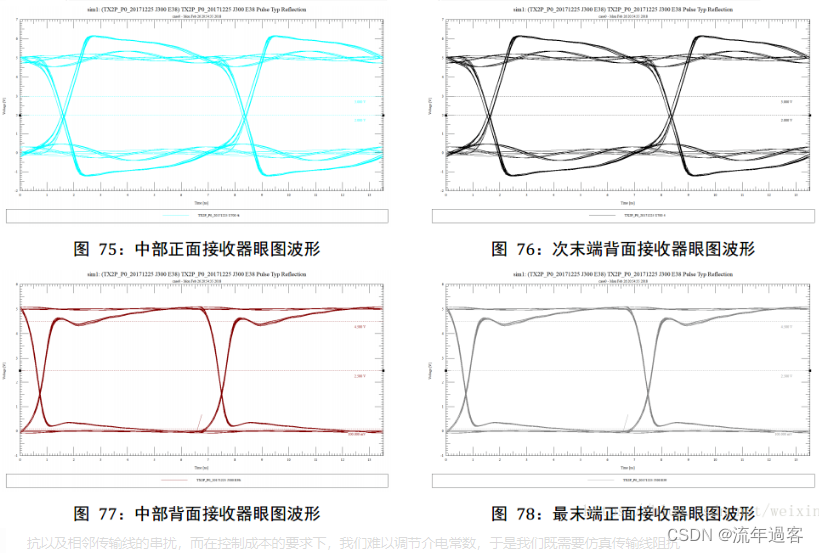

我们可以在Results栏中查看测量结果是否存在问题,也可以更直观地在SigWave查看每一个接收器的波形。在SigWave中,波形可以按照时域(Cartesian)、总线(Bus)、频域(FFT)和眼图(Eye Diagram)模

式显示。我们用眼图模式显示每一个接收器的晶元处波形如下。

上面已经仿真出结果,但是后仿真不仅仅是这样,本案例中,由于布局布线空间的限制,每两个芯片之间的连线长度有一个范围,我们需要仿真连线是不是越短越好;终端并联匹配电阻通常都是等于传输线阻抗,但是却有人提出电阻阻值偏小一些信号更好,我们需要通过仿真确认电阻阻值;叠层和线宽会影响到传输线的阻抗以及相邻传输线的串扰,而在控制成本的要求下,我们难以调节介电常数,于是我们既需要仿真传输线阻抗的选择,也需要确认什么样的线宽、线间距以及平行长度下串扰的影响可以接受。以上种种,我们不仅需要找出“最”优化方案,也要根据实际情况的需要给出在此方案下所允许的裕量空间,是为方案空间分析。

方案空间分析一般有两种方式,其一是固定其他参数或条件,只扫描某一参数值对仿真结果的影响;其二是将所有的未确认参数都在同一个仿真文件(拓扑)中扫描。后者耗时少,但并不是每一个参数对仿真结果的影响都是线性单调变化,导致所得到的最优值以及可变空间不能适应所有情况;后者在参数多的情况下,仿真量将是一个天文数字。因此我们常常需要在一定的理论和经验的基础上,结合两种方式进行仿真分析。

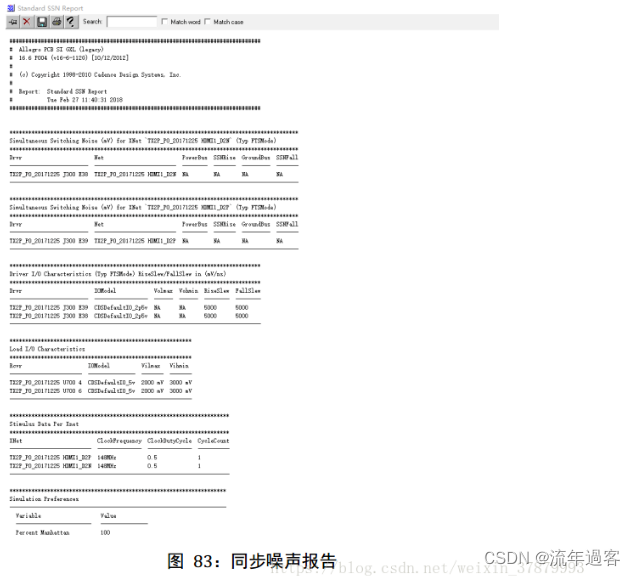

3.2.反射报告,延时报告以及同步噪声报告

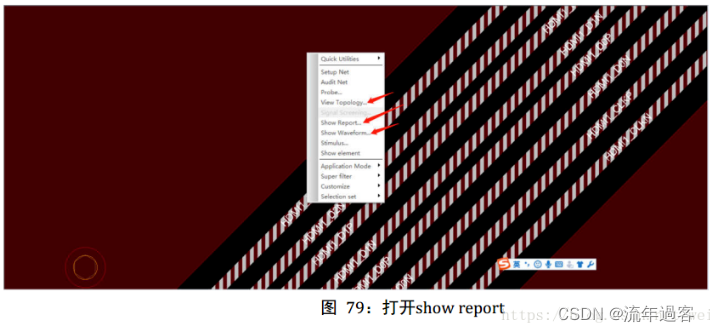

用以下方法:左键单击所要仿真的差分线,右键首先选择show Report

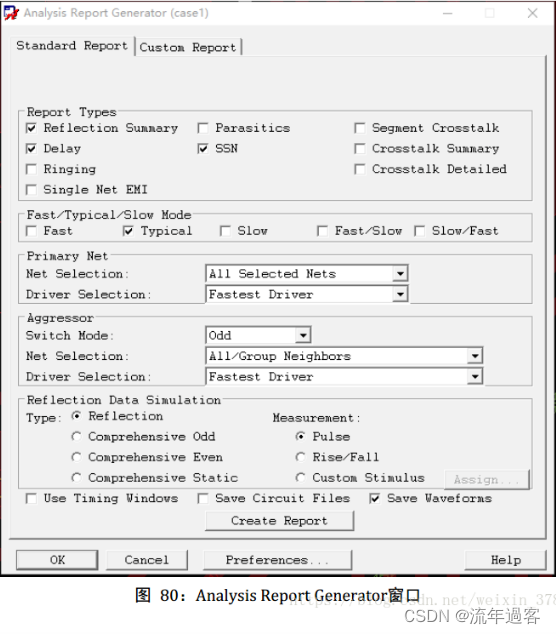

出现如下图所示:Reflection Summary:反射总结 Delay:延时报告 SSN:同步噪声分析 Typical:典型模式;然后点击create report:

出现如下图所示:等待即可

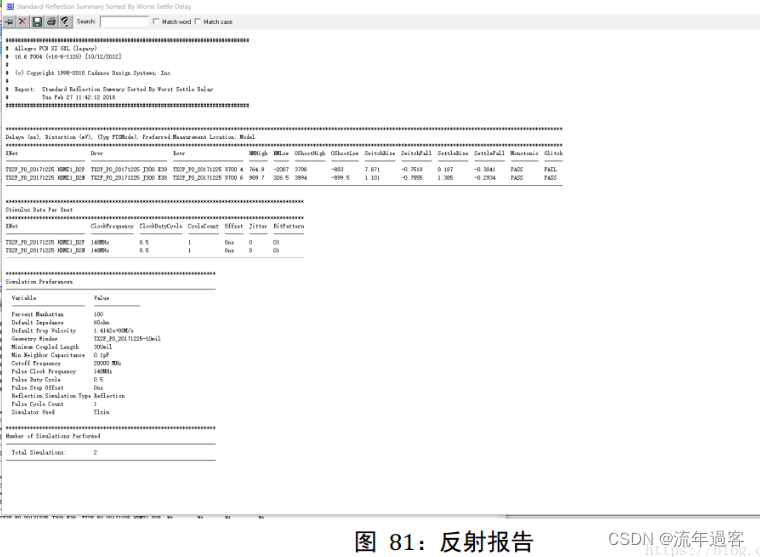

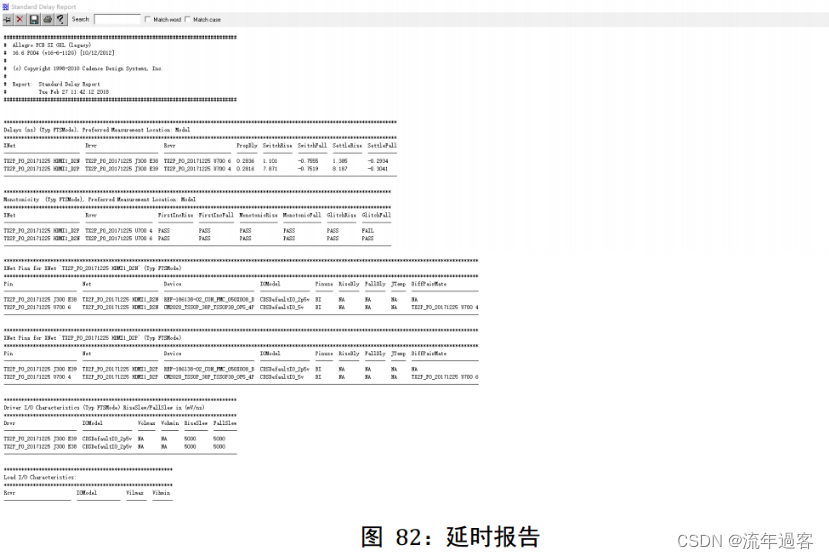

完成后有如下所示:标准延时报告和在最糟糕的延时情况下标准反射总结报告以及同步噪声分析报告

可以通过报告来验证规则设定以及LAYOUT是否符合预期。