文章目录

- 连续分配方式会形成大量碎片,虽然可通过

紧凑方法将许多碎片拼接成可用的大块空间,但须为之付出很大开销离散分配:将一个进程直接分散的装入到许多不相邻接的分区中,离散分配分为以下三种

- 分页存储管理

- 将用户程序的地址空间分为若干个固定大小的区域,称为“页”或“页面”,典型的页面大小为1kb

- 相应的也将内存空间分为若干个物理块或页框

- 页和块大小相同,这样可将用户程序的任一页放入任一物理块中,实现离散分配

- 分段存储管理

- 把用户的地址空间分为若干个大小不同的段,每段可定义一组相对完整的信息

- 在存储器分配时,以段为单位,这些段在内存中可以不相邻接,所以同样实现了离散分离

- 段页式存储管理

- 分页和分段两种存储管理方式相结合的产物,同时具有两者的优点,目前应用较广泛的一种存储管理方式

一. 分页存储管理方式

1.1 分页存储管理的基本方法

1.1.1 页面和物理块

- 页面:

- 分页存储管理将进程的逻辑地址空间分成若干个页,并为各页加以编号,从0开始。

- 在为进程分配内存时,以块为单位,将进程中的若干个页分别装入到多个可以不相邻接的物理块中。

- 由于进程的最后一页经常装不满,形成了不可以利用的碎片,称为页内碎片

- 页面大小:

- 在分页系统中,若选择过小的页面大小,虽然一方面可以减小内存碎片,有利于内存利用率的提高,但另一方面却会造成每个进程占用较多的页面,从而导致进程的页表过长,占用大量内存,此外,还会降低页面换进换出的效率

- 如果选择的页面过大,对然可能减少页表长度,提高页面换进换出的速度,但又会使页内碎片增大,

- 页面大小应选择使用,且为2的幂,通常为 1KB ~ 8KB

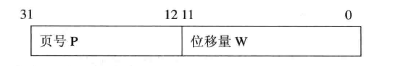

1.1.2 地址结构

分页地址中的地址结构如下

- 它包含两部分内容:前一部分为页号P,后一部分为位(偏)移量W,即页内地址

- 上图中,地址长度为32位,其中0~11位是业内地址,即每页大小为4KB; 12 ~31位为页号,即地址空间最多有1M页(220)

- 设系统页面为1KB(210),A = 2170B,则 P = 2,d = 122 (2 * 1024 + 122 = 2170)

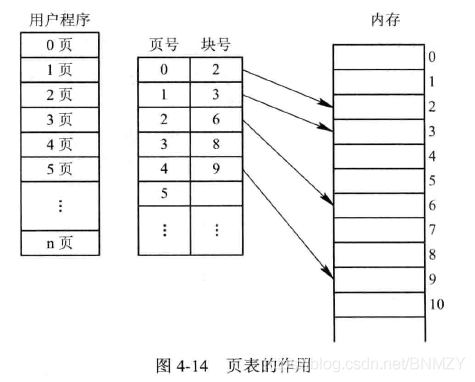

1.1.3 页表

- 分页系统中,允许将进程的各个页离散地存储在内存的任一物理块中,为保证进程仍能够正确的运行,即能在内存中找到每个页面所对应的物理块,系统又为每个进程建立了一张页面映像表,简称页表

- 如图,页表的作用是实现从页号到物理块号的地址映射

- 即使在简单地分页系统中,也常在页表的表项中设置一存取控制字段,用于对该存储块中的内容加以保护。如当存取控制字段仅有一位时,可用来规定该存储块中的内容是允许读/写还是只读,两位时则可以读/写,只读和只执行等存取方式,当一个进程试图去写一个只允许读的存储块时,将引起操作系统的一次中断

- 如果要利用分页系统实现虚拟存储器,则还必须增设一个数据项,将在下文中介绍

1.2 地址变换机构

- 为了能将用户地址空间中的逻辑地址转换为内存空间中的物理地址,在系统中必须设置地址变换机构

- 变换机构的基本任务是实现从逻辑地址到物理地址的转换,即将页号转换为块号

- 地址变换任务是借助于页表来完成的

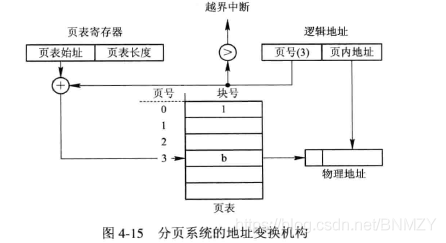

1.2.1 基本的地址变换机构

- 进程运行期间需要将用户地址空间中的逻辑地址变换为内存空间中的物理地址,由于它执行效率非常高,因为每条指令都需要进行变换,故需要由硬件来实现

- 页表功能是由一组专门的寄存器来实现的,一个页表项用一个寄存器,但是由于寄存器成本较高,且大多数现代计算机的页表很大,显然不可能所有页表项都用一个寄存器。

- 因为第 2 点,页表大多驻留在内存中,在系统中只设置一个页表寄存器PTR,在其中存放页表在内存的始址和页表的长度,平时进程未运行时,页表的始址和页表长度存放在本进程的PCB中。当调度程序调度到某进程时,才将这两个数据装入页表寄存器中

- 当进程要访问某个逻辑地址中的数据时,分页地址变换机构会自动的将有效地址(相对地址)分为页号和页内地址两部分,再以页号为索引去检索页表(该操作由硬件执行),产生以下两种结果

- 页号大于页表长度:表示本次访问的地址已超越进程的地址空间,这一错误将被系统发现,并产生一地址越界错误

- 页号在页表长度内:页表始址 + 页号*页表项长度 = 该页表项物理起始位置,加上页内偏移量(页内地址)就是数据的物理地址

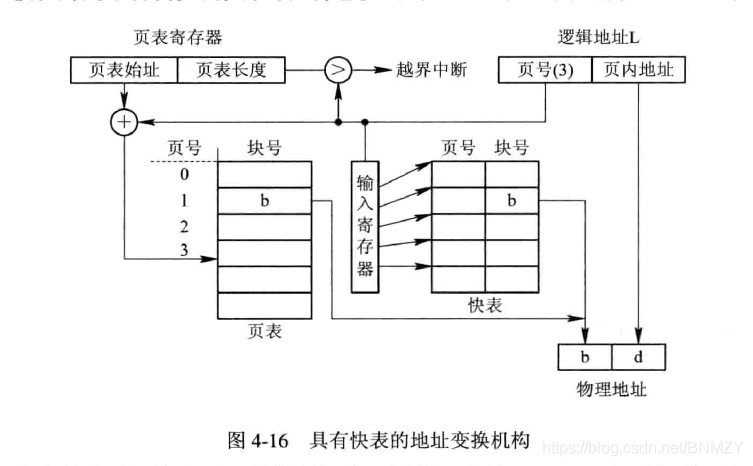

1.2.2 具有快表的地址变换机构

- 由于也表示存放在内存中的,所以CPU每存取一个数据时,都要两次访问内存。第一次访问内存中的页表,从中找到指定页的物理块号,再将块号与页内偏移量W拼接,形成物理地址。第二次访问内存时,才是从第一次所得地址中获得所需数据(或向此地址中写入数据)。因此,采用这种方式将使计算机的处理速度降低近1/2

- 为了提高地址变换速度,可在地址变换机构中增设一个具有并行查询能力的特殊高速缓冲寄存器,又称为联想寄存器,或称为快表,用以存放当前访问的那些页表项。

- 此时的地址变换过程是:在CPU给出有效地址后,由地址变换机构自动的将页号P送入高速缓存寄存器,并将此页号与高速缓存中的所有页号进行比较,若其中存在相应匹配的页号,便表示所要访问的页表项在快表中,可直接从快表中读出该页的物理号,并送到物理地址寄存器中

- 如果快表中未找到,则还需要访问内存中的页表,找到后把页表项中读出的物理块号送往地址寄存器,同时将 此页表存入快表的一个寄存单元中

- 若联想寄存器已满,则OS必须找到一个老的且已被认为是不再需要的页表项,将它换出

1.3 访问内存的有效时间

二. 分段存储管理方式

版权声明:本文为BNMZY原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接和本声明。