用case语句写出比较电路:

推出一个2位较大数判断电路的真值表

用case语句编写判断电路

1、给出程序

2、给出仿真程序

3、给出RTL图

4、给出仿真结果

1、真值表

当data1=data2时,输出为0,表示两者相等;当data1>data2时,输出为1,表示data1比较大;当data2>data1时,输出为2,表示data2比较大。

| data1 | data2 | output |

|---|---|---|

| 00 | 00 | 00 |

| 00 | 01 | 10 |

| 00 | 10 | 10 |

| 00 | 11 | 10 |

| 01 | 00 | 01 |

| 01 | 01 | 00 |

| 01 | 10 | 10 |

| 01 | 11 | 10 |

| 10 | 00 | 01 |

| 10 | 01 | 01 |

| 10 | 10 | 00 |

| 10 | 11 | 10 |

| 11 | 00 | 01 |

| 11 | 01 | 01 |

| 11 | 10 | 01 |

| 11 | 11 | 00 |

2、比较电路程序

module Comparer(input wire[1:0] data1,

input wire [1:0]data2,

output wire [1:0]result );

reg [1:0] result1;

always @* begin

result1=2'b11;

case({data1,data2})

0000,0101,1010,1111: result1=2'b00;

0001,0010,0011,0110,0111,1011: result1=2'b10;

default: result1=2'b01;

endcase

end

assign result=result1;

endmodule

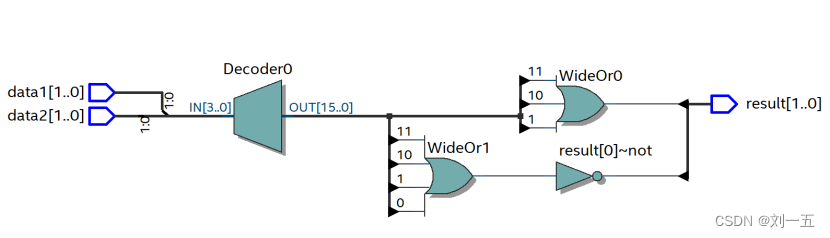

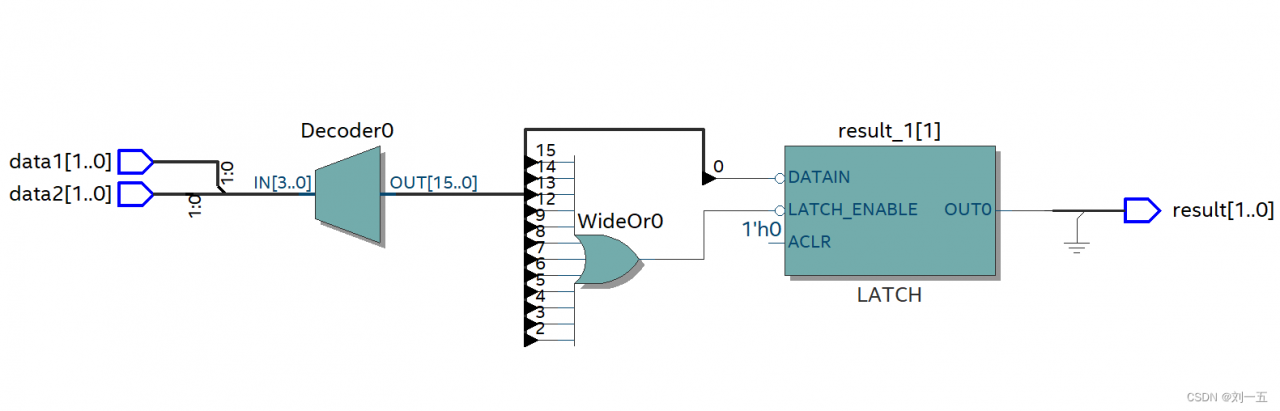

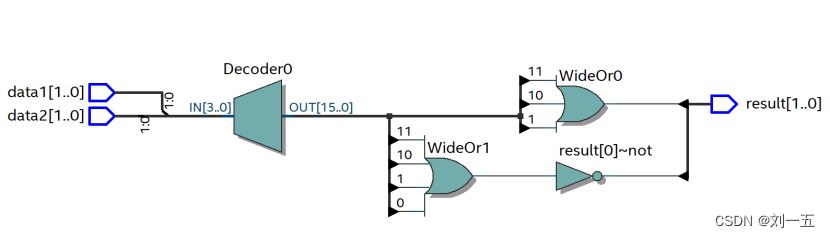

3、RTL图

由上述程序得到的RTL图如下所示:

4、测试程序

`timescale 1ns/100ps

module tb_Comparer;

reg clk;

reg [3:0]data_pro;

reg[1:0]data_1,data_2;

wire [1:0]result_1;

parameter PERIOD=10;

always #(PERIOD/2) clk=~clk;

initial begin

clk=0;

data_1=2'b00;

data_2=2'b00;

data_pro=4'b0000;

# 160 $stop(2);

end

always @(posedge clk) begin

data_pro=data_pro+1;

data_1={data_pro[1],data_pro[0]};

data_2={data_pro[3],data_pro[2]};

$display(data_1,data_2);

end

Comparer Com_1(.data1(data_1),.data2(data_2),.result(result_1));

endmodule

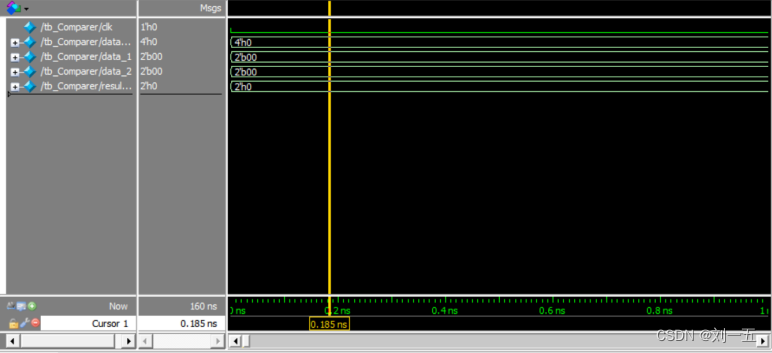

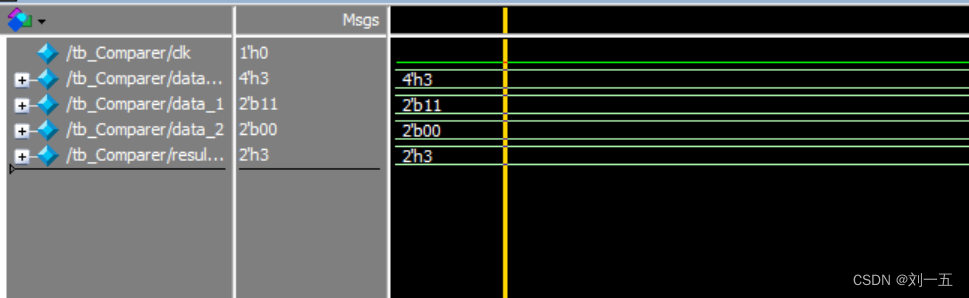

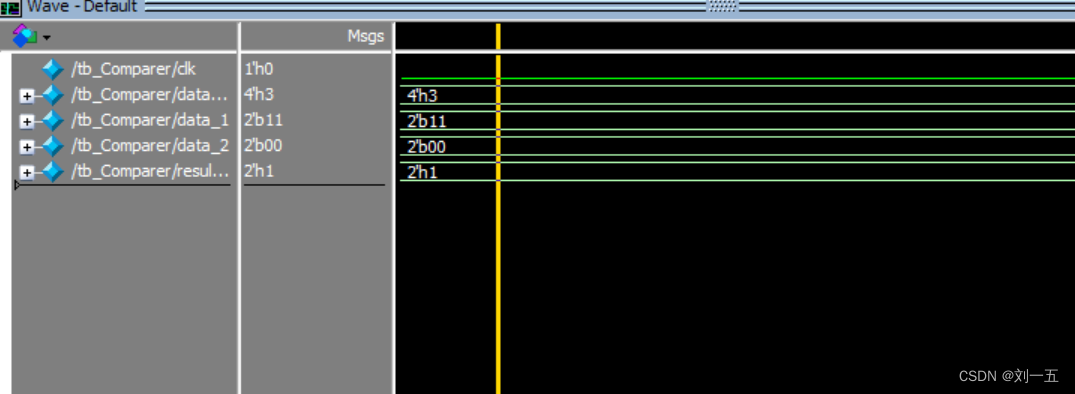

5、仿真结果

当输入data_1=data_2时,输出为0。如下图,当输入data_1=00,data_2=00,输出为0。

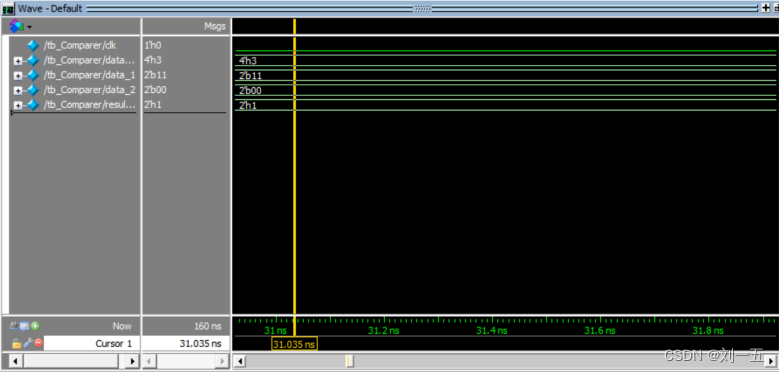

当输出data_1>data_2时,输出为1,表示第1个数据比较大。如下图,当输入data_1=11,data_2=00,输出为1。

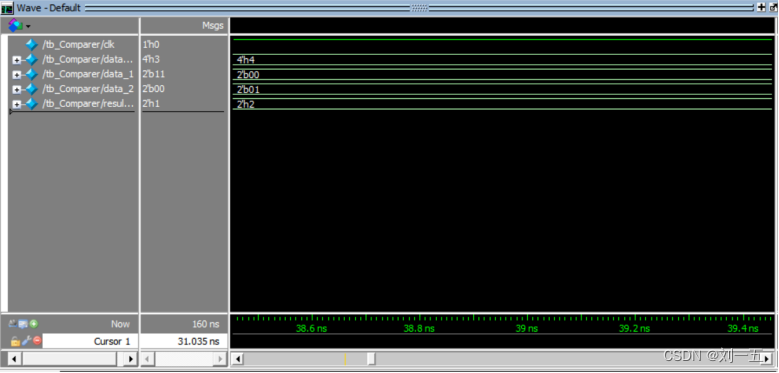

当输出data_2>data_1时,输出为2,表示第2个数据比较大。如下图,当输入data_1=00,data_2=01,输出为2。

6、完成本设计时的错误总结

(1)无法生成RTL错误

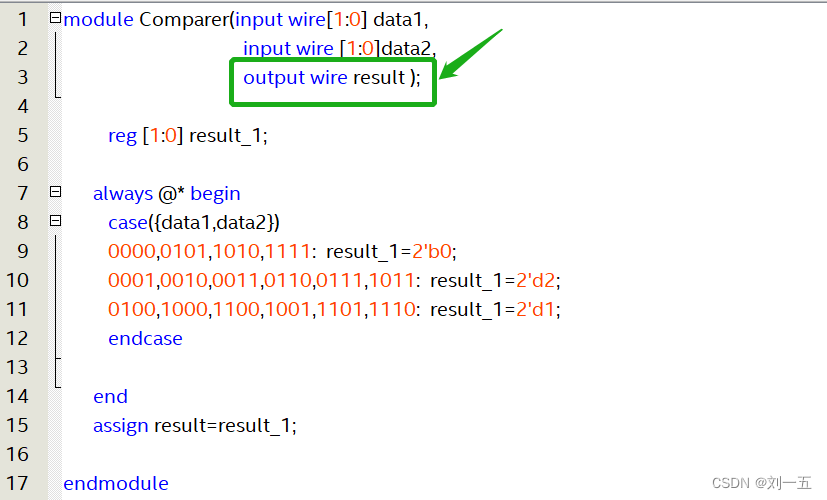

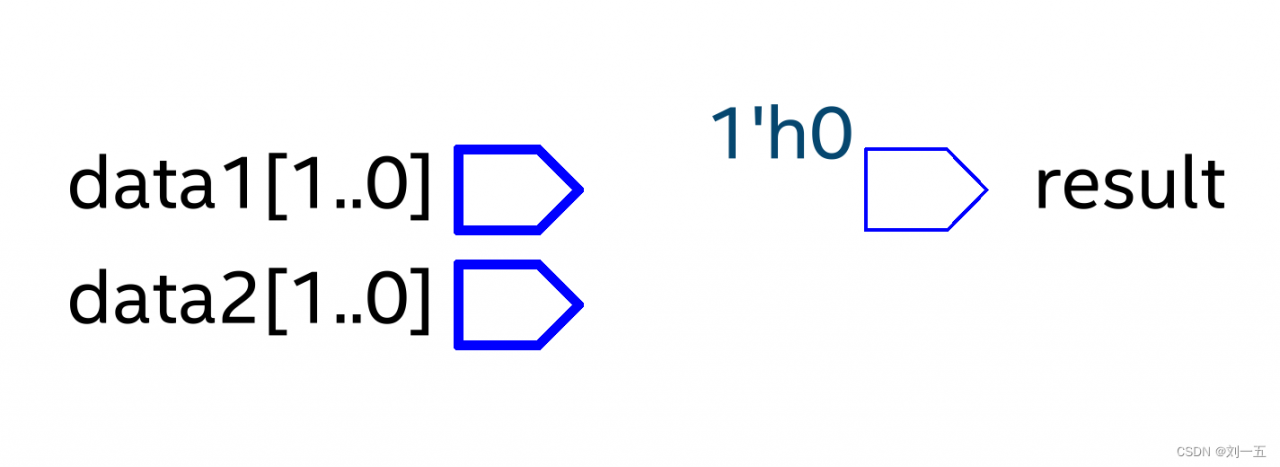

编译的时候不会有语法报错,但是无法生成RTL图。原因是没有给输出wire参量标定位数。

没有给输出参量标定位数,产生的RTL图如下:

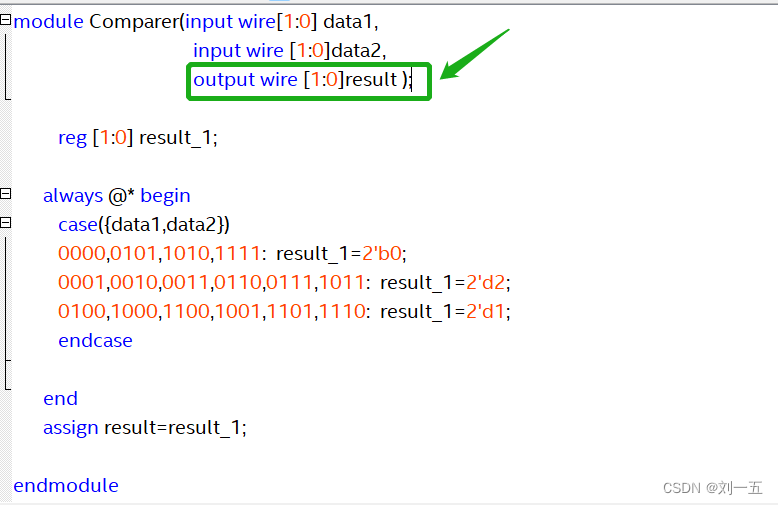

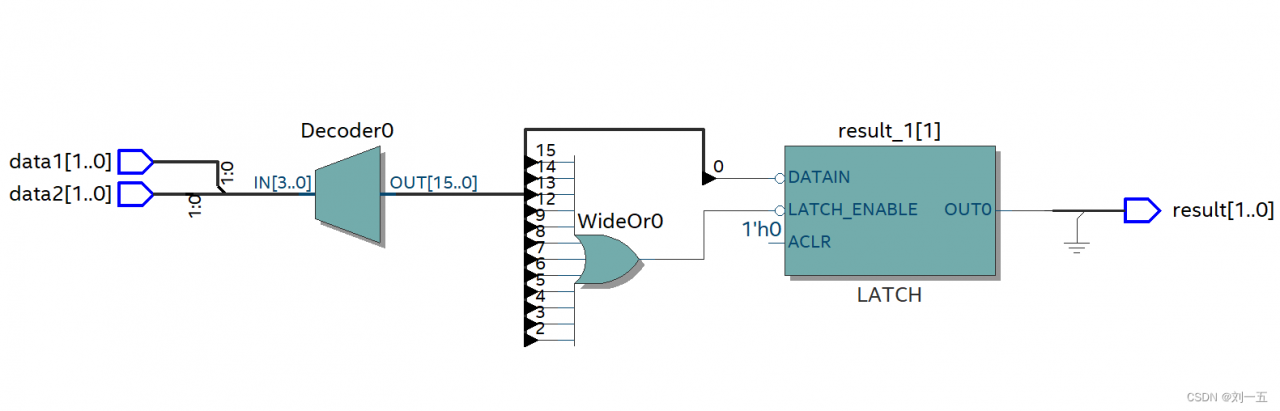

标定输出参量的位数之后,产生的RTL图如下:

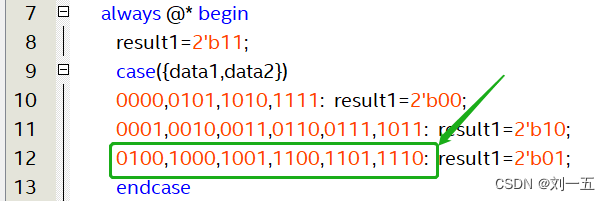

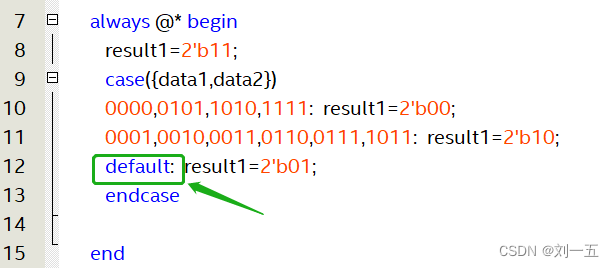

(2)case语句输出错误

错误现象:在输入是1100,也就是case3的情况下,输出应该是01,实际输出是11。也就是说没有执行到这个case里面去。发现解决方法是修改case3的所有情况为default,有点玄学😂

修改为default,便成功得到预期的结果:

其次,可以看到修改default前后RTL图还是不一样的,下次还是直接写default就好了😏

Forever young,always tearful. 😏

版权声明:本文为Jessaly原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接和本声明。