3.2.基于FPGA的原型设计流程概述

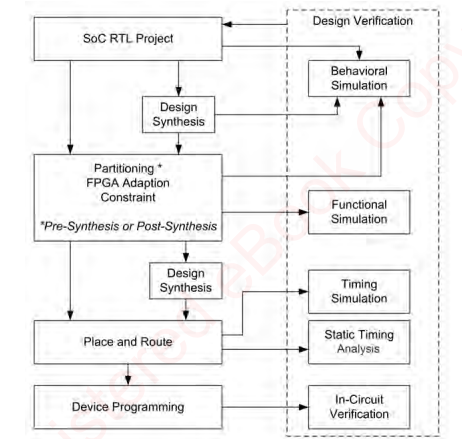

图26显示了我们在基于FPGA的原型化过程中所遵循的基本流程:让我们依次快速查看这些步骤。

-

综合:

可以在分割之前或分割之后进行。将RTL转换为FPGA网列表的过程

。综合过程为所选设备生成一个FPGA网列表,以及FPGA后端工具将使用的实现约束。此外,一些综合工具提供了对预期性能的早期估计,这允许用户在可能漫长的后端过程中花费任何时间之前对设计或约束进行更改。 -

针对FPGA的设计适应:在这一步中,SoC RTL的设计被修改,以更好地适合FPGA技术和特定的原型平台。

对SoC RTL的典型修改包括删除没有原型的块,用时钟生成和其他IP等FPGA结构替换一些SoC特定的结构,以及调整内存等块的大小以更好地适合FPGA。

-

分区:**分区:将SoC RTL设计的FPGA-ready版本被划分为映射到单个fpga的块的过程。**这一步对于不适合于单个FPGA的设计是必需的。分区可以手动或使用分区工具来完成。第3章探讨了一些划分的方法。

-

约束生成:**这是流中的一个方便的点,可以进入各种实现约束,如时间和针脚位置。**虽然在综合后可能会产生约束并应用于后端工具,但在综合步骤之前这样做可以使综合产生一个FPGA网表,更优化,以满足位置和路线后的面积/速度约束。

-

布局布线:

将FPGA网络列表和用户约束转换为FPGA位流的过程

版权声明:本文为weixin_45264425原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接和本声明。