目录

序言

在之前的分享

中,讨论了如何利用网络分析仪(以下简称“网分”)的并联

–

直通法完成电源系统的

PDN测量(文章链接:

电源完整性的PDN测试与仿真_一只豌豆象的博客-CSDN博客

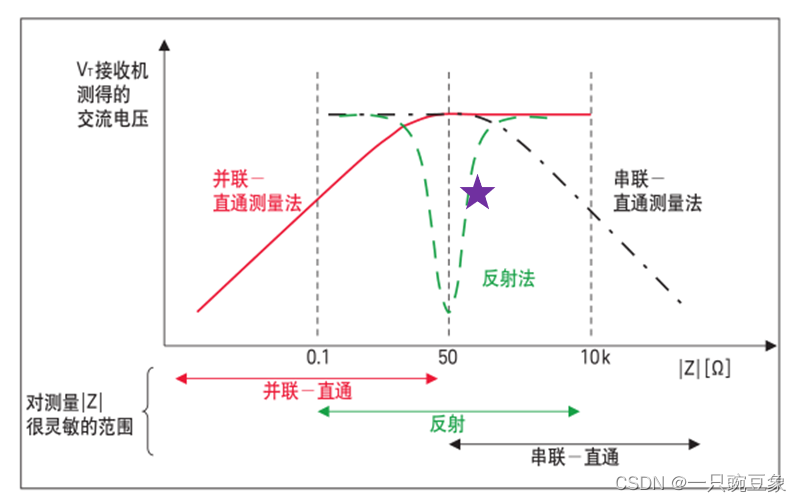

),其中,也提到过反射法的典型应用是测试铁氧体磁珠的阻抗曲线,在实际产品设计中,确实也大量存在这样的测试需求,举例来说,用过车载相机的工程师对SerDes

电路上的

PoC

网络肯定不会陌生,对于该网络的一个重要评估方式就是阻抗曲线的测量,因为对于该网络的阻抗设计要求往往介于

1000~3000

欧姆之间,如下图所示,大致处于紫色五角星所在的区域,因此,尚可以用最简单的反射法进行测量。

反射测量法之所以简单,是因为其仅仅需要一路网分的端口,进行回波损耗的测量即可完成,其阻抗等效计算公式已经在PDN的文章中介绍过,未来,小编还会专门撰写一篇文章,去详细讨论下,网络分析仪工作以及公式的推导过程,敬请期待!

PoC

电路设计

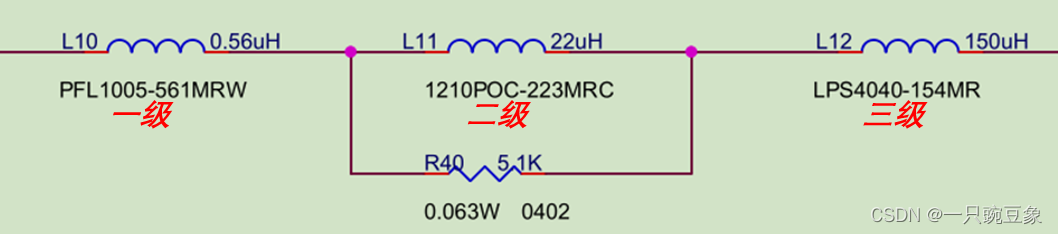

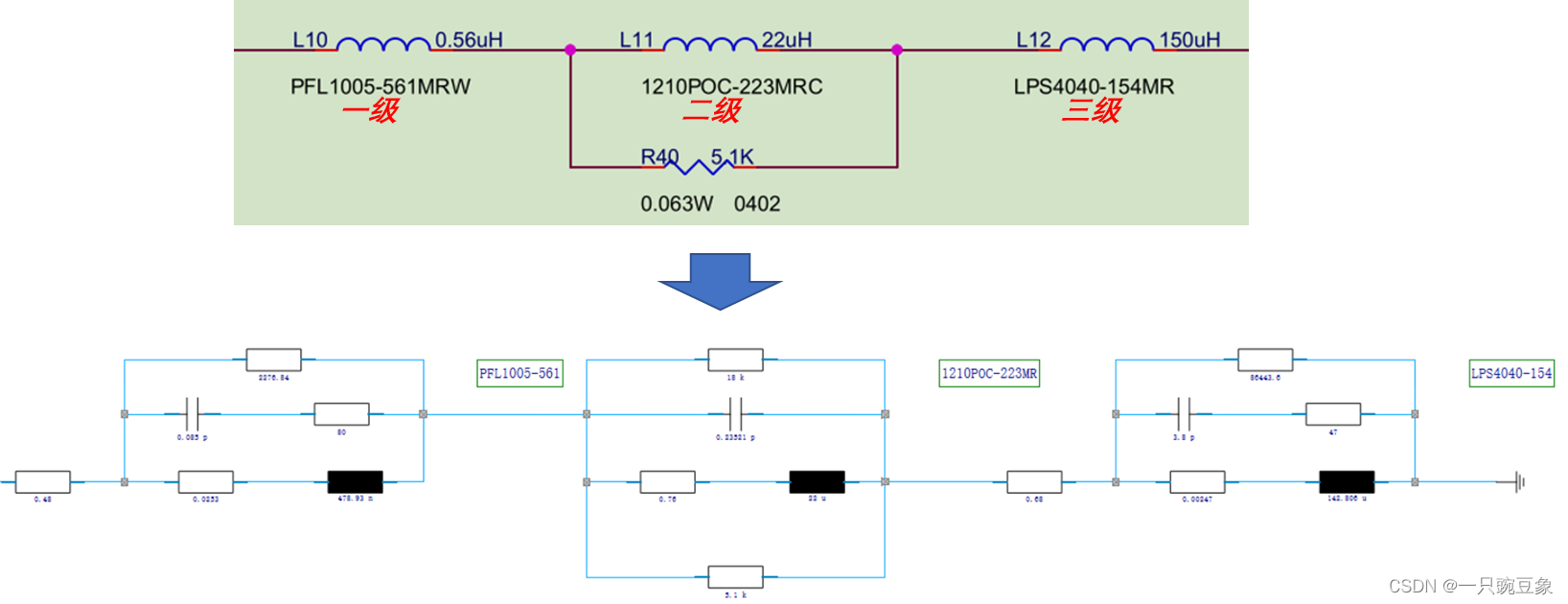

言归正传,举例来说,设计中,采用了如下图所示的PoC

网络电路设计,可以看出,采用的是

Coilcraft

的电感组合,总共分为三级:二级电感处的并联电阻,是为了使得整体的随频率变化的阻抗曲线更为平稳(电感在其谐振峰值处的电阻值往往非常大);

由于Coilcraft

未直接提供具体的元件仿真模型,比如

spice

或

touchstone

文件,因此,需要根据其官网提供的参数信息,手工完成电感的参数化建模;

模型来源:一级和三级电感的参数,均可在官方的spice model

指导手册中找到,二级电感则没有该数据,小编只能按照通用的电感等效模型对其进行估算,需要说明的一点,不论是哪种计算,都只能是针对某一个具体频点的计算结果,所以,计算值与实测值必然存在一定的偏差;

官方数据链接如下,感兴趣的小伙伴可以自行查阅:

PFL1005 Series Shielded Power Inductors |

Coilcraft

1210PoC Series PoC (Power over Coax) Injection Chokes |

Coilcraft

LPS4040 Series Low Profile Shielded Power Inductors |

Coilcraft

参数

化建模方法

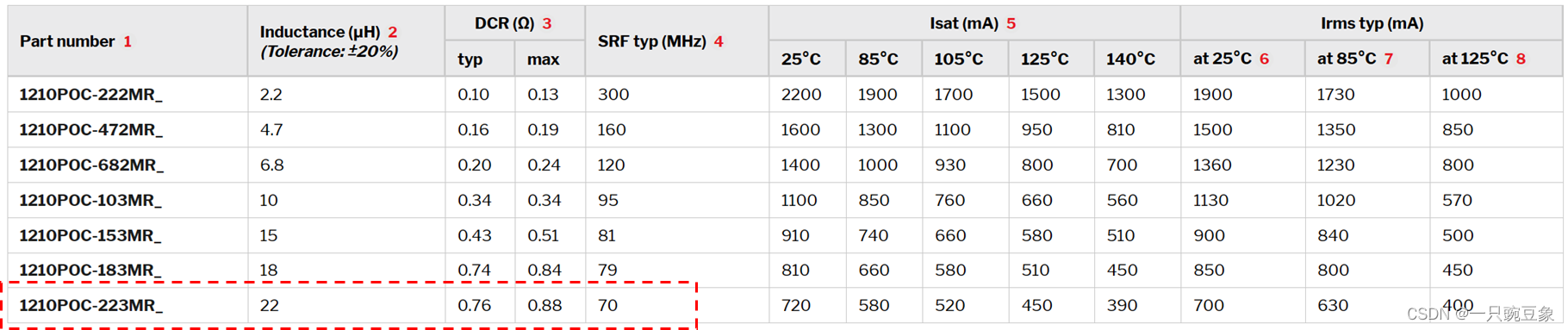

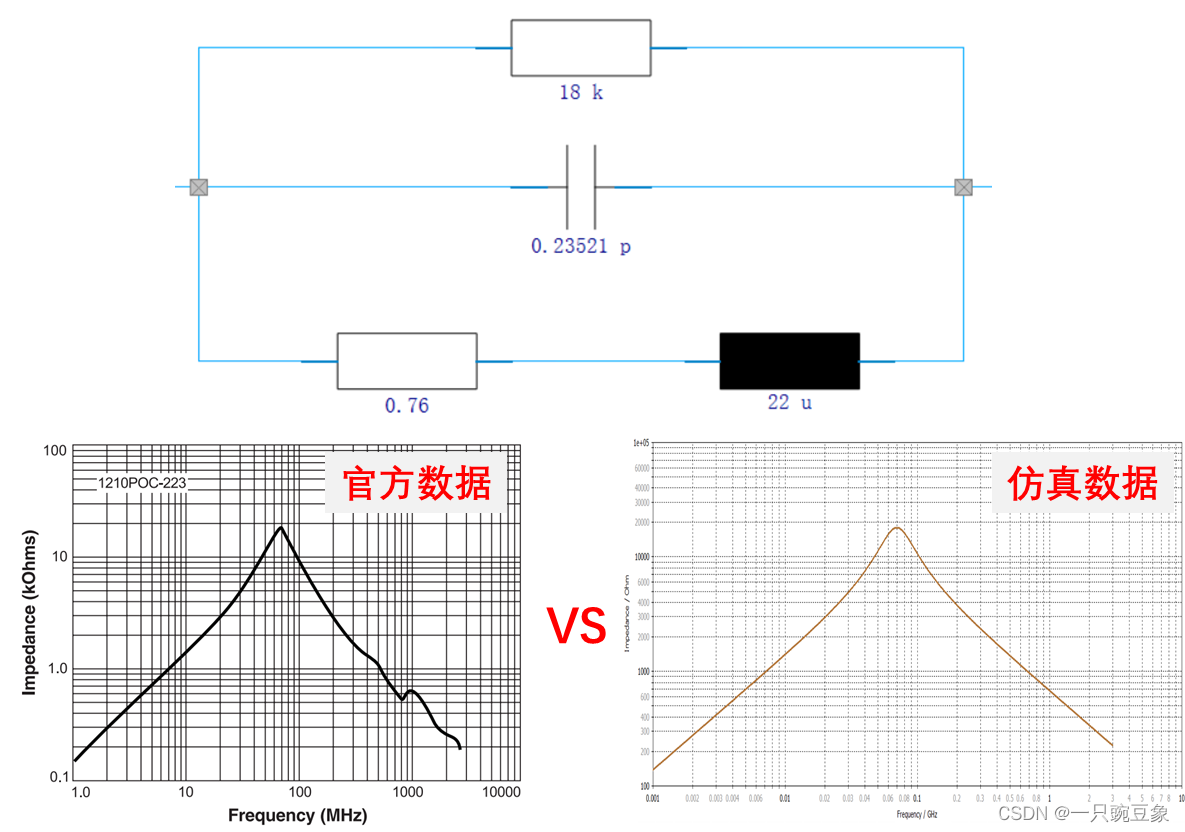

以1210POC-223MRC

为例,首先,通过官网,可以获取到电感标称值、直流等效电阻值及谐振点频率,然后,根据谐振公式计算得到分布电容值,最后,通过查看其阻抗曲线图,获取谐振峰值处的电阻值,从而,完成所有分布参数值的引入;

最后的数据对比效果如下图所示,只有在高频处的波动无法体现出来,谐振点及其附近的趋势还是较为一致的。

按照上述的方法,最终的PoC网络参数化建模如下图所示:

测试环境

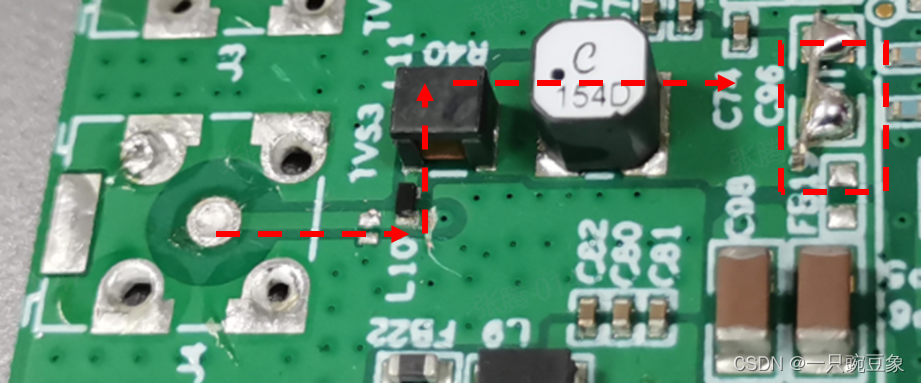

实际产品如下图所示,由于是单端口网分测试,需要将SerDes

信号内部走线割断,仅保留连接器到

PoC

电感这段走线(如图中红色虚箭头所示),并且,三级电感输出的地方,做对地短接处理,如图中红色虚线框所示;

然后如下图所示,完成连接器处的SMA

测试端口的焊接,最好用热风枪进行焊接以保证焊点的牢靠性(焊接之前,不要忘记在网分上完成该端口的延伸校准,至于这段短截线的长度,当然越短越好,或者按照

≤1/15*

最高工作波长进行考虑,或者校准完后通过观察史密斯圆图上开路曲线效果而定

);

仿真环境

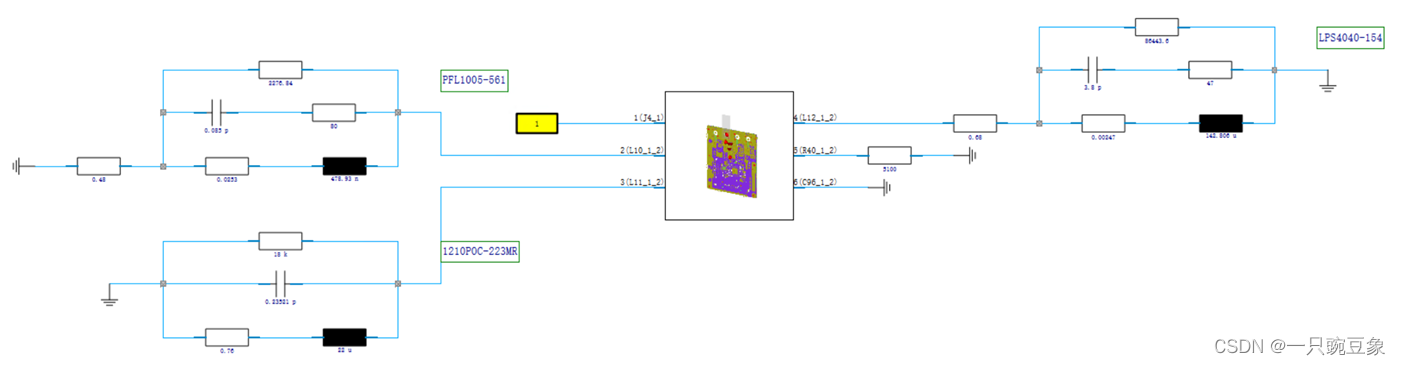

与此同时,小编利用CST MWS

微波

工作室,对测试用的

PCB

进行

3D

建模(之所以用三维建模,是为了提高

S

参数的准确度),并利用电路协同仿真环境,完成对测试台架的模拟;

结论

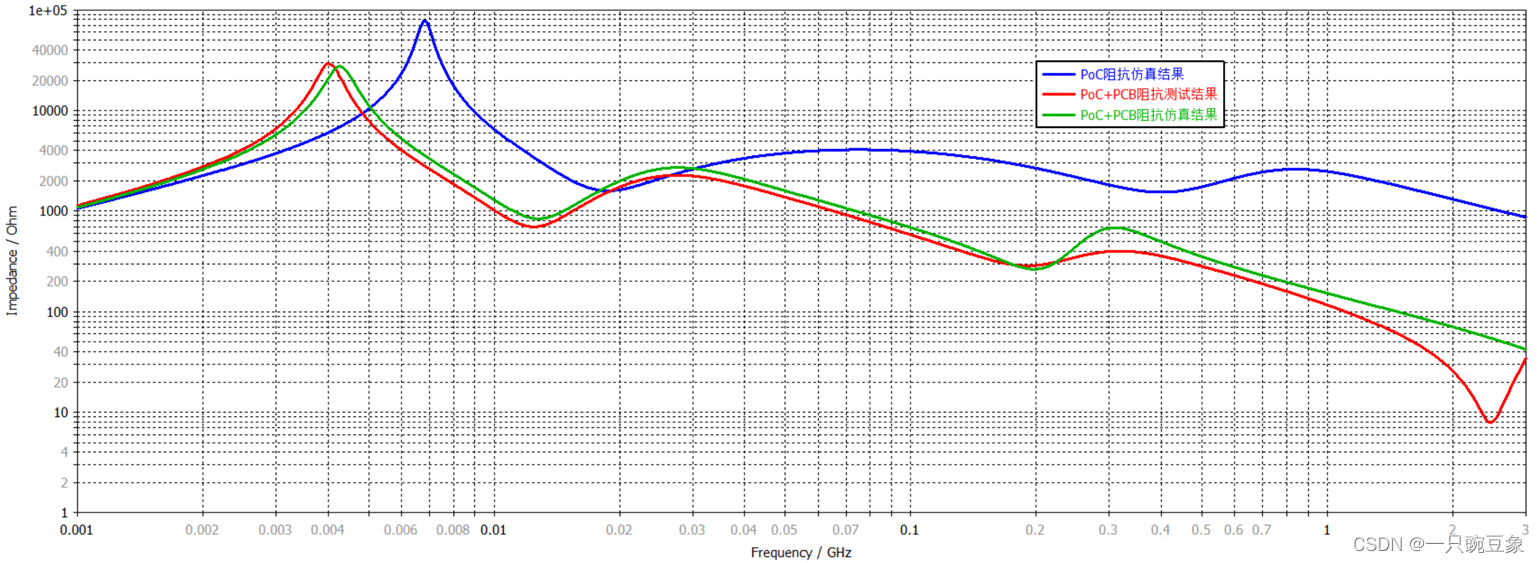

最终的仿真与测试结果对比如下,从效果来说(红色与绿色实线相比),达到了预期的趋势上的匹配度,要知道,电感的模型都是单个频点等效出来的,所以存在一定的偏差是合理的(并且知道偏差更多地出现在高频处);

但是,也可以观察到,与单纯的电感组合效果相比(蓝色实线),PCB

的特性阻抗影响是非常显著地,尤其在高频处;

因此,接下来,就可以利用仿真完成后期的

PCB

优化,实际操作时,小编发现,同样是

PCB

的特性阻抗影响,高频处欲将阻抗控到千欧级几乎是不可能的,此时,就需要通过其它的评估手段来进行整体的设计评估(小编后期也确实做了更多的关于

SerDes

链路的仿真及测试验证,基本可以保证在仿真环境下,达到仿真与测试结果的一致,如果感兴趣,可以留言进行讨论);

最后,小编想说,只有将仿真与测试紧密结合起来,才可以

有效地提高硬件研发阶段的设计可靠性;