1. DAC6004手册研读

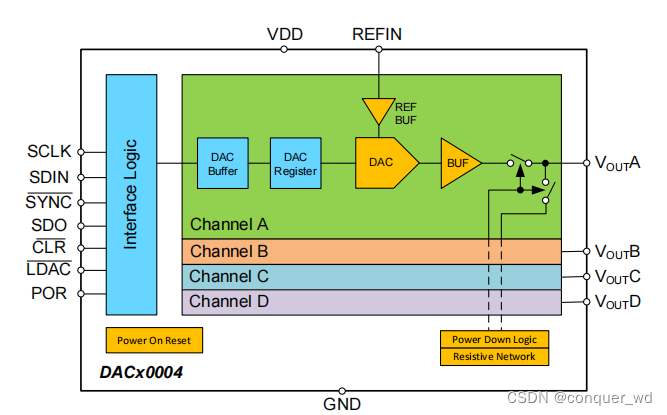

DAC6004相对比较简单,有4个配置通道,配置过程中使用的主要信号有SCLK 、SDIN、SDO、SYNC、LDAC以及通道的配置输出。

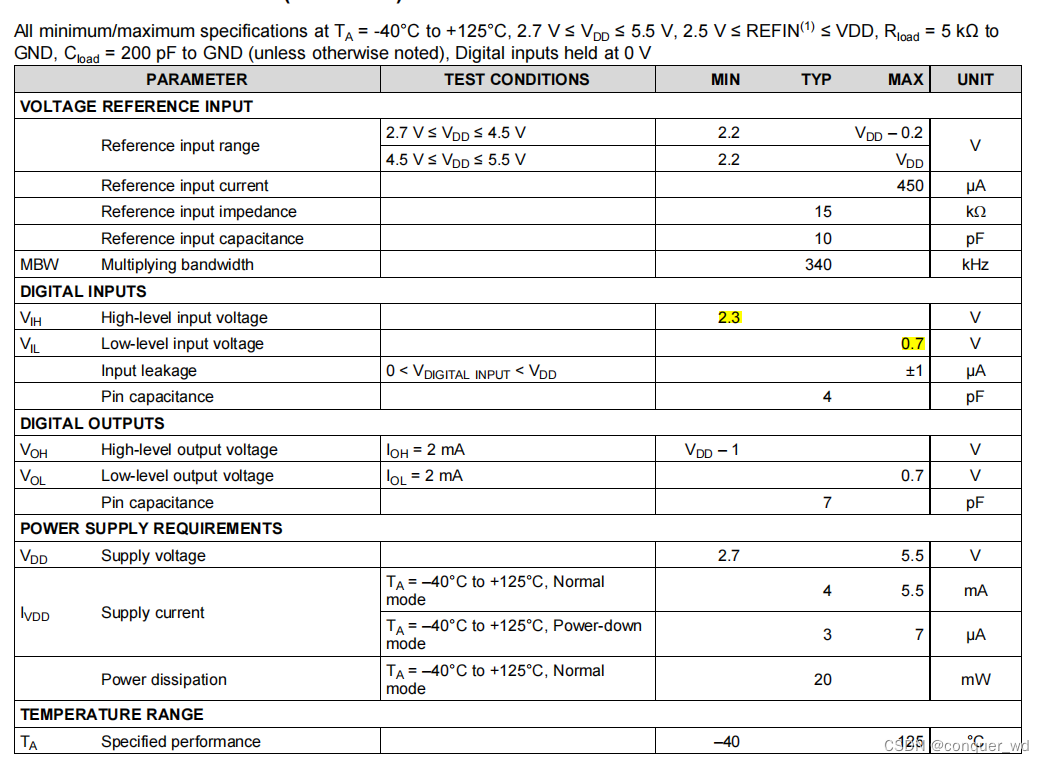

1.1 DAC6004数字端电压要求

此处相对还是比较重要,因为牵扯到DAC数字端输入的最低和最高的电压要求,即要求DAC输入电压必须高于2.3v才可以表示某一个信号为高,低于0.7v才可以驱动信号为低电平,如下图黄色部分中,表示了DAC的驱动电压要求。

1.2 DAC6004一些时间要求(重要)

下表列出了DAC6004一些时间的要求,特别需要注意的,比如说tw1,tw4,t20;

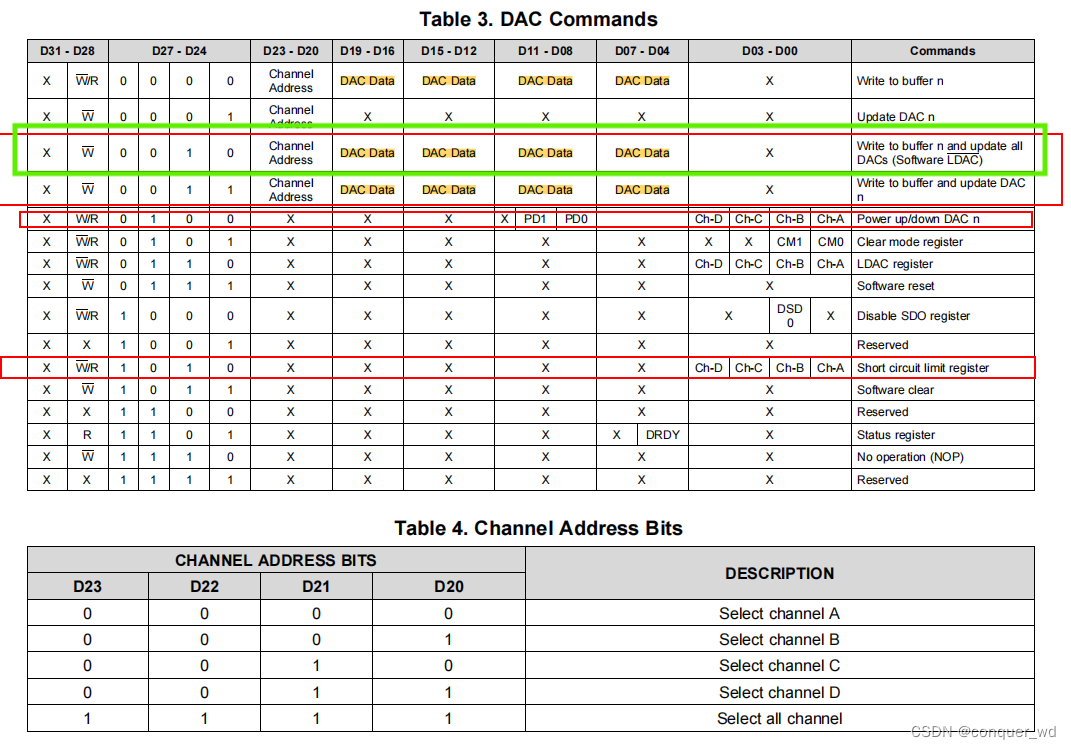

1.3 DAC6004配置命令

DAC6004一共有4个channel,每个channel配置的最大电压范围为0~REFIN,使用其实相对比较简单, 此处我采用绿色部分的配置命令,仅配置了chan0和chan1,可以用示波器抓到所需的电压输出,尝试去回读时候没有回读成功,如果有老铁在学习或者研究过程中,回读成功的话,麻烦还望告知下;

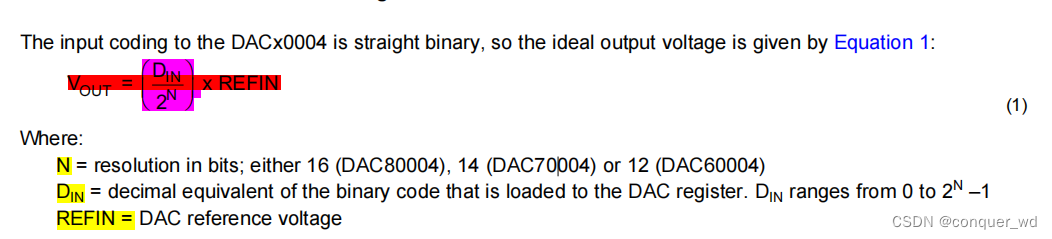

1.3 DAC6004输出电压计算

1.4 DAC6004关键管脚说明

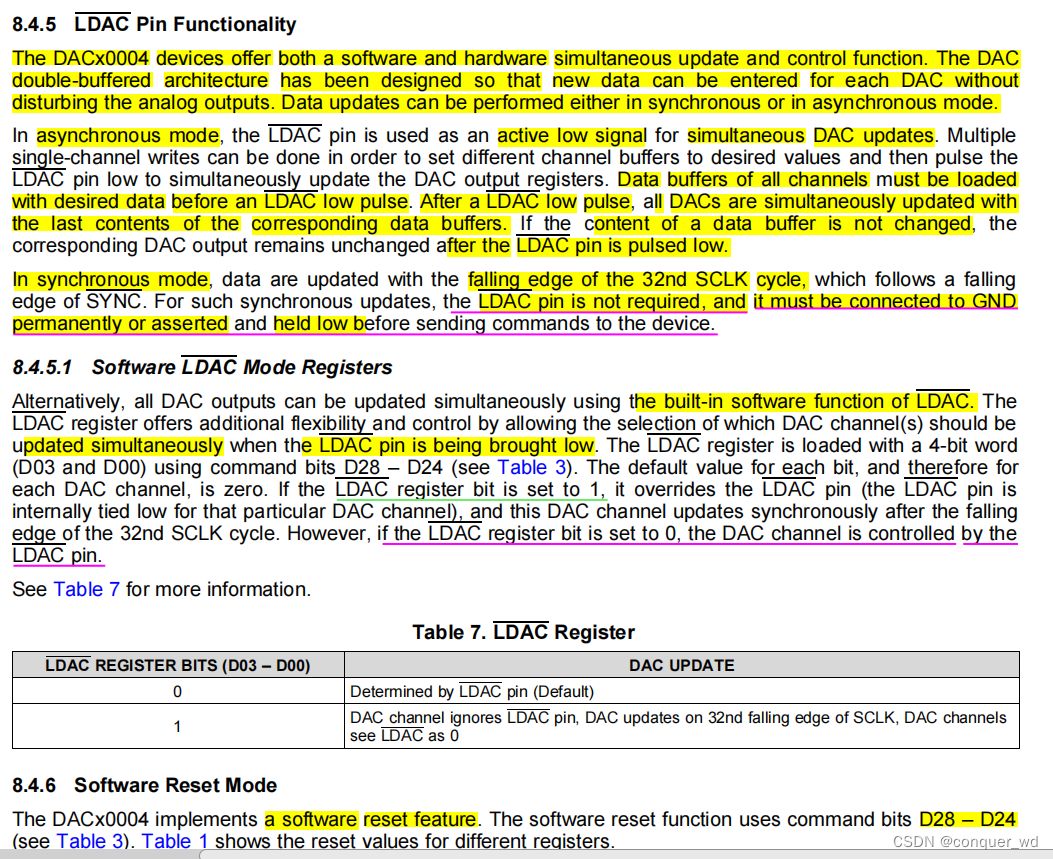

(1)LDAC管脚: 有同步模式和异步模式,与硬件连接有关系,同步模式下硬件上必须要将LDAC管脚接地;异步模式下,当对DAC配置完成之后,等指定的时间,然后拉低LDAC管脚,既可更新对应的chan值。

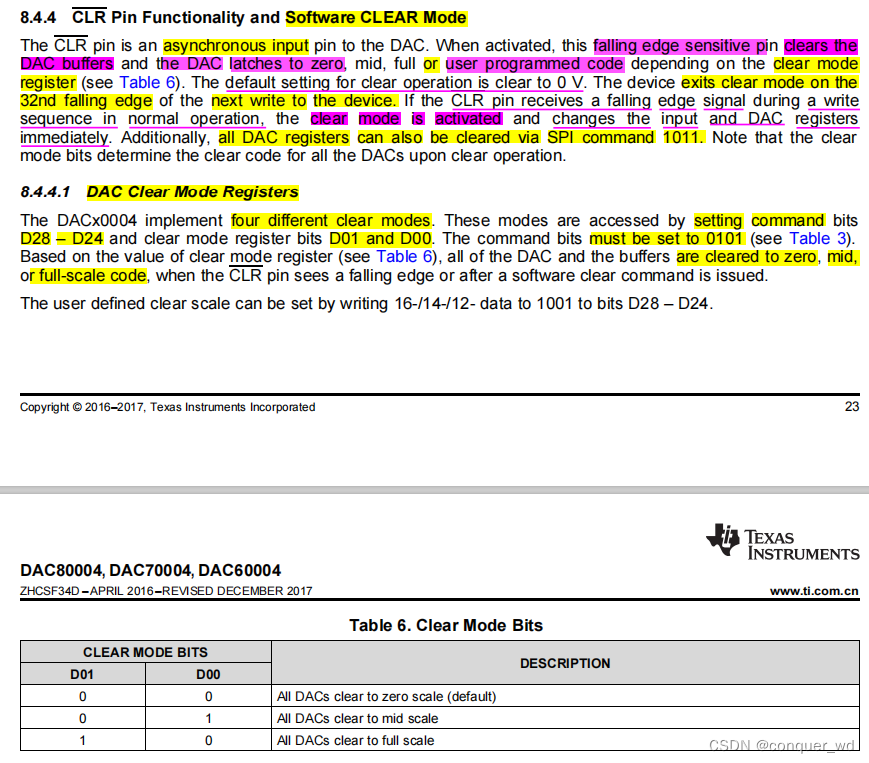

(2)CLR管脚:该管脚得作用是用来清除当前chan输出的电压到指定的电平,至于当拉低这个管脚之后chan的输出状态是多少与CLR寄存器的配置有关系,默认是清0

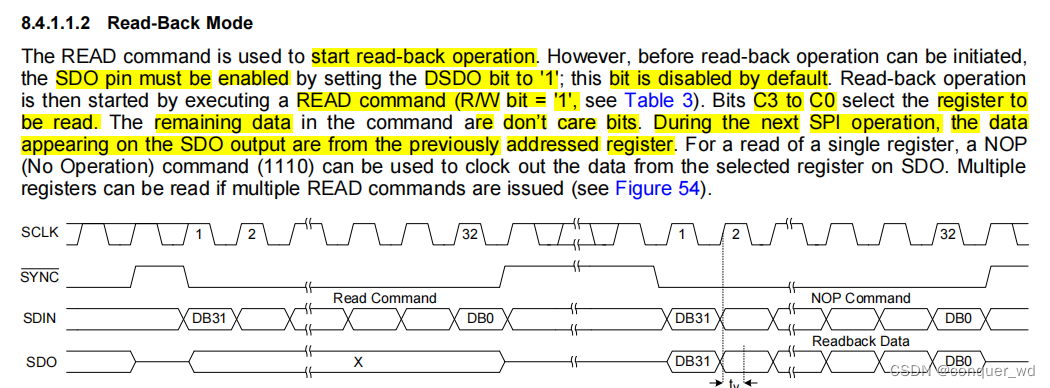

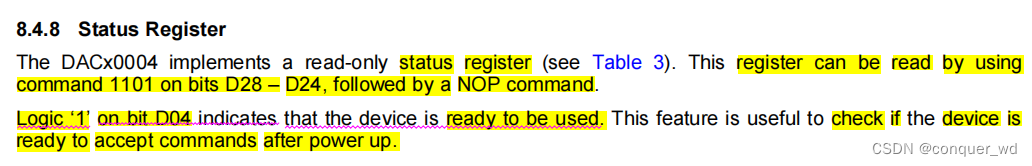

1.4 DAC6004状态回读以及读时序

回读没有读成功,有回读成功的老铁还望告知,感谢感谢!!

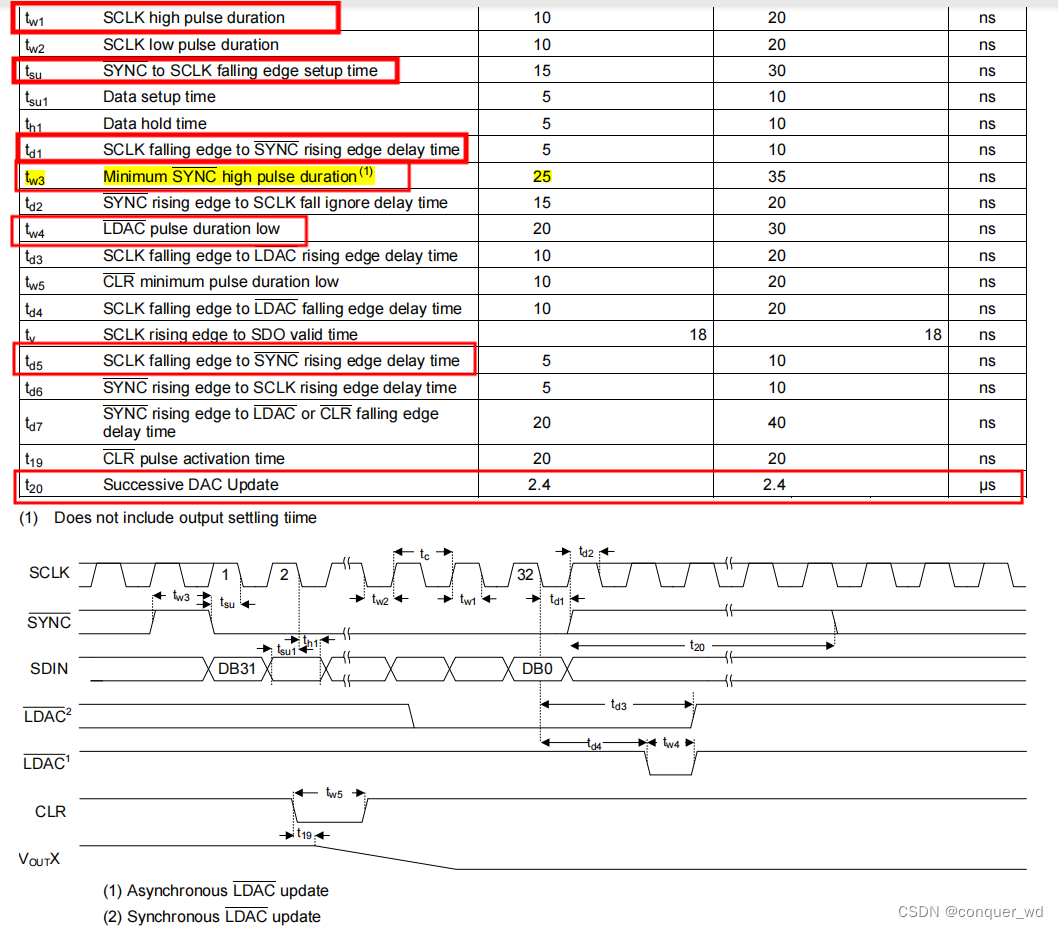

2. DAC6004 SPI配置时序解释

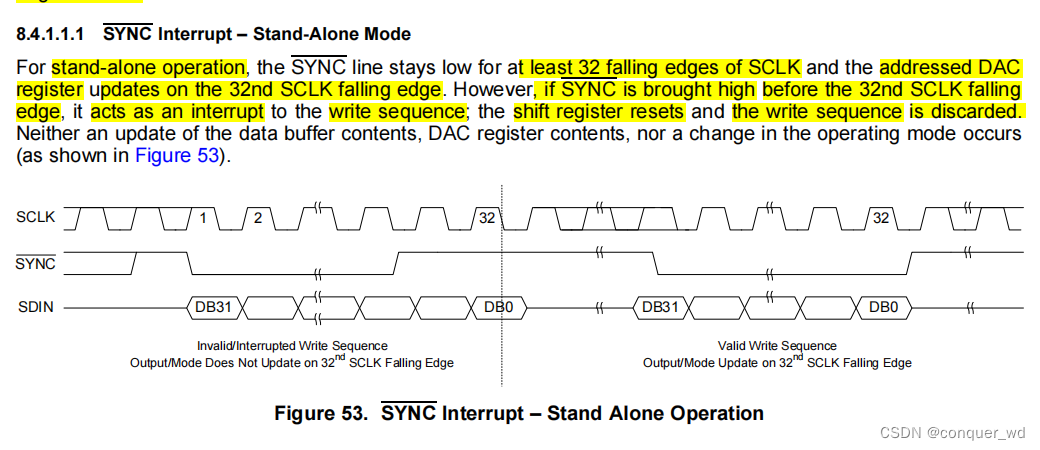

下图解释了关于DAC6004的配置时序,前半部分是配置有问题的时序,后半部分是配置ok的时序,如果在数据并串转换的过程中,串行数据没有发送完成,就拉高了SYNC则此包数据会被丢弃,SYNC拉高相当于是一个中断信号。

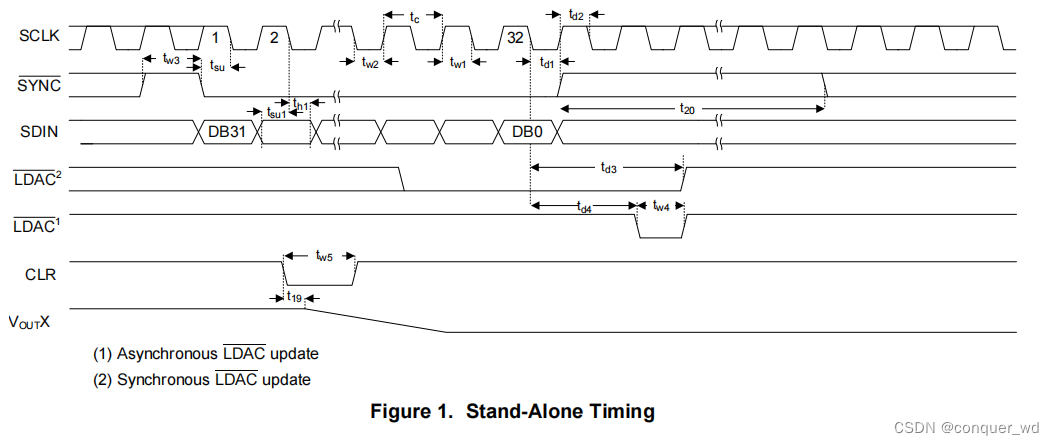

下图是正常的传输时序,第一个DB31时,在SYNC下降沿就要将数据发出,在1 的SCLK下下降沿对DB31进行采样,在SCLK的上升沿去更新DB30,同理在32个SCLK的上升沿去更新DB0的数据,在32个SCLK下降沿去采样DB0的数据,当数据更新完成之后,等一段td4去拉低LDAC,更新chan的值。表示一个chan的更新完成。 如果有多个通道需要更新的话,即假如多个32bit的配置数据需要更新,则更新完多个32bit的配置数据之后,然后等td4拉低LDAC更新所有通道的值,但是要注意每个chan(即每个32bit配置数据)之间的时间间隔要求。

注释:由于项目比较赶,有些方面也搞的不是很清楚,比如说状态回读这个功能,有时候可以读成功有时候不成功,如果有问题之处还望老铁们指正,对读有研究比较透彻的同志,还望告知,多谢哈