一、组合逻辑电路与时序逻辑电路

组合逻辑电路:

任意时刻的输出仅仅由该时刻的输入决定,与电路当前的状态无关

。

时序逻辑电路:

任意时刻的输出不仅由该时刻的输入决定,还与电路当前的状态有关

。

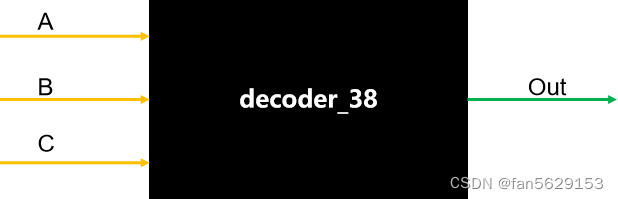

二、38译码器的工作原理

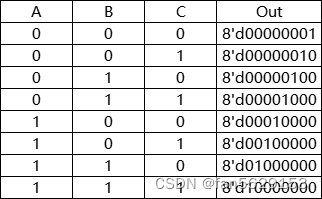

表①、38译码器真值表

3种输入状态翻译成8种输出状态。

三、Verilog代码实现

源码:

module decoder_38 (

a,b,c,data

);

input wire a;

input wire b;

input wire c;

output reg [7:0]data;

always @( a,b,c) begin

case ({a,b,c})

3'd0: data=8'b0000_0001;

3'd1: data=8'b0000_0010;

3'd2: data=8'b0000_0100;

3'd3: data=8'b0000_1000;

3'd4: data=8'b0001_0000;

3'd5: data=8'b0010_0000;

3'd6: data=8'b0100_0000;

3'd7: data=8'b1000_0000;

endcase

end

endmodule

testbench:

`timescale 1ns/100ps

module decoder_38_tb ;

reg a;

reg b;

reg c;

wire [7:0]data;

decoder_38 decoder_38_0 (

.a(a),

.b(b),

.c(c),

.data(data)

);

initial begin

a=0;b=0;c=0;

#200;

a=0;b=0;c=1;

#200;

a=0;b=1;c=0;

#200;

a=0;b=1;c=1;

#200;

a=1;b=0;c=0;

#200;

a=1;b=0;c=1;

#200;

a=1;b=1;c=0;

#200;

a=1;b=1;c=1;

#200;

$stop;

end

endmodule

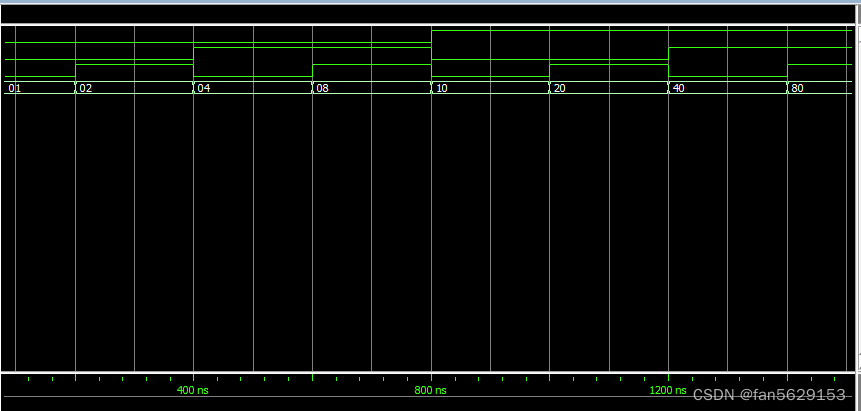

三、仿真模拟

版权声明:本文为fan5629153原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接和本声明。