参考:IS62WV51216ALL数据手册 W9825G6KH数据手册

1.SRAM

静态随机存取存储器(Static Random-Access Memory,SRAM)是随机存取存储器的一种。相对之下,动态随机存取存储器(DRAM)里面所储存的数据就需要周期性地更新。然而,当电力供应停止时,SRAM储存的数据还是会消失(被称为volatile memory),这与在断电后还能储存资料的ROM或闪存是不同的。STM32内部有SRAM和FLASH作为内存和程序存储空间,但当程序比较大的时候就需要在芯片外部扩展存储器,可以使用FSMC方式将SRAM外扩作为内存。

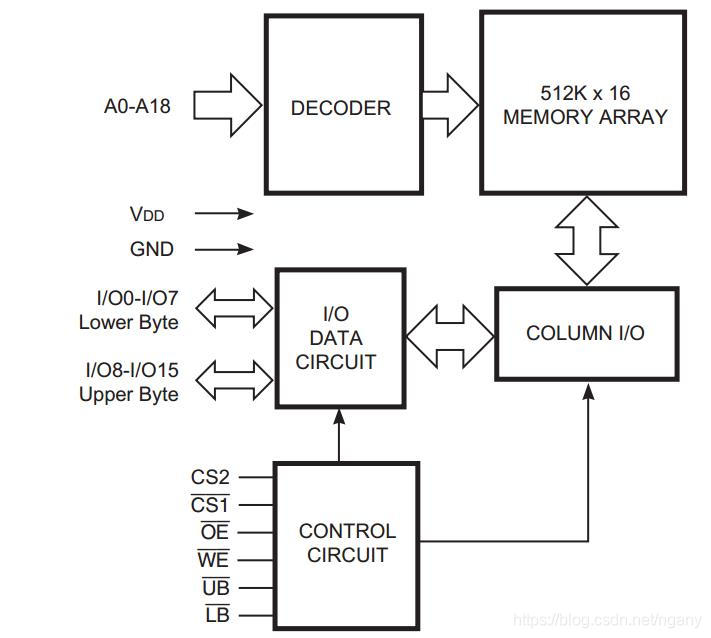

1.1芯片引脚说明

| A0-A17 | Address Inputs | 地址线 |

| I/O0-I/O15 | Data Inputs/Outputs | 数据线 |

| CS1 | Chip Enable Input | 芯片使能 |

| OE# | Output Enable Input | 输出使能(读使能) |

| WE# | Write Enable Input | 写使能 |

| LB# | Lower-byte Control (I/O0-I/O7) | 低八位使能 |

| UB# | Upper-byte Control (I/O8-I/O15) | 高八位使能 |

| NC | No Connection | 无效连接 |

| VDD | Power | 电源 |

| GND | Ground | 地 |

在SRAM 中,排成矩阵形式的存储单元阵列的周围是译码器和与外部信号的接口电路。存储单元阵列通常採用正方形或矩阵的形式,以降低整个芯片面积并有利于数据的存取。以一个存储容量为1MB位的SRAM为例,共需19条地址线来保证每个存储单元都能被选中(2^19 =512K,每个存储单元的数据是16位的)。IS62WV51216芯片是不需要列地址的。

1.2从Dout引脚读取1bit数据须要下面的步骤:

1)通过地址总线把要读取的bit的地址传送到对应的读取地址引脚(这个时候/WE引脚应该没有激活,所以SRAM知道它不应该运行写入操作)。

2)激活/CS选择该SRAM芯片。

3)激活/OE引脚让SRAM知道是读取操作。

第三步之后,要读取的数据就会从DOut引脚传输到数据总线。

1.3从Dout引脚存储1bit数据须要下面的步骤:

1)通过地址总线确定要写入信息的位置(确定/OE引脚没有被激活)。

2)通过数据总线将要写入的传输数据到Dout引脚。

3)激活/CS引脚选择SRAM芯片。

4)激活/WE引脚通知SRAM知道要进行写入操作。

经过上面的四个步骤之后,须要写入的数据就已经放在了须要写入的地方。

1.4SRAM时序说明

读时序

写时序

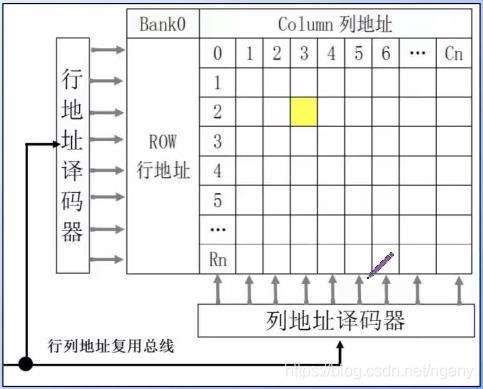

2.SDRAM

SDRAM(Synchronous Dynamic Random Access Memory),同步动态随机存储器。同步是指内存工作需要同步时钟,内部的命令的发送与数据的传输都以它为基准;动态是指存储阵列需要不断的刷新来保证数据不丢失;随机是指数据不是线性依次存储,而是自由指定地址进行数据读写。

SDRAM的内部是一个存储阵列,你可以把它想象成一张表格。我们在向这个表格中写入数据的时候,需要先指定一个行(Row),再指定一个列(Column),就可以准确地找到所需要的“单元格”,这就是SDRAM寻址的基本原理。

SDRAM总存储容量 = L-Bank的数量×行数×列数×存储单元的容量

W9825G6KH这一款SDRAM的内存 = 4×2^13×2^9×16 = = 256Mbit,即32MB。

| 时钟 | CKE | 时钟有效信号 |

| CLK | 时钟信号 | |

| 地址线 | A0-A12 | 行地址13位,列地址9位 |

| BA0,BA1 | Bank选择,共有4个Bank | |

| 数据线 | I/O0 – I/O15 | 数据传输 |

| 控制命令 | CS# | 芯片选择 |

| WE# | 写使能(低电平写,高电平读) | |

| RAS# | 行地址选通 | |

| CAS# | 列地址选通 |

| 初始化 | 输入稳定期 |

| 所有L-Bank预充电 | |

| 8个刷新周期 | |

| 模式寄存器设置 |

| 读写 | 行激活 |

| 列读写 | |

| 预充电 | |

| 刷新 |

模式寄存器在默认开机状态未指定。需要遵循以下电源启动和初始化顺序,以确保设备预先适应每个用户的特定需求。

在通电期间,当输入信号处于“NOP”状态时,所有VDD和VDDQ引脚必须同时升高到指定的电压。任何输入引脚或VDD电源电压不能超过VDD + 0.3V。启动后,需要一个200us的输入稳定器,后跟一个预充电指令给所有Bank预充电。为了防止在电源启动期间DQ总线上的数据争用,需要在初始暂停期间将DQM和CKE引脚保持高位。一旦所有的Bank都已预充,须发出模式寄存器设置命令来初始化模式寄存器(MR,Mode Register)。在对模式寄存器进行编程之前或之后,还需要另外8个自动刷新周期(CBR),以确保正确的后续操作。