1 概述

本文用于记录在用xilinx的FPGA时,使用VIVADO编译两个GTP/GTX IP时出现的[DRC RTSTAT-1]错误的问题,并说明问题原因与解决思路。

使用的编译软件:vivado 2017.4

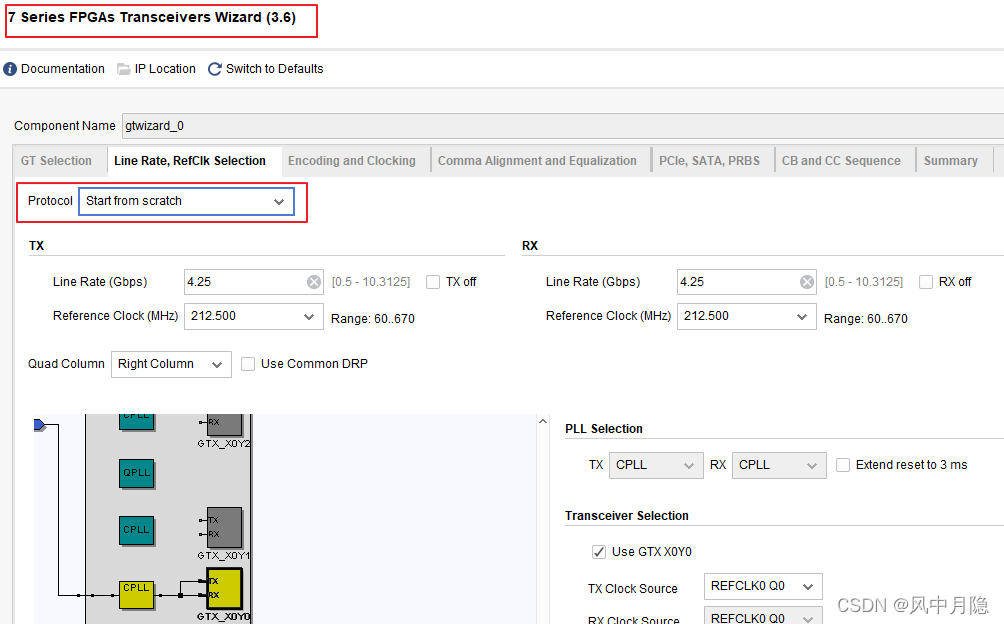

使用的GTP IP:

2 错误具体描述

看error时:

> [DRC RTSTAT-1] Unrouted nets: 4 net(s) are unrouted. The problem

> bus(es) and/or net(s) are

> gtp_top1_inst/gtwizard_0_support_i/common0_i/gt0_qplloutclk_in,

> gtp_top2_inst/gtwizard_2_support_i/common0_i/gt0_qplloutclk_in,

> gtp_top1_inst/gtwizard_0_support_i/common0_i/gt0_qplloutrefclk_in, and

> gtp_top2_inst/gtwizard_2_support_i/common0_i/gt0_qplloutrefclk_in.

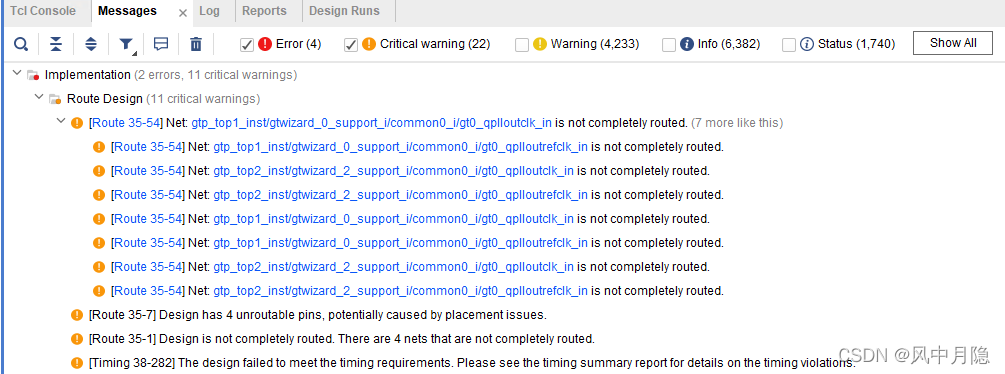

看critical warning:

> [Route 35-54] Net:

> gtp_top1_inst/gtwizard_0_support_i/common0_i/gt0_qplloutclk_in is not

> completely routed.

3 错误分析

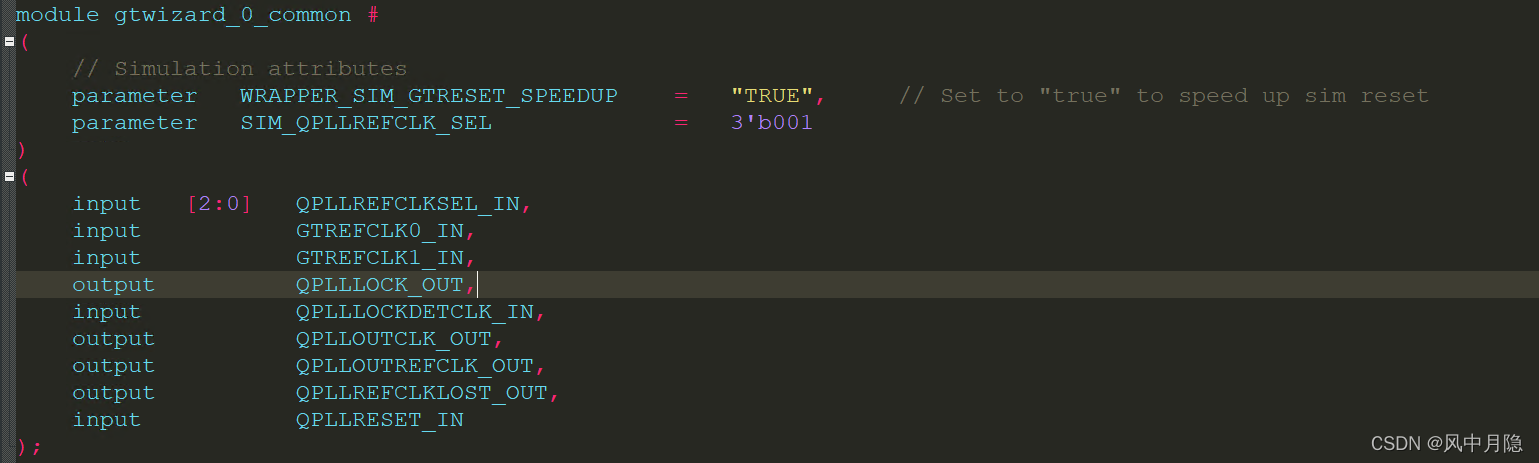

根据出现的错误,我们看到是GTP中的common*

i/gt*

*clk_in冲突,然而我们找到对应的模块gtwizard_0_common中并没有错误对应的一模一样的信号,如下所示:

`default_nettype wire

timescale 1ns / 1ps

define DLY #1 //*****************************

Entity Declaration **************************** module

gtwizard_0_common # (

// Simulation attributes

parameter WRAPPER_SIM_GTRESET_SPEEDUP = “TRUE”, // Set to “true” to speed up sim reset

parameter SIM_QPLLREFCLK_SEL = 3’b001 ) (

input [2:0] QPLLREFCLKSEL_IN,

input GTREFCLK0_IN,

input GTREFCLK1_IN,

output QPLLLOCK_OUT,

input QPLLLOCKDETCLK_IN,

output QPLLOUTCLK_OUT,

output QPLLOUTREFCLK_OUT,

output QPLLREFCLKLOST_OUT,

input QPLLRESET_IN );//***************************** Parameter Declarations

localparam QPLL_FBDIV_TOP = 16; localparam QPLL_FBDIV_IN = (QPLL_FBDIV_TOP == 16) ? 10'b0000100000 : (QPLL_FBDIV_TOP == 20) ? 10'b0000110000 : (QPLL_FBDIV_TOP == 32) ? 10'b0001100000 : (QPLL_FBDIV_TOP == 40) ? 10'b0010000000 : (QPLL_FBDIV_TOP == 64) ? 10'b0011100000 : (QPLL_FBDIV_TOP == 66) ? 10'b0101000000 : (QPLL_FBDIV_TOP == 80) ? 10'b0100100000 : (QPLL_FBDIV_TOP == 100) ? 10'b0101110000 : 10'b0000000000;localparam QPLL_FBDIV_RATIO = (QPLL_FBDIV_TOP == 16) ? 1’b1 :

(QPLL_FBDIV_TOP == 20) ? 1’b1 :

(QPLL_FBDIV_TOP == 32) ? 1’b1 :

(QPLL_FBDIV_TOP == 40) ? 1’b1 :

(QPLL_FBDIV_TOP == 64) ? 1’b1 :

(QPLL_FBDIV_TOP == 66) ? 1’b0 :

(QPLL_FBDIV_TOP == 80) ? 1’b1 :

(QPLL_FBDIV_TOP == 100) ? 1’b1 : 1’b1;// ground and vcc signals wire tied_to_ground_i; wire [63:0] tied_to_ground_vec_i; wire tied_to_vcc_i; wire[63:0] tied_to_vcc_vec_i;

assign tied_to_ground_i = 1'b0; assign tied_to_ground_vec_i = 64'h0000000000000000; assign tied_to_vcc_i = 1'b1; assign tied_to_vcc_vec_i = 64'hffffffffffffffff; //_________________________________________________________________________ //_________________________________________________________________________ //_________________________GTXE2_COMMON____________________________________ GTXE2_COMMON # ( // Simulation attributes .SIM_RESET_SPEEDUP (WRAPPER_SIM_GTRESET_SPEEDUP), .SIM_QPLLREFCLK_SEL (SIM_QPLLREFCLK_SEL), .SIM_VERSION ("4.0"), //----------------COMMON BLOCK Attributes--------------- .BIAS_CFG (64'h0000040000001000), .COMMON_CFG (32'h00000000), .QPLL_CFG (27'h06801C1), .QPLL_CLKOUT_CFG (4'b0000), .QPLL_COARSE_FREQ_OVRD (6'b010000), .QPLL_COARSE_FREQ_OVRD_EN (1'b0), .QPLL_CP (10'b0000011111), .QPLL_CP_MONITOR_EN (1'b0), .QPLL_DMONITOR_SEL (1'b0), .QPLL_FBDIV (QPLL_FBDIV_IN), .QPLL_FBDIV_MONITOR_EN (1'b0), .QPLL_FBDIV_RATIO (QPLL_FBDIV_RATIO), .QPLL_INIT_CFG (24'h000006), .QPLL_LOCK_CFG (16'h21E8), .QPLL_LPF (4'b1111), .QPLL_REFCLK_DIV (1) ) gtxe2_common_i ( //----------- Common Block - Dynamic Reconfiguration Port (DRP) ----------- .DRPADDR (tied_to_ground_vec_i[7:0]), .DRPCLK (tied_to_ground_i), .DRPDI (tied_to_ground_vec_i[15:0]), .DRPDO (), .DRPEN (tied_to_ground_i), .DRPRDY (), .DRPWE (tied_to_ground_i), //-------------------- Common Block - Ref Clock Ports --------------------- .GTGREFCLK (tied_to_ground_i), .GTNORTHREFCLK0 (tied_to_ground_i), .GTNORTHREFCLK1 (tied_to_ground_i), .GTREFCLK0 (GTREFCLK0_IN), .GTREFCLK1 (GTREFCLK1_IN), .GTSOUTHREFCLK0 (tied_to_ground_i), .GTSOUTHREFCLK1 (tied_to_ground_i), //----------------------- Common Block - QPLL Ports ----------------------- .QPLLDMONITOR (), //--------------------- Common Block - Clocking Ports ---------------------- .QPLLOUTCLK (QPLLOUTCLK_OUT), .QPLLOUTREFCLK (QPLLOUTREFCLK_OUT), .REFCLKOUTMONITOR (), //----------------------- Common Block - QPLL Ports ------------------------ .QPLLFBCLKLOST (), .QPLLLOCK (QPLLLOCK_OUT), .QPLLLOCKDETCLK (QPLLLOCKDETCLK_IN), .QPLLLOCKEN (tied_to_vcc_i), .QPLLOUTRESET (tied_to_ground_i), .QPLLPD (tied_to_vcc_i), .QPLLREFCLKLOST (QPLLREFCLKLOST_OUT), .QPLLREFCLKSEL (QPLLREFCLKSEL_IN), .QPLLRESET (QPLLRESET_IN), .QPLLRSVD1 (16'b0000000000000000), .QPLLRSVD2 (5'b11111), //------------------------------- QPLL Ports ------------------------------- .BGBYPASSB (tied_to_vcc_i), .BGMONITORENB (tied_to_vcc_i), .BGPDB (tied_to_vcc_i), .BGRCALOVRD (5'b11111), .PMARSVD (8'b00000000), .RCALENB (tied_to_vcc_i) ); endmodule

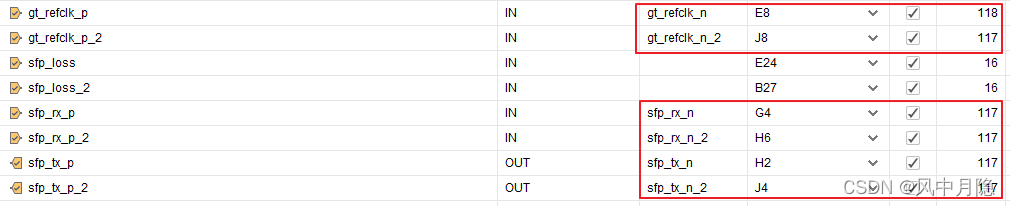

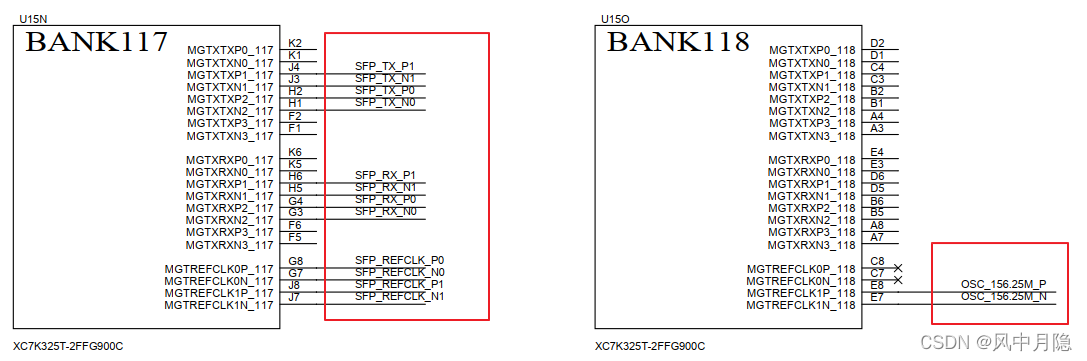

但很明显我们这里能知道是时钟布线冲突,这里先看看两个GTX的管脚约束情况,如下图所示:

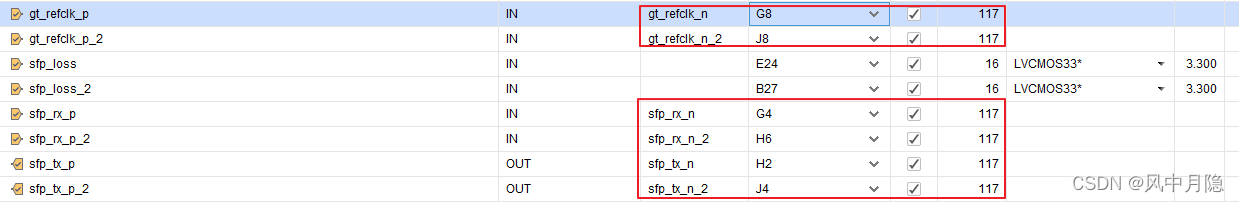

即数据线在相同的bank,时钟在不同的bank。这个是根据硬件原理图来的,如下所示:

再根据原理图看,时钟我可以调整到一个bank上即117上,进行调整后如下所示,问题依然存在,并没有解决。

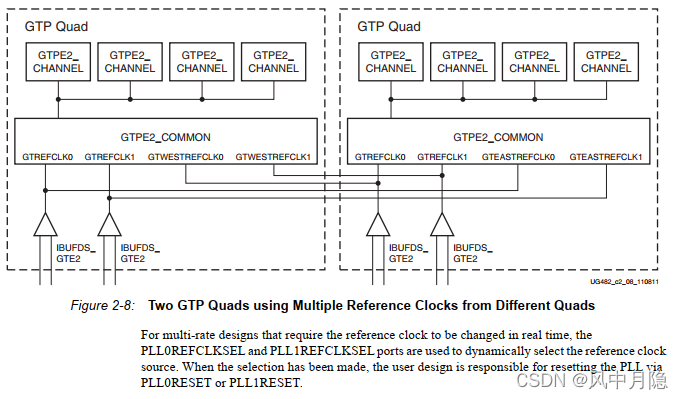

那么是否是说同一个工程中不能使用两个GTX呢?我翻看ug482_7Series_GTP_Transceivers手册后发现并不是,比如手册上是可以使用多个IP的,如下所示:

但是需要这个GTP分布在不同的Quad。而本设计硬件上是将两个SFP设置在了同一个Quad上,因此报了错误。

为了验证这个思路是否正常,我将一组GTP的信号管脚移植到BANK118如下所示,经过编译发现错误消失了,即证明若需要两个GTP时需要它们在两个BANK上。