低引脚数总线接口的规范,称为LPC

目标:启用一个没有ISA或X-bus的系统,降低传统X-bus设备成本,满足X-bus的数据传输速率,执行与X-bus相同的周期类型:Memory, I/O, DMA,和Bus Master,支持固件内存周期类型,将X-bus上的内存空间从16MB增加到4GB,同步设计。

中断通过串行中断(SERIRQ)协议进行通信。

LPC接口不需要支持高速总线

,

USB等低延迟总线。

术语:

主机:直接连接到CPU或连接到CPU的上游设备的接口部分。

这是典型的系统芯片组。

外设:连接到X-bus的LPC下游设备

,如Super I/O组件、flash和其他嵌入式控制器。

‘

XXXXb’:以二进制表示的信号值

信号定义:LPC接口需要7个信号,6个信号可选,

LPC所需信号:

LAD[3:0]

多路

复用

命令、地址和数据

LFRAME#

帧:表示一个新周期的开始,中断周期的结束。

LRESET#

与主机上的Reset相同如果主机的接口上有则不要

LCLK

主机上与PCI时钟相同的33MHz时钟。

与现有的基于ISA设备相比,信号节省是巨大的。

LPC接口通常只需要6个新信号:LAD[0:3]、LFRAME#和LDRQ#。

CLKRUN#通常只在移动系统中实现。LPCPD#仅用于在某些低功耗状态下部分供电的LPC设备

协议概述

1、

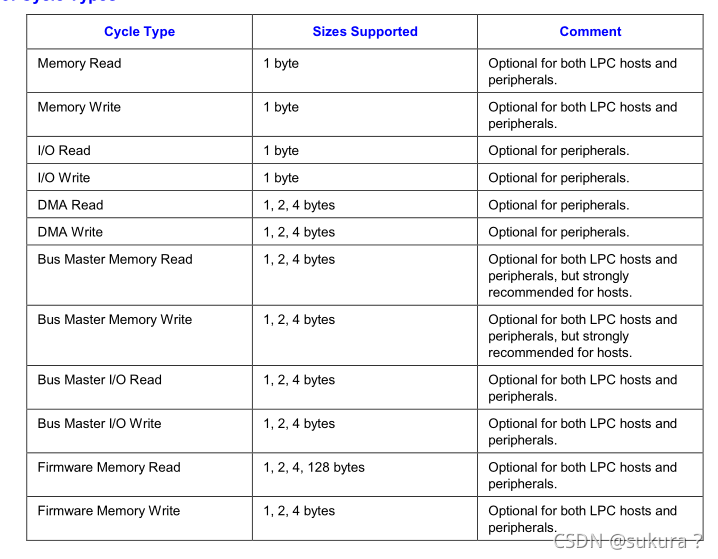

协议支持的各种类型的周期

:

应遵守以下规则:

•主机和外设应执行所述的周期类型。

•外设不能尝试主机不支持的总线主周期。例如,如果主机不支持总线