目录:

Multicycle Path

1.什么是multicycle path

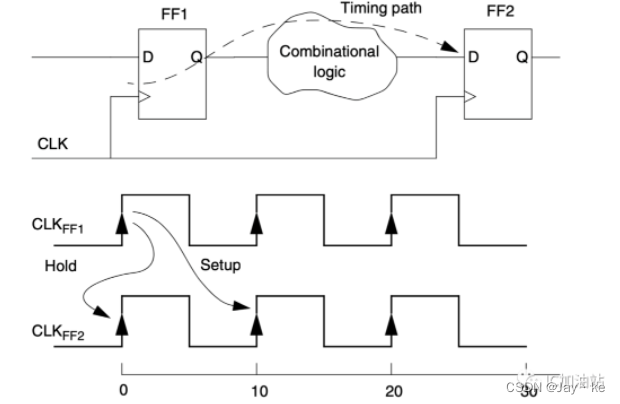

通常情况下,在同一个时钟驱动下的寄存器之间信号的传输都是单周期的

-

setup检查

是从launch_clk的一个上升沿到capture_clk的下一个上升沿, -

hold检查

是从launch_clk的一个上升沿到capture_clk的捕获沿的前一个沿

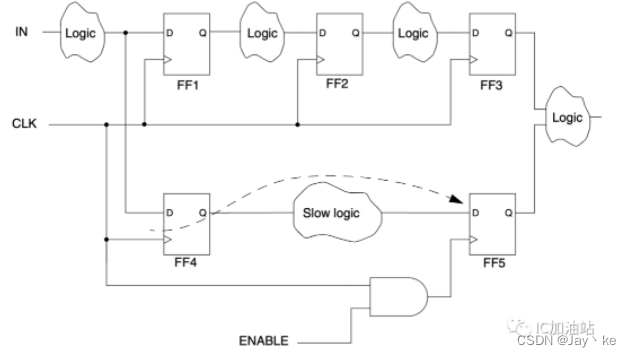

但是在有的电路设计中,要么是有意为之,要么是单周期无法close timing,我们会遇到下面的电路

其中FF4的Q变化要经过2个周期才能被FF5的D采样到,这个时候我们就要告诉STA工具,这个path不是单周期的,需要2个周期。在Prime Time中,这个command 是set_multicycle_path

2.set_multicycle_path:

时序约束的目标就是让发射沿发射的数据能够被捕获沿捕获,就是考虑两个沿移动的问题,在两个沿之间保留特定的时间

set_multicycle_path path_multiplier [-setup|-hold]

[-start|-end]

-from <StartPoint>

-through <ThroughPoint>

-to <EndPoint>

- end是指capture flop的cl

版权声明:本文为qq_39541098原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接和本声明。