实验题目

设计、实现八位二进制数全加器

设计思路

总体设计为三输入,两输出。具体:实体声明部分描述电路模块的端口,即指定输入输出口及其大小。设计具有8位位宽的矢量或总线端口信号a,b以及标准一位输入的cin。然后在结构体描述部分对电路模块的功能进行描述,指明整个电路时如何运作的:对3个二进制的9位矢量数进行加法运算输出到data。

使用两个四位二进制加法器组成。

功能设计

实现八位二进制数加法,并保存可能存在的溢出值。

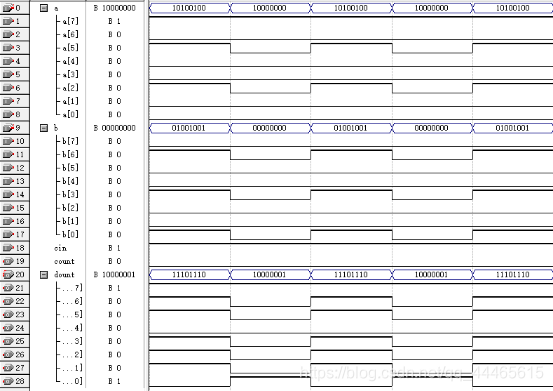

波形图

源代码

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity ADD8 is

port (a,b : in std_logic_vector(7 downto 0);

count : out std_logic;

cin : in std_logic;

dount : out std_logic_vector(7 downto 0) );

end entity Add8;

architecture bhv of add8 is

signal data :std_logic_vector(8 downto 0);

begin

data <= ('0' & a) + ('0' & b) + ("00000000" & cin);

count <= data(8);

dount <= data(7 downto 0);

end architecture bhv;

实验题目

设计、实现八位无符号二进制数乘法器

设计思路

八位乘法器由八位全加器以时序逻辑构成,通过逐项移位相加原理实现乘法。乘数的各位数码从被乘数的最低位开始依次相乘,每相乘一次得到部分积,若为此位的数码为1,则乘数左移后与上一次的和相加;若为0,左移后以全零相加,直至被乘数的最高位,所有的部分积被加过一次可以得到相应的乘积。由于乘数的每一位不是0就是1,对应的部分积不是0就是和被乘数相等的部分积,所以实际作部分积相加这一步时,只要根据乘数的对应位判断,如过该位为1,则将累加器中的数据加上被乘数再移位;如该位为0时,就不加被乘数而直接移1位。然后对乘法器的进行自顶而下设计,把乘法器的设计分成几个功能模块,进而逐步细化。该任务需了解各个模块的引脚含义以及内部构造,并对各个模块的实现功能进行分析,通过VHDL对这些模块进行编程,调试。最后在QuartusⅡ进行模拟仿真,得出正确的运行结果。

功能设计

本设计采用移位和加法来实现两个8位二进制数相乘,使用VHDL语言完成八位乘法器,以及如何做二进制位相乘的运算过程。该乘法器是由八位加法器构成八位乘法器,通过逐项移位相加来实现乘法功能,并以QuartusⅡ软件工具进行模拟。

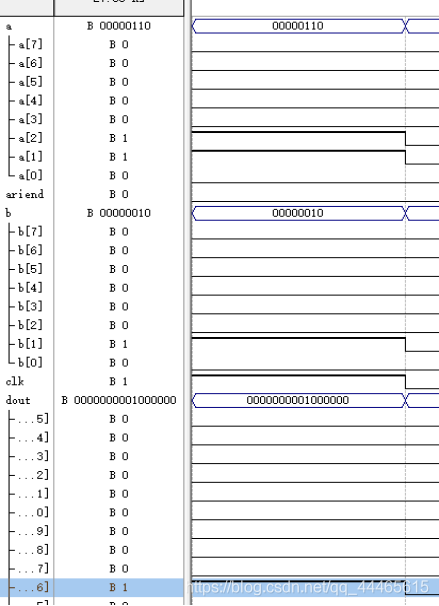

波形图

源代码:

1.library ieee; //四位二进制并行加法器

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity add4 is

port( cin:in std_logic;

a,b:in std_logic_vector(3 downto 0);

s:out std_logic_vector(3 downto 0);

cout:out std_logic);

end;

architecture one of add4 is

signal sint,aa,bb:std_logic_vector(4 downto 0);

begin

aa<='0' & a;

bb<='0' & b;

sint<=aa+bb+cin;

s<=sint(3 downto 0);

cout<=sint(4);

end;

2.library ieee; //由两个加法器结合成八位加法器;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity add8 is

port( cin:in std_logic;

a,b:in std_logic_vector(7 downto 0);

s:out std_logic_vector(7 downto 0);

cout:out std_logic);

end;

architecture one of add8 is

component add4 //说明要调用的元件端口

port( cin:in std_logic;

a,b:in std_logic_vector(3 downto 0);

s:out std_logic_vector(3 downto 0);

cout:out std_logic);

end component;

signal carryout: std_logic;

begin

u1:add4 port map(cin,a(3 downto 0),b(3 downto 0),s(3 downto 0),carryout);

u2:add4 port map(carryout,a(7 downto 4),b(7 downto 4),s(7 downto 4),cout);

end;

3.library ieee; //一位乘法器;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity andarith is

port( abin:in std_logic;

din:in std_logic_vector(7 downto 0);

dout:out std_logic_vector(7 downto 0));

end;

architecture one of andarith is

begin

process(abin,din)

begin

for i in 0 to 7 loop

dout(i)<=din(i) and abin;

end loop;

end process;

end;

4.library ieee; //乘法运算控制器

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity arictl is

port( clk,start:in std_logic;

clkout,rstall,ariend:out std_logic);

end;

architecture one of arictl is

signal cnt4b:std_logic_vector(3 downto 0);

begin

rstall<=start;

process(clk,start)

begin

if start='1' then cnt4b<="0000";

elsif clk'event and clk='1' then

if cnt4b<8 then //小于8:计数,等于8:表明乘法运算结束

cnt4b<=cnt4b+1;

end if;

end if;

end process;

process(clk,cnt4b,start)

begin

if start='0' then

if cnt4b<8 then

clkout<=clk; ariend<='0';

else clkout<='0'; ariend<='1';

end if;

else clkout<=clk; ariend<='0';

end if;

end process;

end;

5.library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity reg16b is

port( clk,clr:in std_logic;

d:in std_logic_vector(8 downto 0);

q:out std_logic_vector(15 downto 0));

end;

architecture one of reg16b is

signal r16s:std_logic_vector(15 downto 0);

begin

process(clk,clr)

begin

if clr='1' then r16s<="0000000000000000";

elsif clk'event and clk='1' then

r16s(6 downto 0)<=r16s(7 downto 1);

r16s(15 downto 7)<=d;

end if;

end process;

q<=r16s;

end;

6.library ieee; //8位右移寄存器:在时钟信号作用下,进行输入值的移位与锁存。

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity sreg8b is

port( clk,load:in std_logic;

din:in std_logic_vector(7 downto 0);

qb:out std_logic);

end;

architecture one of sreg8b is

signal reg8:std_logic_vector(7 downto 0);

begin

process(clk,load)

begin

if clk'event and clk='1' then

if load='1' then reg8<=din;

else reg8(6 downto 0)<=reg8(7 downto 1);

end if;

end if;

end process;

qb<=reg8(0);

end;

7.library ieee; //8位乘法器顶层设计

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

entity mult8x8 is

port( clk:in std_logic;

start:in std_logic;

a,b:in std_logic_vector(7 downto 0);

dout:out std_logic_vector(15 downto 0);

ariend:out std_logic);

end;

architecture struc of mult8x8 is

component add8 is

port( cin:in std_logic;

a,b:in std_logic_vector(7 downto 0);

s:out std_logic_vector(7 downto 0);

cout:out std_logic);

end component;

component andarith is

port( abin:in std_logic;

din:in std_logic_vector(7 downto 0);

dout:out std_logic_vector(7 downto 0));

end component;

component arictl is

port( clk,start:in std_logic;

clkout,rstall,ariend:out std_logic);

end component;

component reg16b is

port( clk,clr:in std_logic;

d:in std_logic_vector(8 downto 0);

q:out std_logic_vector(15 downto 0));

end component;

component sreg8b is

port( clk,load:in std_logic;

din:in std_logic_vector(7 downto 0);

qb:out std_logic);

end component;

signal gndint :std_logic;

signal intclk :std_logic;

signal rstall :std_logic;

signal qb :std_logic;

signal andsd :std_logic_vector(7 downto 0);

signal dtbin :std_logic_vector(8 downto 0);

signal dtbout :std_logic_vector(15 downto 0);

begin

dout<=dtbout; gndint<='0';

u1:arictl port map( clk,start,intclk,rstall,ariend);

u2:sreg8b port map(intclk,rstall,b,qb);

u3:andarith port map(qb,a,andsd);

u4:add8 port map(gndint,dtbout(15 downto 8),andsd,dtbin(7 downto 0),dtbin(8));

u5:reg16b port map(intclk,rstall,dtbin,dtbout);

end;

学习心得

通过本次课外实验项目,我了解了如何使用QuartusⅡ软件、加深了对VHDL语言结构的认识以及如何设计加法乘法器。虽然途中出现了一些困难与问题,比如说运行波形图时结果出现毛刺,设置为功能仿真后又出现Error等等的问题。但是我还是在查询资料的过程中,通过对同一个工程下不同程序的连接,逻辑结构的梳理,对最后结果的测试验证等方面的学习,加深了对整个代码及软件的认识。。此外,在团队中,我们独立思考,互相分享经验和进步,这也改善了自己的各项能力。