UVM学习之路(2)— 使用VCS+Verdi进行仿真调试

一、前言

Verdi最初是由Novas Softwave公司设计的,后属于了SpringSoft公司,最终SpringSoft被Synopsys公司收购,Verdi正式属于Synopsys。

Verdi可以调用第三方工具进行编译仿真产生波形文件并可以查看、可查看源代码对应的电路图,最强大之处在于可以在源代码、原理图、波形图和状态图之间进行即时跟踪,协助工程师debug。

原文

参考文章 :

Linux下VCS与Verdi联合仿真简易教程及例子示范

二、编写源码

编写设计文件

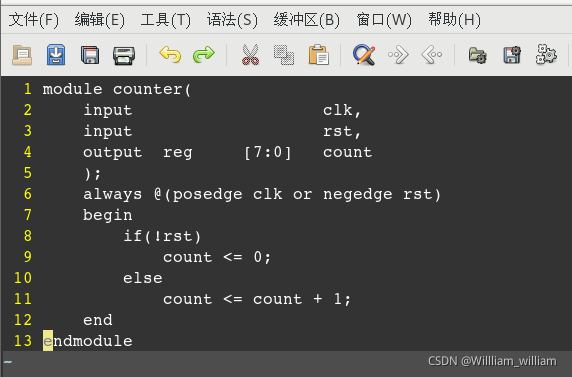

counter.v

如下所示,这是一个简单的计数器模块

module counter(

input clk,

input rst,

output reg [7:0] count

);

always @(posedge clk or negedge rst)

begin

if(!rst)

count <= 0;

else

count <= count + 1;

end

endmodule

编写测试文件

tb.sv

如下所示,

module tb;

reg clk,rst_n;

wire [7:0] count;

counter dut(

.clk (clk),

.rst (rst_n),

.count (count)

);

always #(5) clk = ~clk;

initial begin

clk <= 0;

rst_n <= 0;

#20;

rst_n <= 1;

#500;

$display("tb counter finish.");

$finish;

end

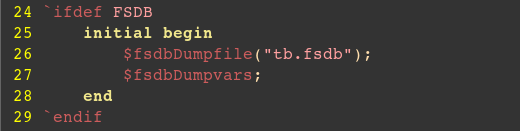

`ifdef FSDB

initial begin

$fsdbDumpfile("tb.fsdb");

$fsdbDumpvars;

end

`endif

endmodule

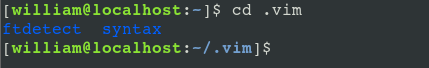

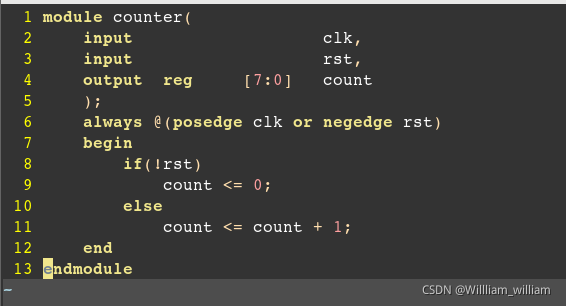

三、设置高亮

我们使用gvim编写源码的时候会发现关键字并没有高亮,所以我们要对verilog和systemverilog的语法高亮进行设置

我们需要从home目录下进入

.vim

文件夹下,如果没有,则新建一个,然后下载systemverilog语法设置文件,链接在文末,打开后可以看到如下两个文件夹,

然后将其中的文件分别放入对应的文件夹中即可(没有则新建文件夹),如下所示

然后再次打开源文件就可以看到语法高亮了

四、编译运行

使用如下命令进行编译,

vcs -full64 -sverilog -fsdb +define+FSDB counter.v tb.sv

其中

-fsdb

表示支持对fsdb相应操作,

+define+FSDB

相当于在文件里加上

FSDB

宏定义,即为了让测试文件的如下代码生效,加这两个选项即是让运行时产生

.fsdb

文件,这个文件是verdi所需要用的

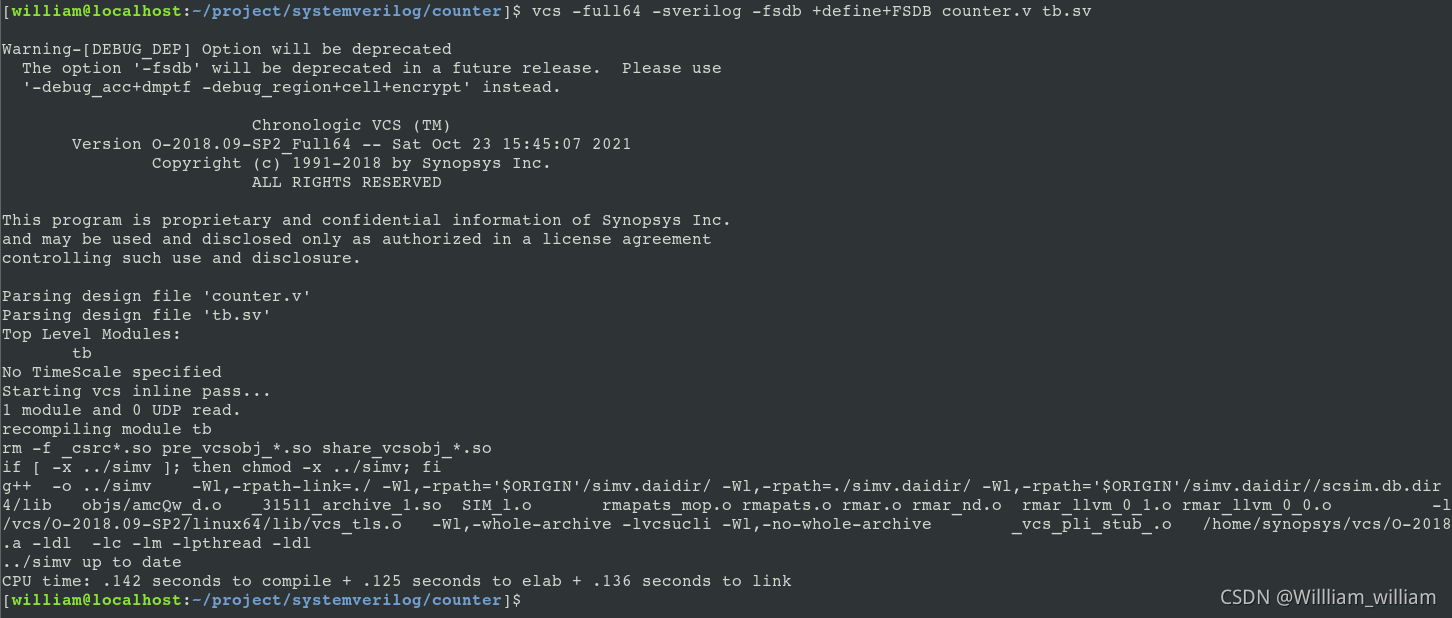

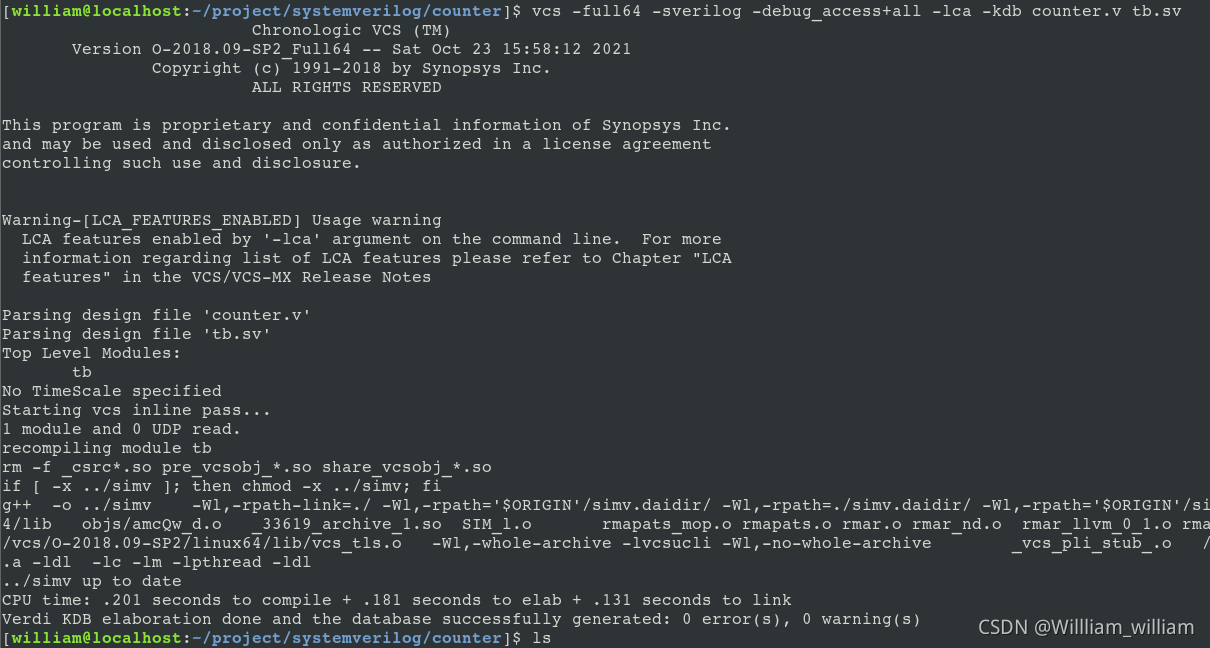

编译成功如下所示

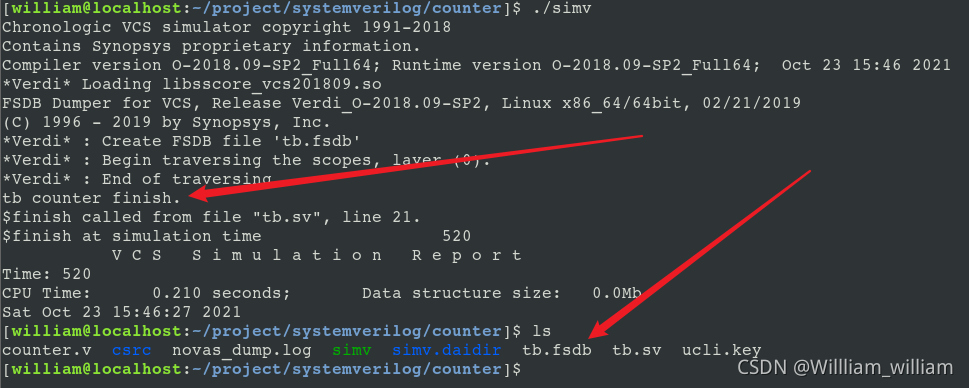

然后运行仿真如下所示

.simv

可以看到在当前文件夹下已经得到了

tb.fsdb

文件

使用verdi打开

tb.fsdb

文件

verdi tb.fsdb

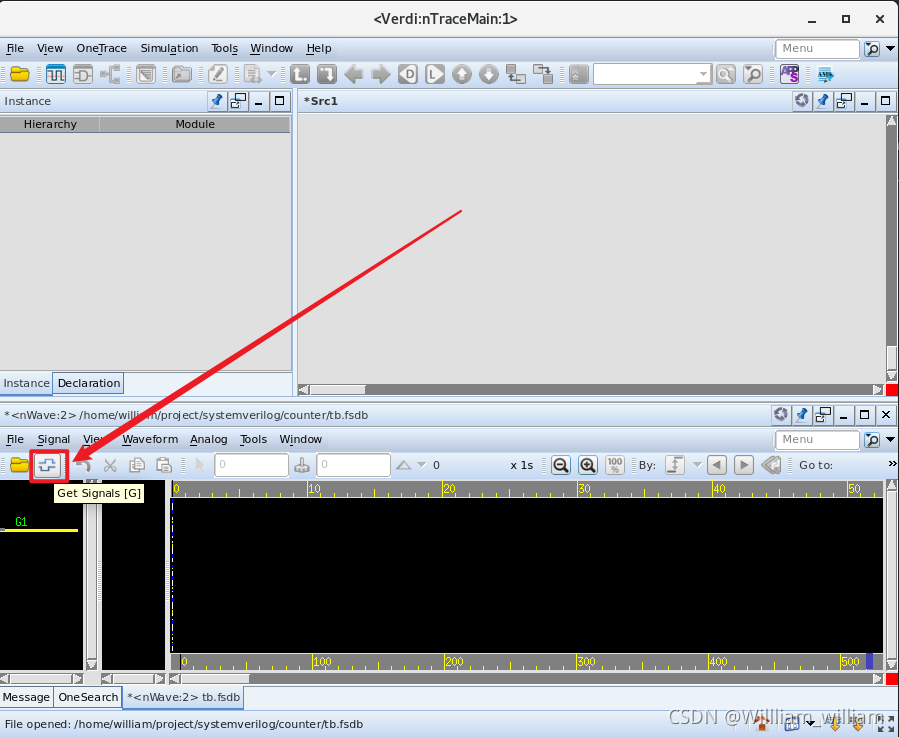

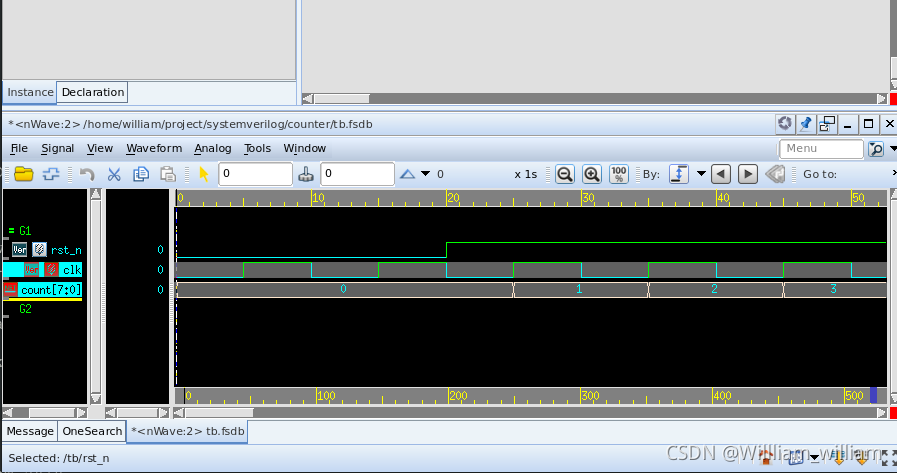

Verdi打开后如下所示,点击【Get Signals】图标按钮,可以添加信号

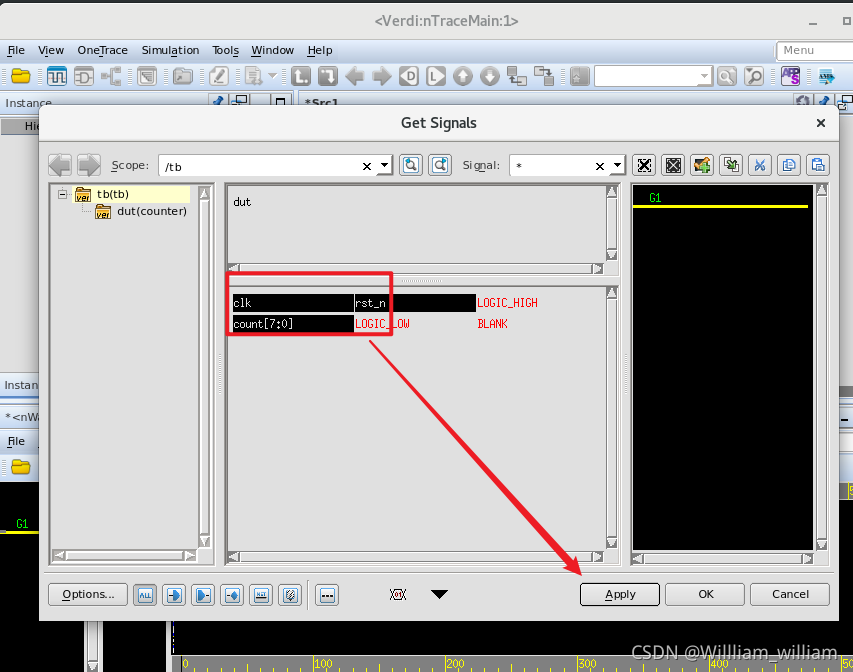

将信号选中然后点击【Apply】按钮,就可以将信号添加到波形窗口了

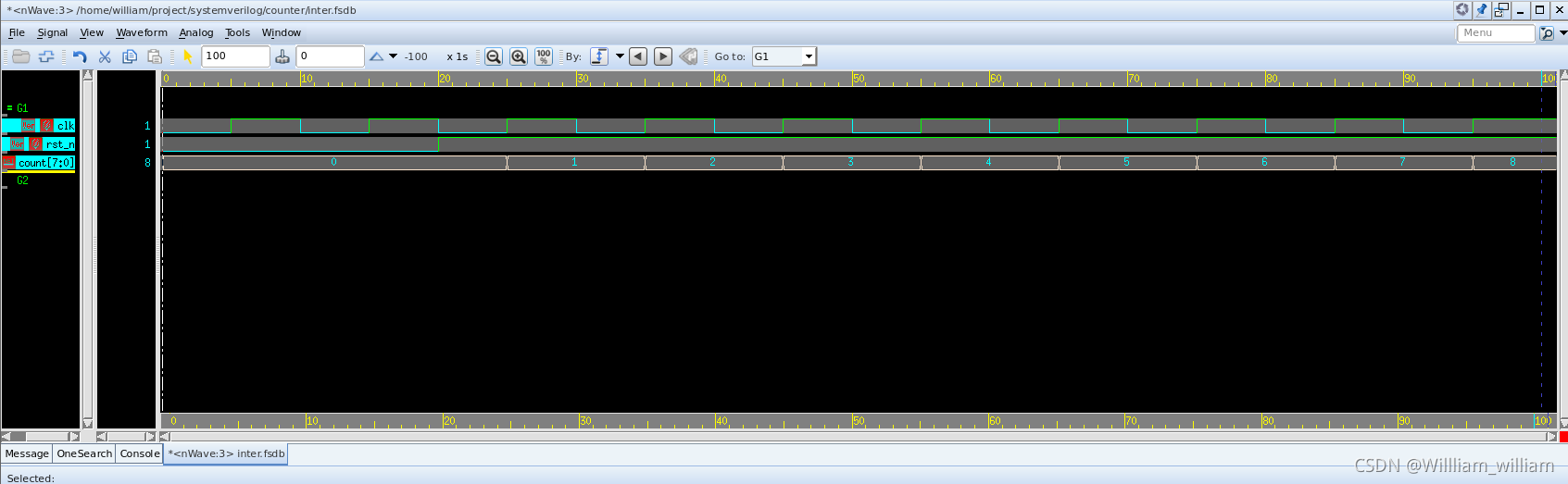

添加完波形如下所示

五、Verdi调试

我们在编译时加入选项

-debug_access+all

选项表示启动

调试模式

,

-lca -kdb

表示加入对Verdi的支持,

vcs -full64 -sverilog -debug_access+all -lca -kdb counter.v tb.sv

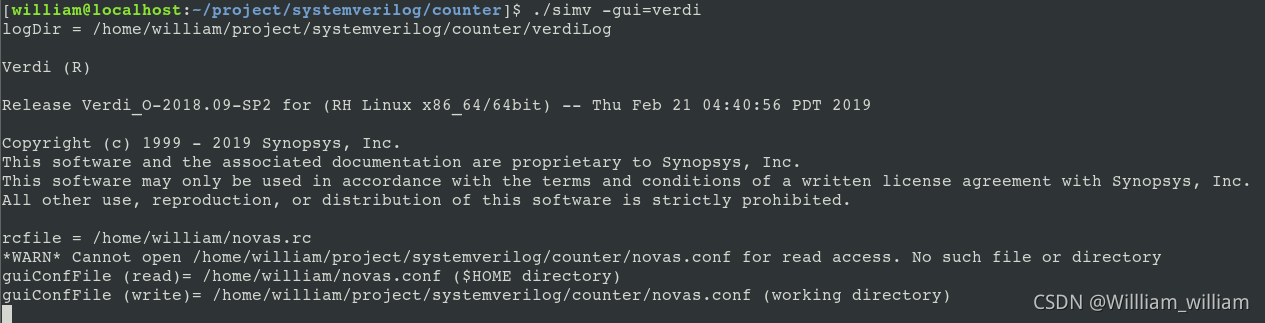

然后在仿真时加入

-gui=verdi

表示使用Verdi进行仿真

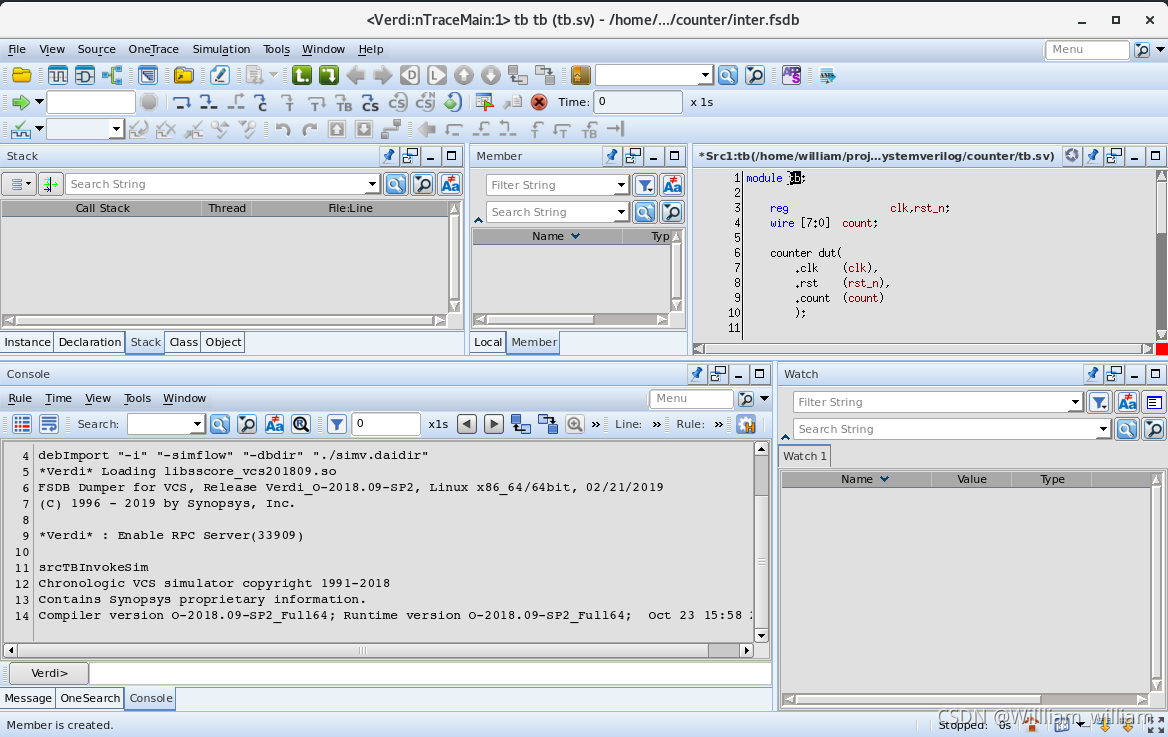

这样就会自动打开Verdi图形化窗口如下所示

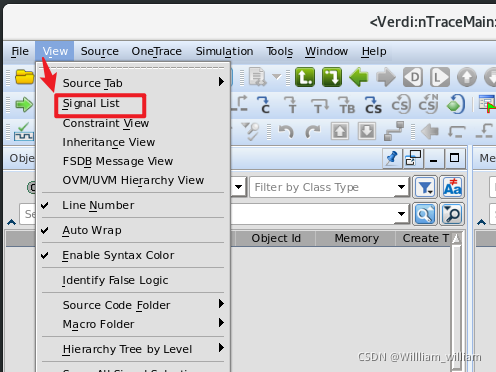

点击【View】->【Signal List】打开信号窗口

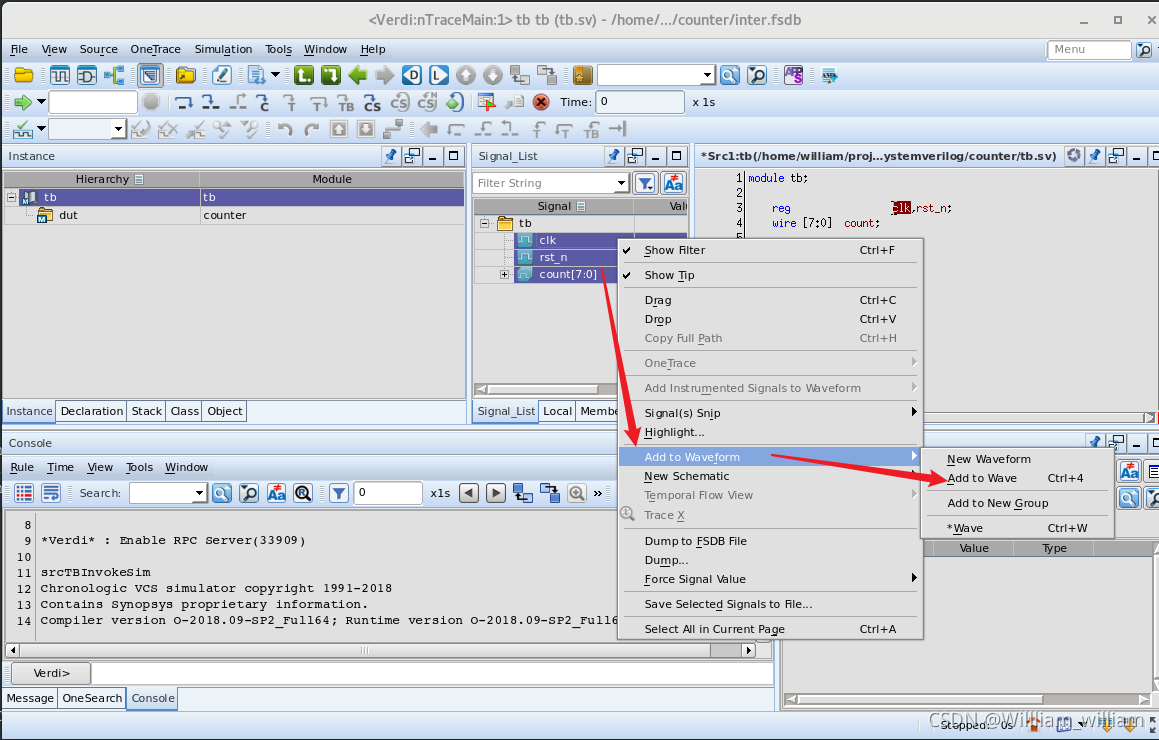

我们按住【Shift】键将信号都选中然后右键【Add to Wavefrom】->【Add to Wave】将信号添加到波形窗口中

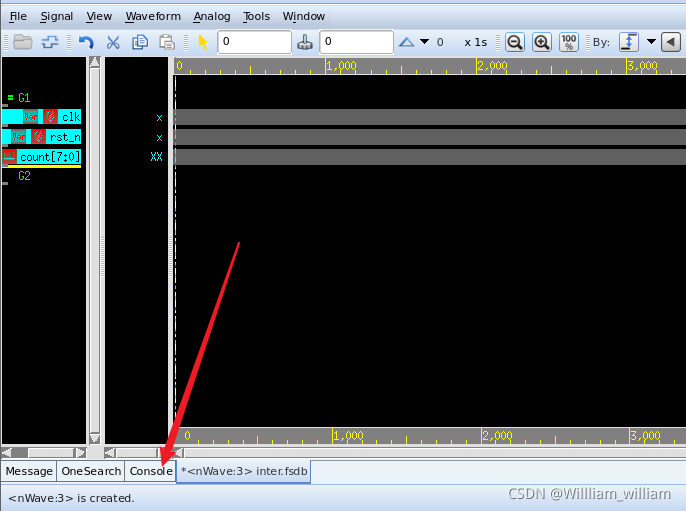

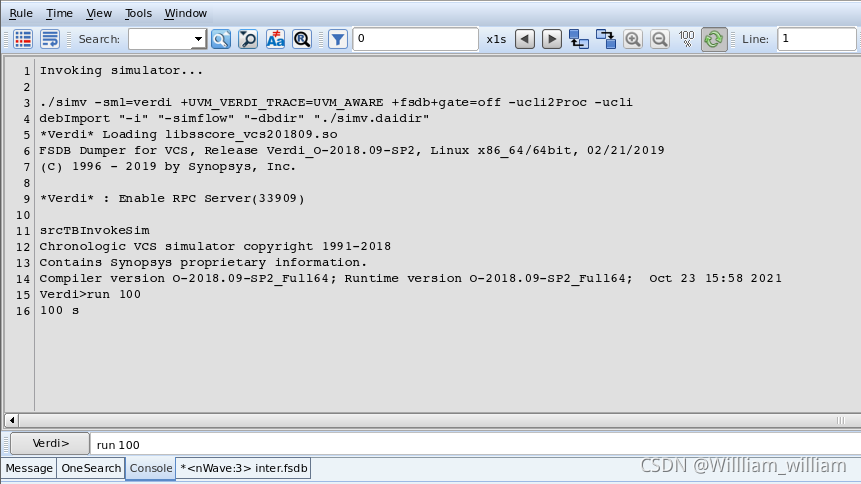

接下来我们再切回【Console】窗口,

输入

run 100

命令,然后按【Enter】键执行

可以看到波形已经有变化了

六、Makefile

为了更便捷的工作,我们可以编写Makefile如下所示

#---------------------------------------------------------------------------

# files options

#---------------------------------------------------------------------------

DFILES += counter.v

VFILES += tb.sv

#---------------------------------------------------------------------------

# tool options

#---------------------------------------------------------------------------

TOOL_CMD = vcs -full64

COMP_OPT = -sverilog -debug_access+all -lca -kdb -fsdb +define+FSDB -timescale=1ns/1ps

comp:

$(TOOL_CMD) $(COMP_OPT) $(DFILES) $(VFILES)

run:

./simv

rung:

./simv -gui=verdi

verdi:

verdi tb.fsdb

clean:

rm -rf csrc simv simv.daidir *.fsdb novas.* ucli.key

rm -rf *.log* *.vpd urgReport verdiLog