快速链接:

.

👉👉👉 个人博客笔记导读目录(全部) 👈👈👈

PSTATE:

程序状态寄存器

SP_ELx(x>0):

在EL1/EL2/EL3 level中,如果spsel=0,则使用SP_ELx(x>0)

SP_EL0 :

在所有level中,如果spsel=1, 则使用SP_EL0

SPSR :

save program status register 备份的程序状态寄存器

ELR_ELx(x>0):

异常链接寄存器,记录着异常时程序的返回地址

ESR_ELx(x>0) :

同步异常, 异常特征寄存器

FAR_ELx(x>0):

同步异常, 异常时的错误地址

VBAR_ELx(x>0):

向量表基地址寄存器

TTBRn_ELx(n=1,2、x>0):

地址翻译基地址寄存器

MAIR_ELx(x>0) :

内存属性寄存器

PAR_EL1:

物理地址寄存器, 当使用指令操作MMU进行VA到PA的转换时,物理地址由PAR_EL1输出.

SCR_EL3 :

安全配置寄存器

SCTLR_ELx(x>0):

系统控制寄存器

TCR_ELx(x>0):

地址翻译控制寄存器

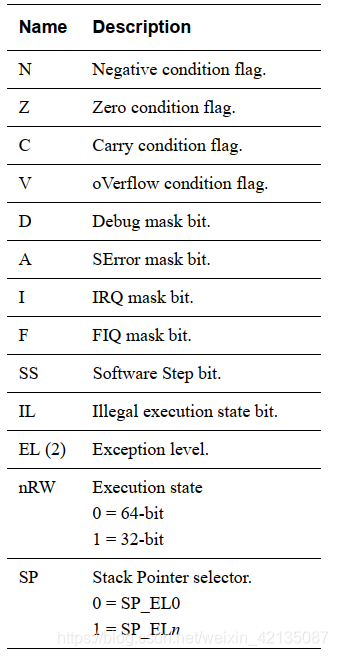

1、PSTATE

PSTATE的bit位定义:

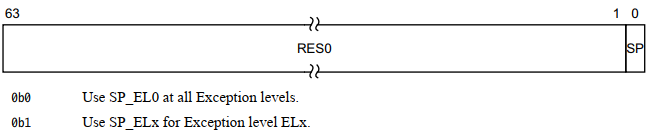

(1)、spsel : (Stack Pointer Select)

2、Stack pointer(sp)寄存器介绍

默认情况下,来了一个异常后,选择当前异常级别的sp,例如来了一个异常到EL1, 那么将自动选择sp_el1做为sp;

但是呢,在高异常等级,通过修改spsel,也可以使用SP_EL0

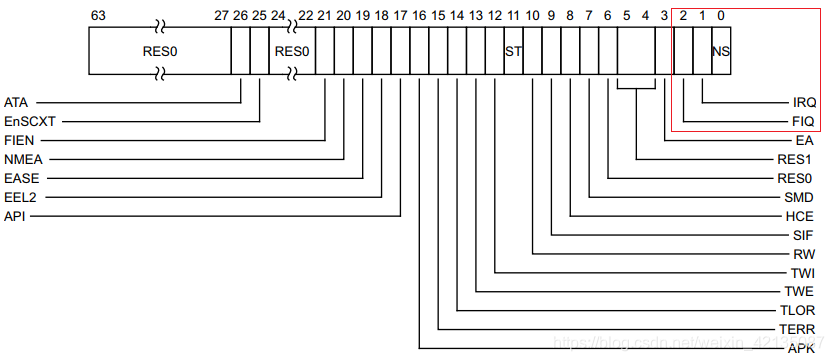

3、SCR_EL3 :(Secure Configuration Register)

- NS :0-secure state, 1-NonSecure state

- IRQ: 0-运行在EL3以下时irq不会target到EL3, 1-irq总是target到EL3

- FIQ: 0-运行在EL3以下时fiq不会target到EL3, 1-fiq总是target到EL3

- EA, bit [3] :

– 0- 运行在EL3以下时External aborts和SError不会target到EL3,运行在EL3时Serror不会产生,External aborts target到EL3

– 1-External aborts and SError target到EL3- SMD, bit [7]:0-smc指令在EL3/EL2/EL1中是enable, 1-smc指令是disable的

- HCE, bit [8]:1-hvc指令在EL3/EL2/EL1中是enable, 0-hvc指令是disable的

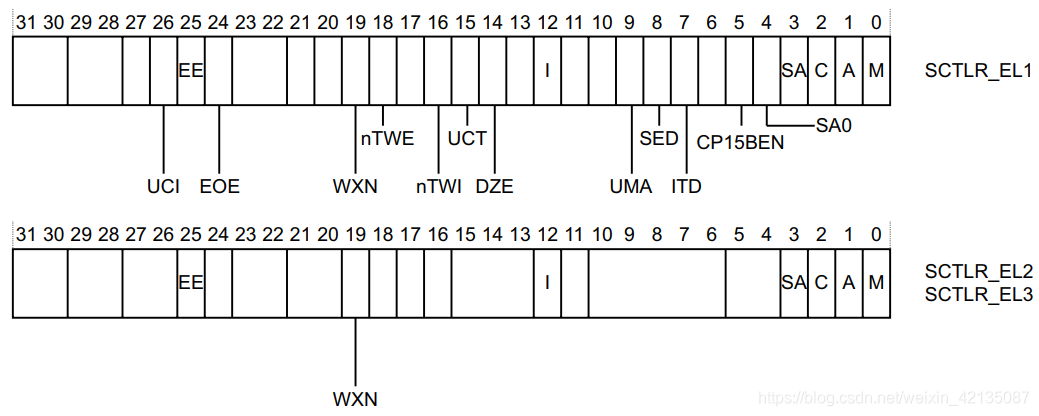

4、SCTLR:(System Control Register)

- UCI : 置1后,EL0可以在aarch64下访问 DC CVAU, DC CIVAC, DC CVAC,IC IVAU指令

- EE:0-Little endian, 1-Big endian.

- EOE:EL0显示的数据访问方式,0-Little endian, 1-Big endian.

- WXN: 0-XN权限不开启,XN权限开启

- nTWE: 1-WFE是正常的指令

- nTWI: 1-WFI是正常的指令

- UCT:1- EL0可以访问CTR_EL0

- DZE:1-EL0可以访问cache的DC ZVA指令

- I:Instruction cache enable

- UMA :EL0中断Mask(适用于aarch64)

- SED:1-SETEND指令disabled(适用于aarch32)

- ITD:1-IT指令disabled

- CP15BEN: cp15 enable(适用于aarch32)

- SA0 开启在EL0sp对齐检查

- SA 开启sp对齐检查

- C :data cache enable

- A : 对齐检查alignment check enable

- M : enable MMU

大小端的解释:

XN权限: