14天学习训练营导师课程:

周贺贺《ARMv8/ARMv9架构-快速入门》

1. 异常处理种类

1.1 中断

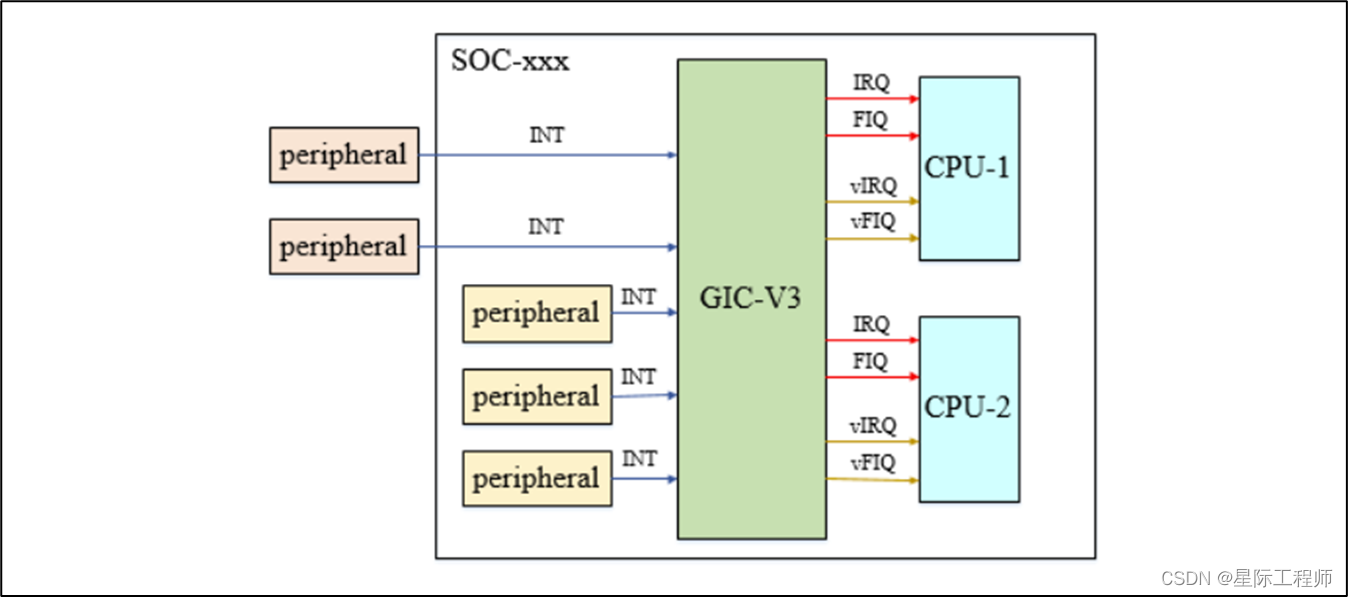

在ARM中,FIQ的优先级要高于IRQ,在SOC内部会有一个中断控制器负责中断优先级调度,然后发送中断信号给处理器。中断属于异步模式的异常。

1.2 中止

中止异常分为数据中止和指令中止,MMU能够捕获错误并汇报给处理器。

1.3 复位

复位是处理器中优先级最高的异常,通常分为上电复位和软件复位。

1.4 软件产生的异常

ARMv8提供了3中软件产生的异常,发生此异常的原因是软件企图进入更高的异常等级。

SVC 允许用户模式下的程序请求os服务

HVC 允许客户机(Linux os)请求主机服务

SMC 允许普通世界的程序请求安全服务

1.5 同步异常和异步异常

故名思议,同步异常必须等待cpu处理完当前异常才可以继续执行指令。

常见的同步异常:

访问其他等级的寄存器,比如当前是EL1,如果访问EL2的寄存器就会出现异常

SP未对齐

SVC、HVC和SMC

地址翻译错误/地址权限

常见的异步异常:

物理中断 IRQ、FIQ和系统错误

虚拟中断 vIRQ、vFIQ、vSError

2. ARMv8异常模型

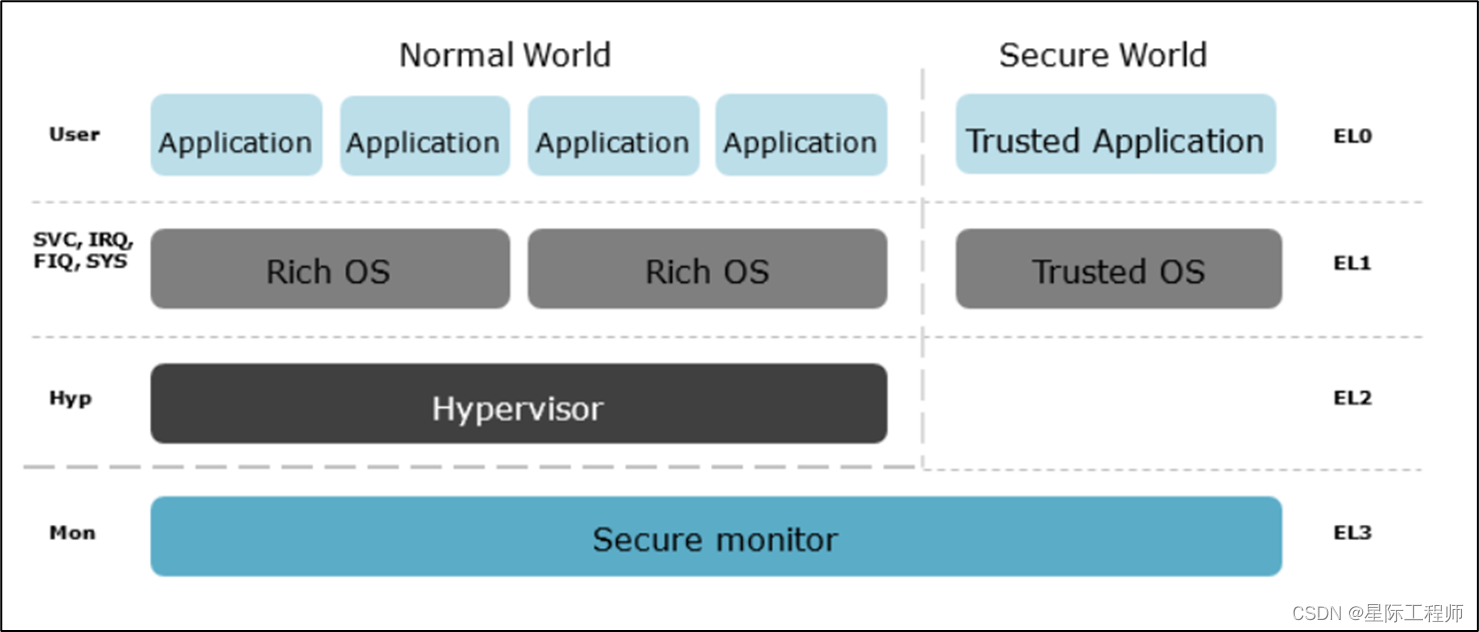

ARMv8-a Exception level有关的说明如下:

1)首先需要注意的是,AArch64中,已经没有User、SVC、ABT等处理器模式的概念,但ARMv8需要向前兼容,在AArch32中,就把这些处理器模式map到了4个Exception level。

2)Application位于特权等级最低的EL0,Guest OS(Linux kernel、window等)位于EL1,提供虚拟化支持的Hypervisor位于EL2(可以不实现),提供Security支持的Seurity Monitor位于EL3(可以不实现)。

3)只有在异常发生时(或者异常处理返回时),才能切换Exception level(这也是Exception level的命名原因,为了处理异常)。当异常发生时,有两种选择,停留在当前的EL,或者跳转到更高的EL,EL不能降级。同样,异常处理返回时,也有两种选择,停留在当前EL,或者调到更低的EL。

3. GIC中断控制器

由于SOC中外设及与其相关的中断数量众多,且各中断又有多种不同的配置方式,为了减轻CPU的负担,现代处理器中断的配置和管理一般都通过中断控制器实现。

GIC是arm公司推出可与cortex-A和cortex-R处理器配合使用的中断控制器,当前一共有4个版本,分别为GICv1 – GICv4。GICv3是基于armv8的SOC设计中应用较为广泛的一种中断控制器,GICv4与GICv3的功能基本相同,只是为了提高虚拟化的性能,增加了直接注入虚拟中断的能力。