随着深度学习(人工智能)的火热,异构并行计算越来越受到业界的重视。从开始谈深度学习必谈GPU,到谈深度学习必谈计算力。计算力不但和具体的硬件有关,且和能够发挥硬件能力的人所拥有的水平(即异构并行计算能力)高低有关。

一个简单的比喻是:两个芯片计算力分别是10T和 20T,某人的异构并行计算能力为0.8,他拿到了计算力为10T的芯片,而异构并行计算能力为0.4的人拿到了计算力为20T的芯片,而实际上最终结果两人可能相差不大。异构并行计算能力强的人能够更好地发挥硬件的能力,而本文的目标就是告诉读者要变成一个异构并行计算能力强的工程师需要学习那些知识。

异构并行计算是笔者提出的一个概念,它本质上是由异构计算和并行计算组合而来,一方面表示异构并行计算工程师需要同时掌握异构计算的知识,同时也需要掌握并行计算的知识;另一方面是为更好地发展和丰富异构计算和并行计算。通过异构并行计算进一步提升了知识的系统性和关联性,让每一个异构并行计算工程师都能够获得想要的工作,拿到值得的薪水。

对于一个异构并行计算工程师的日常来说,他的工作涉及的方面很广,有硬件,有软件,有系统,有沟通;是一个对硬实力和软实力都有非常高要求的岗位。

异构并行计算的难度是非常高的,而市场对这个职位的需求一直在提升,期待读者能够和我一起投身于异构并行计算的行列,为异构并行计算在中国的推广做出贡献。

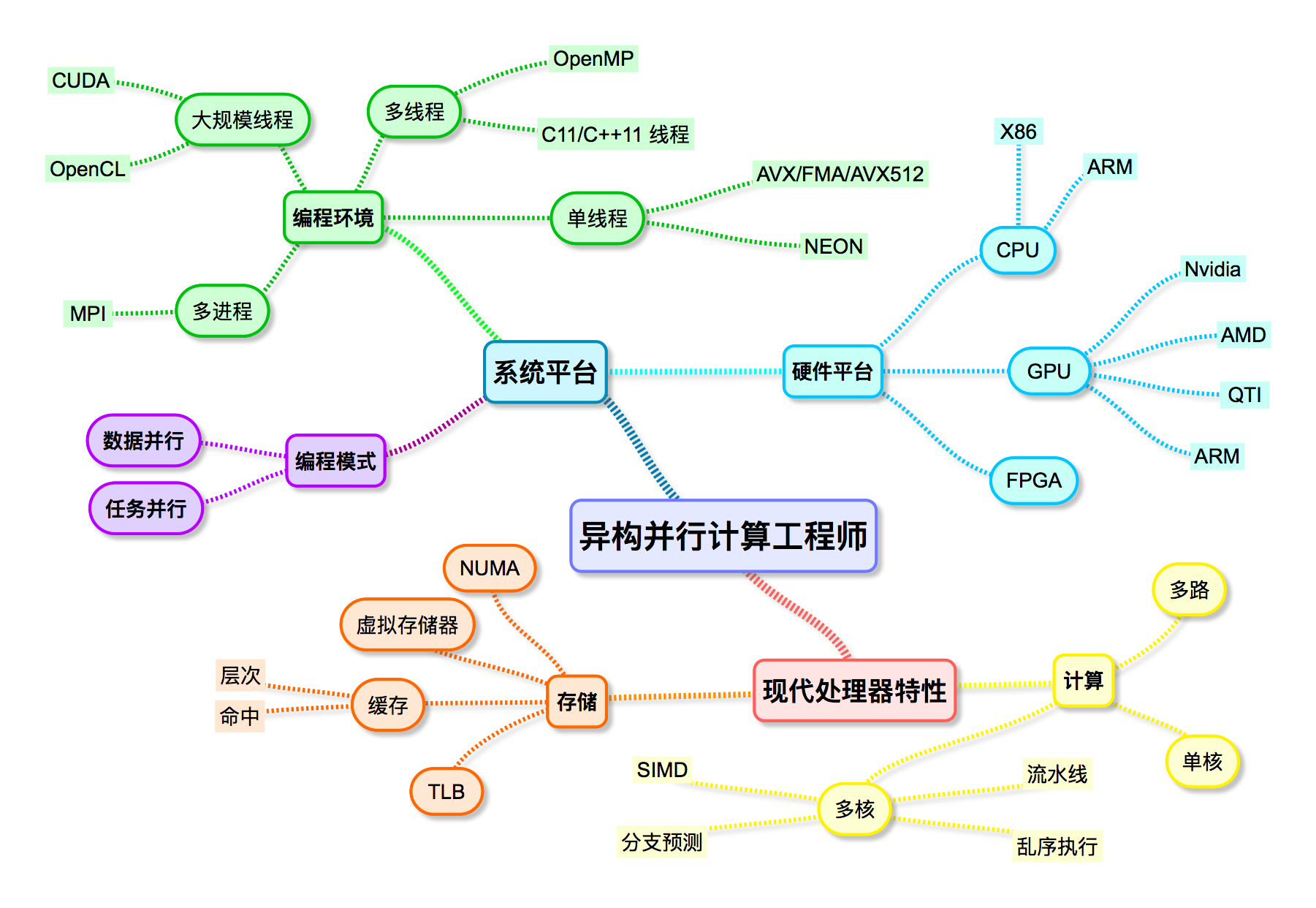

异构并行计算工程师技能树

要想成为一个优秀的异构并行计算工程师需要掌握许多知识和技能,这些技能可以分为两个方面:

- 处理器体系,处理器如何执行具体的指令;

- 系统平台方面,这又可以分成多个细的主题,包括硬件的特点,软件编程相关的平台和基础设施。

读者可以从图1具体了解到异构并行计算工程师需要掌握的技能和知识。

图1 异构并行计算工程师技能树

异构并行计算工程师成长详解

每个人甚至每个技术领域都是在不停的成长,通常公司的岗位会区分为初级、中级、高级、主任等,这是按照贡献、能力和责任大小来分,并不适合用来表示技术。为了更好地帮助读者学习知识,本文从技能体系角度来分析,因此并不能对应到各个公司招聘的岗位需求上,也意味着读者不能简单的把本文的技能和各个公司的岗位级别对应。

为了帮助读者更好地理解,本文会使用先硬件后软件的方式介绍。和异构并行工程师相关性最大的硬件知识即处理器特性,我们从这一点开始。

现代处理器的特性

从系统启动到终止,处理器一条接着一条地执行存储器中的指令,站在使用者的角度来看就好像是前一条指令执行完之后下一条指令才开始执行,是一个完完全全的串行过程。实际上,现代处理器利用了指令级并行技术,同一时刻存在着多条指令同时被执行,并且处理器执行指令的顺序无需和汇编代码给出的指令顺序完全一致,编译器和处理器只需要保证最终结果一致即可,这类处理器称为“乱序执行处理器”。而严格按照顺序一次执行一条指令,只有前一条执行完才开始执行后一条指令的处理器,称为“按序处理器”。而即使是在按序执行处理器上,编译器也可以对源代码进行类似的优化,以提高程序性能。对于一个特定的流水线来说,现代乱序执行处理器只保证指令执行阶段可以乱序,而其他阶段通常还是顺序的。目前主流的CPU和GPU,甚至DSP,无论是在服务器端,还是在移动端基本上都已经是乱序执行处理器了。

今天大多数处理器都是哈佛架构的变体,其根本特征是在程序执行时把指令和数据分开存储,程序员通常可以忽略指令存储,实际上异构并行计算更关注的是:计算和数据访问。

计算和访存

以作者正在使用的处理器E5-2680v3来说,其主频为2.6GHz,支持FMA指令集,其单核单精度浮点计算能力为2.6*2*8*2=83.2 GFlops;而单通道内存的带宽大约为20GB/s。主流处理器的处理速度远快于内存读写速度,为了减小访问数据时的延迟,现代主流处理器主要采用了两种方式:

- 利用程序访问数据的局部性特点:采用了一系列小而快的缓存保存正在访问和将要被访问的数据,如果数据会被多次访问且数据能够被缓存容纳,则能够以近似于内存的价格获得近似于缓存的速度;

- 利用程序的并行性:在一个控制流由于高延迟的操作而阻塞时,执行另一个控制流,这样能够提高处理器核心的利用率,保证处理器核心一直在忙碌的状态。

简单来说,前一种方法是将经常访问的数据保存在低延迟的缓存中,以减少访问数据时的延迟,通过更快为处理器提供数据而提高性能,主要是目前主流的CPU采用。而后一种方法则尽量保证运算单元一直在忙碌工作,通过提高硬件的利用率以提高程序的吞吐量,这种方法目前主要为主流的GPU所采用。这两种办法没有天然的壁垒,现代处理器(无论是CPU还是GPU)都采用了这两种方法,区别只是更偏重于使用哪一种方法。

指令级并行

现代处理器具有许多和代码性能优化相关的特点,本节主要介绍以下部分:

-

指令级并行技术:主要有流水线、多发射、VLIW、乱序执行、分支预测、超标量等技术;

向量化:主要有SIMT和SIMD技术; - 软件开发人员如果了解现代多核向量处理器的这些特性,就能写出性能效率超过一般开发人员的代码。

多核

多核是指一个CPU模块