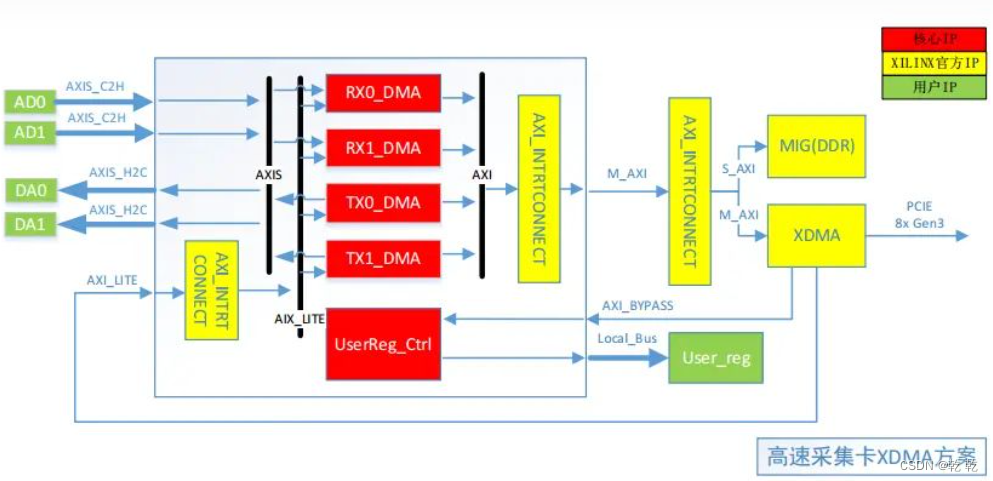

基于Xilinx FPGA 的PCIE开发教程

一、XDMA配置

- 创建一个BD文件

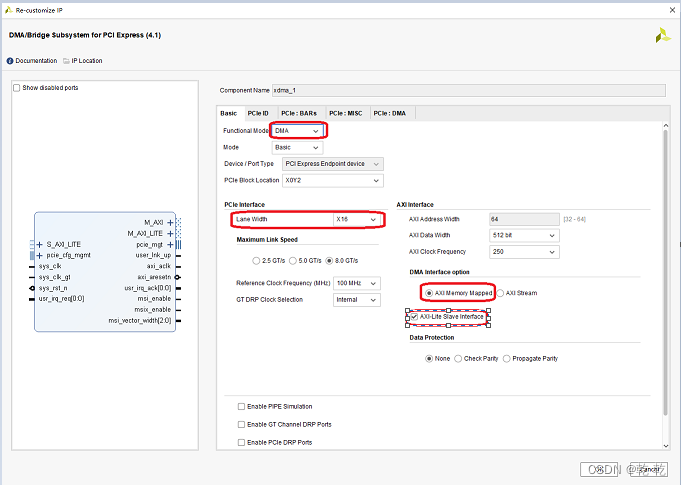

2. 添加PCIE的IP

选择这个IP对应的

用户接口为AXI4或者AXI4-stream

3. 双击IP,进行配置

参数:

(1) PCIe Block Location

选择PCIe所在quad,该选择会生成特定的引脚和区域约束文件和引脚分配,有的FPGA芯片有多个PCIe location,在选择芯片的时候也可以看到。

(2) Lane Width

选择用多少通道进行传输,下面是PCIe理论传输速度表格:

3)AXI data Width

AXI主要用于传输数据,传输带宽64或128可选。

(4)Maximum Link Frequency

每个传输通道的最大速度

(5) AXI Clock Frequency

选择AXI参考时钟,根据位宽的不同,时钟是固定的。

(6)DMA Interface option

接口选择AXI

(7)AXI4-Lite Slave

可选,用来将XDMA 内部寄存器开放给用户逻辑,用户逻辑可以通过此接口访问 XDMA内部寄存器,不会映射到BAR。

我这里没有选择

。

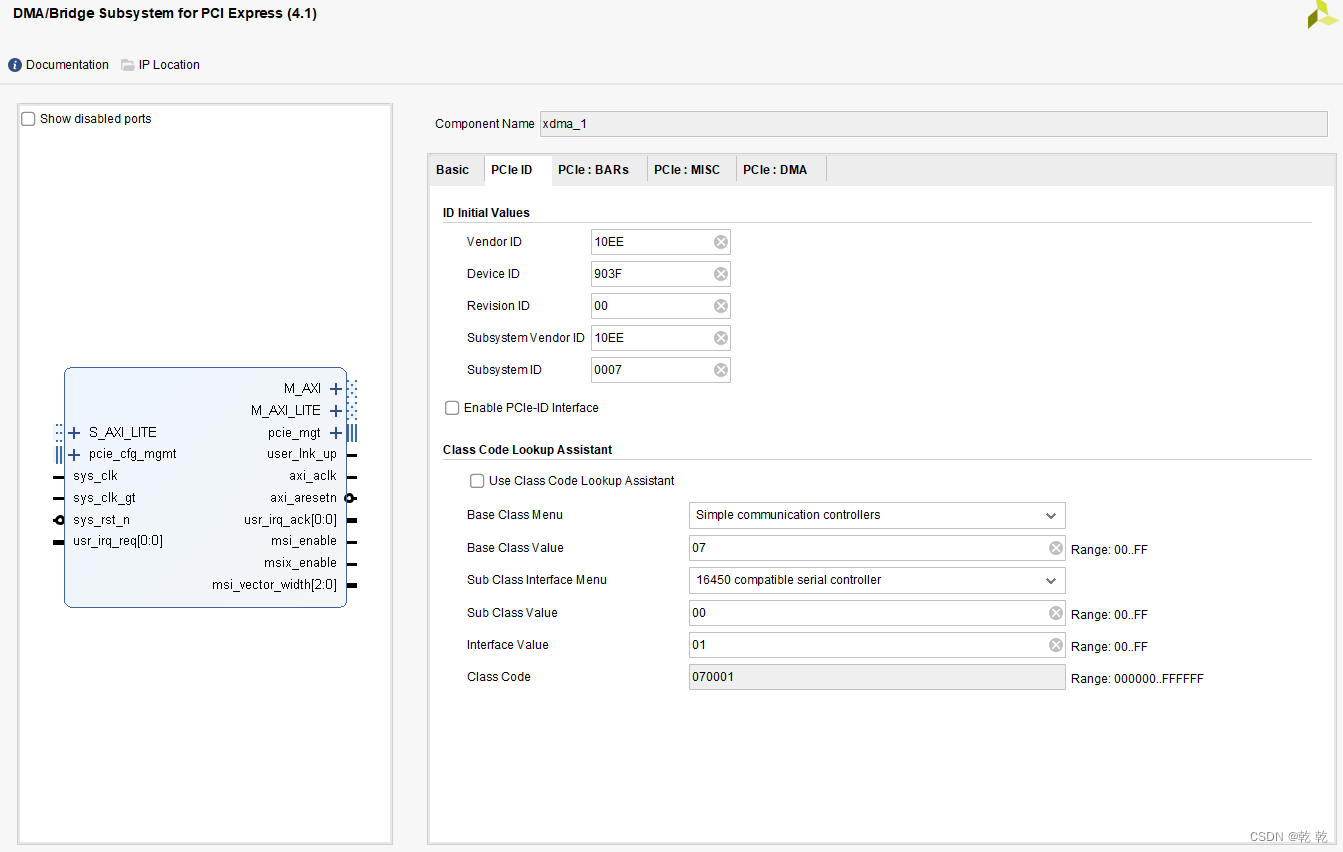

PCIe 的几个ID不需要更改:

1)PCIE to AXI Lite Master Interface

主机一侧通过PCIE 来访问用户逻辑侧寄存器或者其他AXI4-Lite 总线设备。

(2)size

选择1M,可以根据实际需要大小进行配置。

(3) PCIE to AXI Translation

通常情况下,主机侧PCIE BAR 地址与用户逻辑侧地址是不一样的,这个设置就是进行BAR 地址到AXI 地址的转换,比如主机一侧 BAR 地址为0,IP 里面转换设置为 0x80000000,则主机访问 BAR 地址 0 转换到AXI LIte 总线地址就是0x80000000。

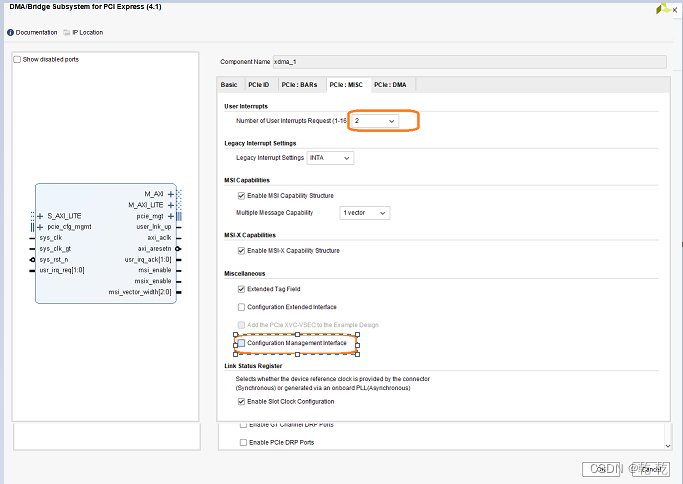

上面这页是DMA中断的配置,共提供16条中断线。

Legacy Interrupt:传统中断,非MSI中断,PCI设备使用INTx中断请求的方式与电平触发类似,而MSI/MSI-X中断请求的方式与边沿触发方式类似。当PCI设备的INTx信号有效时,PCIe桥将该信号转换为Assert_INTX消息报文,当这些INTx信号无效时,PCIe桥将该信号转换为Deassert_INTx中断信号。

注意:MSI 中断和 MSI-X 中断只能选择一个,否则会报错,如果选择了 MSI 中断,则可以选择 Legacy 中断,如 果选择了 MSI-X 中断,那么 MSI 必须取消选择,同时Legacy 也必须选择None。此 IP 对于7 系列设置有这个问题,如果使用Ultrascale 系列,则可以全部选择。

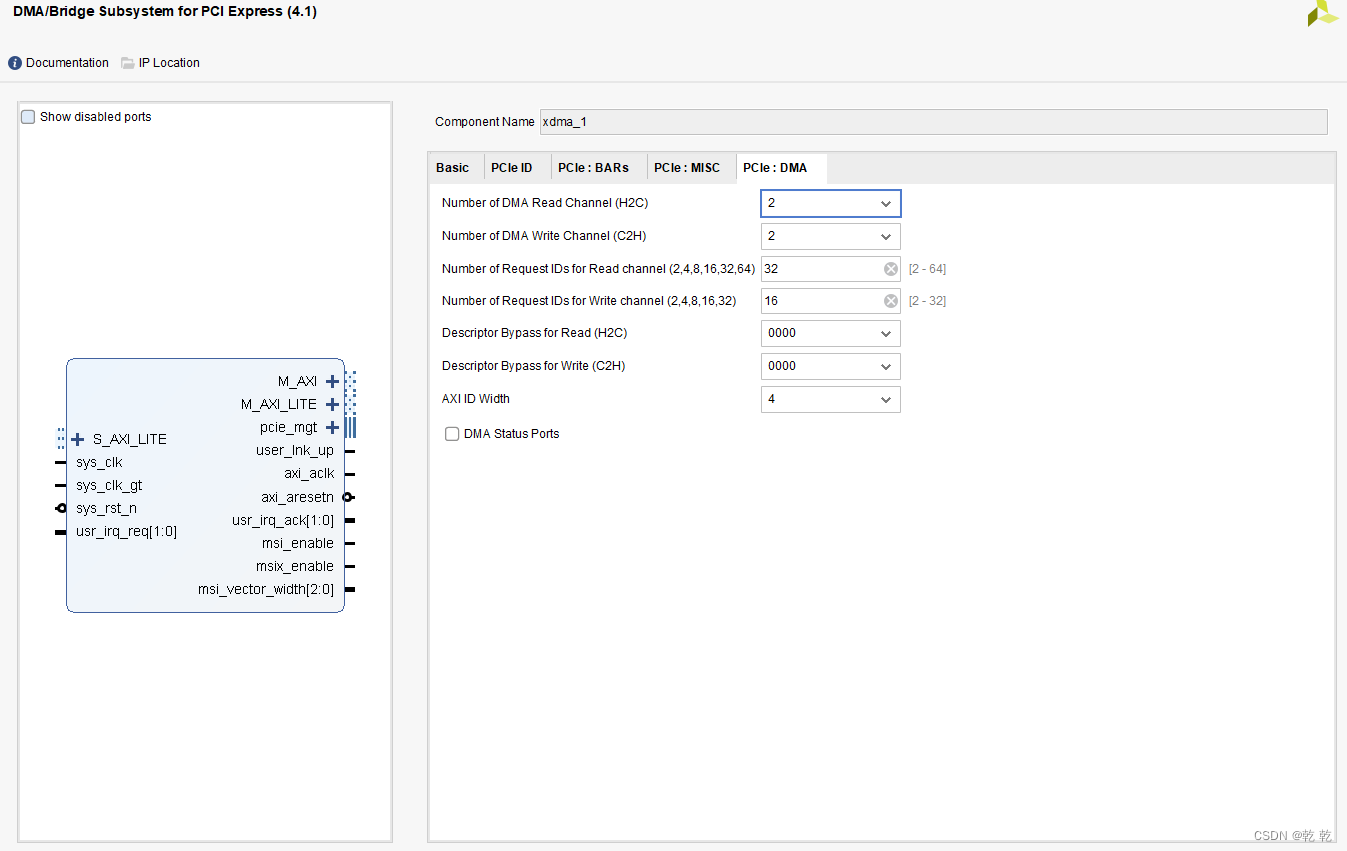

(1) Number of DMA Read Channel( H2C)& Number of DMA Write Channel(C2H)

对于PCIE2.0 来说最大只能选择 2,也就是 XDMA 可以提供最多两个独立的写通道和两个独立的读通道, 独立的通道对于实际应用中 有很大的作用,在带宽允许的前提前,一个PCIE 可以实现多种不同的传输功能,并且互不影响。

注意:

多通道时在AXI Stream模式下影响很明显,在AXI Stream模式下选择多通道,可以连接不同的数据源。在AXI Memory Mapped模式下影响不大。

(2)Number of Request IDs for Read (Write) channel

这个是每个通道设置允许最大的 ID 数量,按照默认即可。

![]()

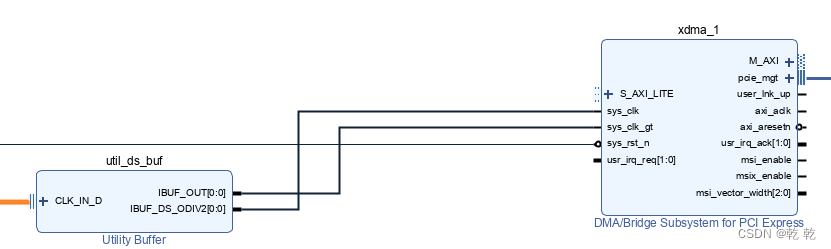

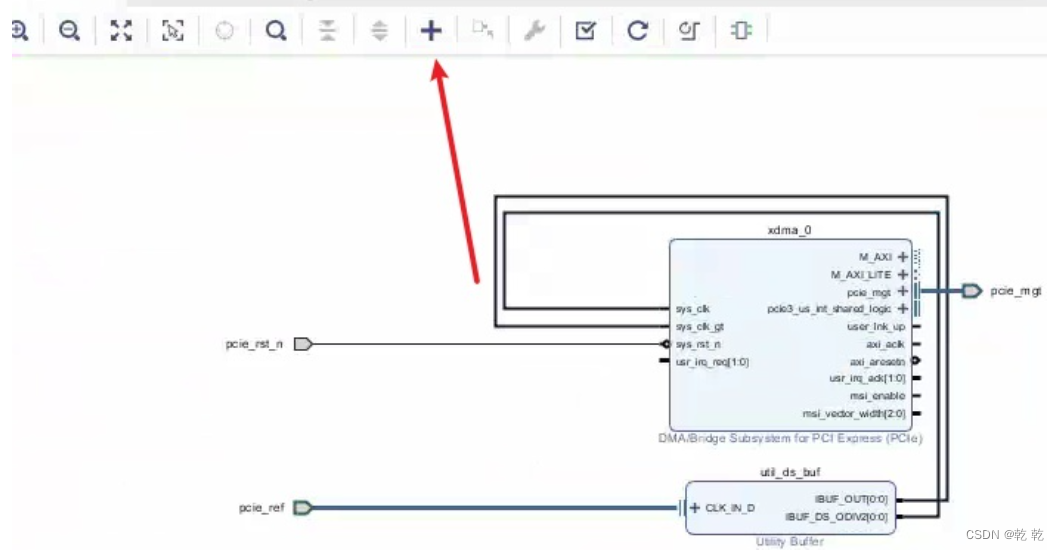

这个位置可能会自己更改,我们改成和XDMA IP核相同的配置即可。下图1、2、3分别代表PCIe的复位、时钟、接口,可以通过双击端口进行名字的修改:

至此,XDMA配置完毕。

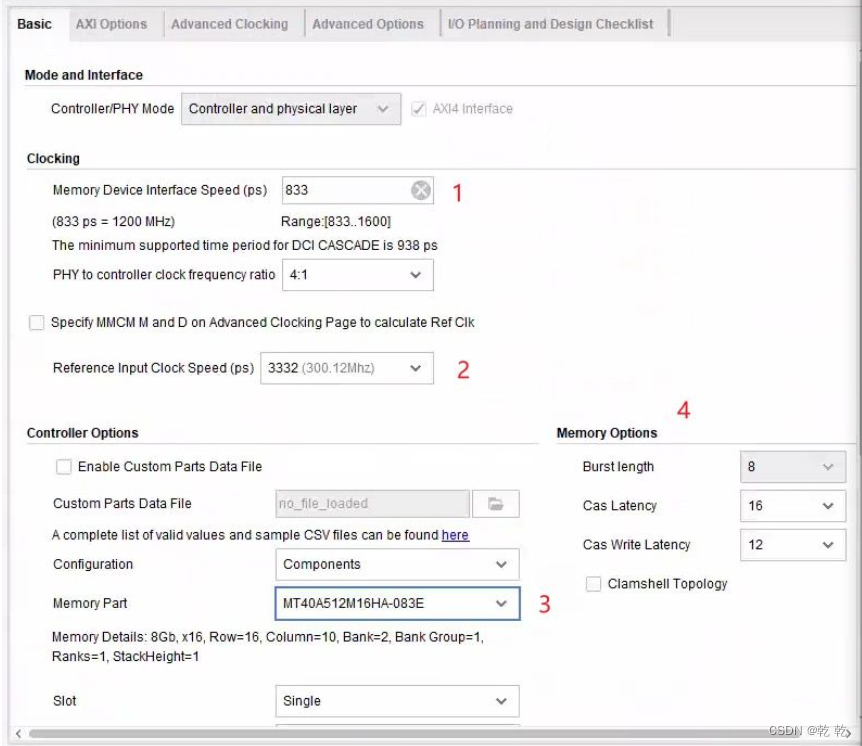

二、MIG的配置

这里需要接板卡上的DDR,如果相接BRAM,这里可以跳过。

MIG(Memory Device interface speed)本质是一个内存控制器,IP核的输出接口和内存相连。

根据实际型号进行选择即可:

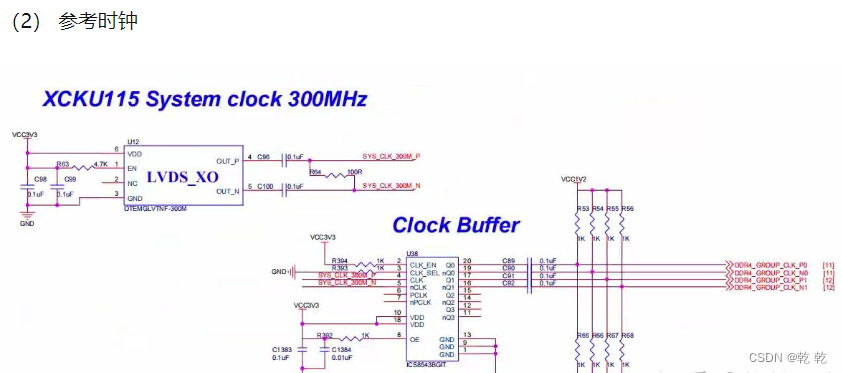

(1) Memory Device interface speed

表示的是外部时钟频率1.2G,所以它的数据传输速率为2.4G,带宽为2.4G×64/8 = 19.2GB

根据板卡的实际情况进行选择。

根据板卡的实际型号进行选择即可。

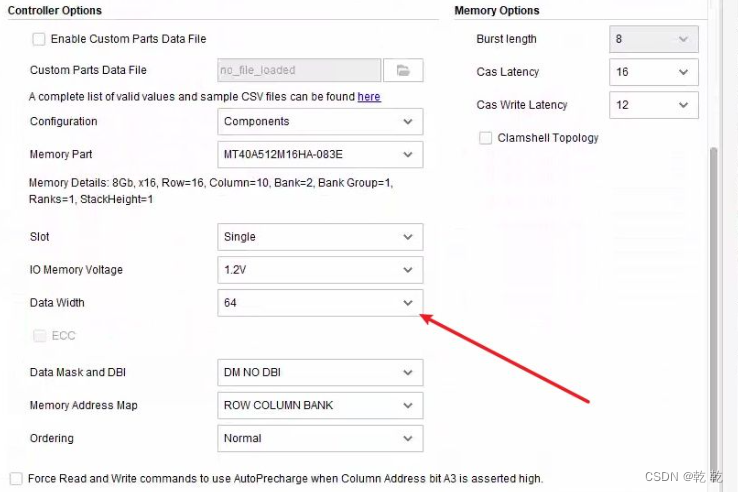

(4)这里还不是很清晰要怎么选择

选择64位位宽,这就是上面速率计算的原理。

其它栏目的选项直接默认即可。

生成MIG IP后,分别点:

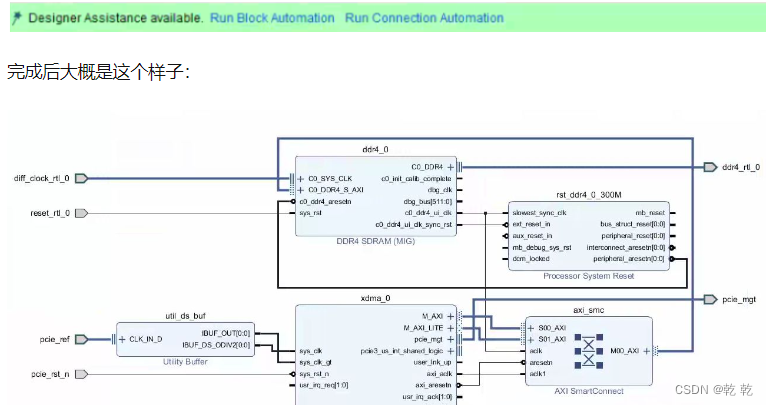

这里多了两个IP,一个是asi_smc,另一个是rst_ddr4_0_300M

- asi_smc功能

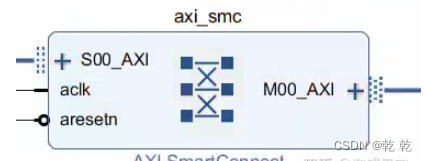

给位宽转换提供足够的时间,与AXI_interconnect IP功能相似,后续的文章不再使用它,换成AXI_interconnect IP。这里点开IP,把时钟改成1个

2. rst_ddr4_0_300M

Xilinx处理器系统复位模块允许客户通过设置某些参数来启用/禁用功能,从而根据自己的应用来定制设计。

想详细了解的可以参考下面的文章(这个IP不需要做任何的修改):

Xilinx IP解析之Processor System Reset v5.0_徐晓康的博客的博客-CSDN博客_proc_sys_reset

修改axi_smc后的,Diagram如下:

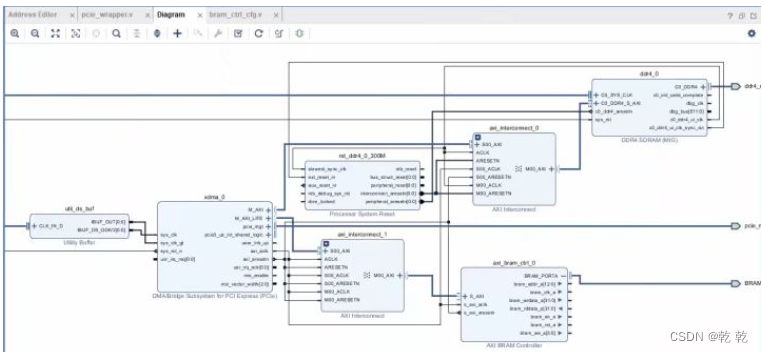

host如何通过AXI4接口读写DDR(或者BRAM)和通过AXI-LITE接口读写控制信号,BD图如下图所示:

可以看到M_AXI通过interconnecte IP连接到DDR4,M_AXI_LITE通过interconnecte IP连接到bram_ctrl,将BRAM_PORTA引出,在FPGA侧进行控制信号的读写。

软件开发

FPGA:赛灵思KU115

HOST:ubuntu 18.04

Driver:XDMA,具体安装方法参考

HiFive Unmatched开发板安装XDMA(linux安装XDMA) – 知乎

HOST主要代码:

主函数中,通过调用pcie初始化,写控制,读控制,写数据、读数据。

# include "stdio.h"

#include <assert.h>

#include <fcntl.h>

#include <getopt.h>

#include <stdint.h>

#include <stdio.h>

#include <stdlib.h>

#include <string.h>

#include <unistd.h>

#include <time.h>

#include <pthread.h>

#include <semaphore.h>

#include <stdarg.h>

#include <syslog.h>

#include <sys/mman.h>

#include <sys/stat.h>

#include <sys/time.h>

#include <sys/types.h>

#include <sys/sysinfo.h>

#include <unistd.h>

#include <dirent.h>

#include <string.h>

/* ltoh: little to host */

/* htol: little to host */

#if __BYTE_ORDER == __LITTLE_ENDIAN

# define ltohl(x) (x)

# define ltohs(x) (x)

# define htoll(x) (x)

# define htols(x) (x)

#elif __BYTE_ORDER == __BIG_ENDIAN

# define ltohl(x) __bswap_32(x)

# define ltohs(x) __bswap_16(x)

# define htoll(x) __bswap_32(x)

# define htols(x) __bswap_16(x)

#endif

#define MAP_SIZE (1024*1024UL)

#define MAP_MASK (MAP_SIZE - 1)

#define FPGA_AXI_START_ADDR (0)

void *control_base;

int control_fd;

int c2h_dma_fd;

int h2c_dma_fd;

static unsigned int h2c_fpga_ddr_addr;

static unsigned int c2h_fpga_ddr_addr;

static int open_control(char *filename)

{

int fd;

fd = open(filename, O_RDWR | O_SYNC);

if(fd == -1)

{

printf("open control error\n");

return -1;

}

return fd;

}

static void *mmap_control(int fd,long mapsize)

{

void *vir_addr;

vir_addr = mmap(0, mapsize, PROT_READ | PROT_WRITE, MAP_SHARED, fd, 0);

return vir_addr;

}

void write_control(int offset,uint32_t val)

{

uint32_t writeval = htoll(val);

*((uint32_t *)(control_base+offset)) = writeval;

}

uint32_t read_control(int offset)

{

uint32_t read_result = *((uint32_t *)(control_base+offset));

read_result = ltohl(read_result);

return read_result;

}

void put_data_to_fpga_ddr(unsigned int fpga_ddr_addr,short int *buffer,unsigned int len)

{

lseek(h2c_dma_fd,fpga_ddr_addr,SEEK_SET);

write(h2c_dma_fd,buffer,len*2);

}

void get_data_from_fpga_ddr(unsigned int fpga_ddr_addr,short int *buffer,unsigned int len)

{

lseek(c2h_dma_fd,fpga_ddr_addr,SEEK_SET);

read(c2h_dma_fd,buffer,len*2);

}

int pcie_init()

{

c2h_dma_fd = open("/dev/xdma0_c2h_0",O_RDWR | O_NONBLOCK);

if(c2h_dma_fd < 0)

return -1;

h2c_dma_fd = open("/dev/xdma0_h2c_0",O_RDWR );

if(h2c_dma_fd < 0)

return -2;

control_fd = open_control("/dev/xdma0_user");

if(control_fd < 0)

return -5;

control_base = mmap_control(control_fd,MAP_SIZE);

return 1;

}

void pcie_deinit()

{

close(c2h_dma_fd);

close(h2c_dma_fd);

close(control_fd);

}

unsigned int len = 4096;

int read_fftdata(short int *buf1){

FILE *fpread=fopen("fft_linux.txt","r");

if(fpread == NULL) return 1;

for(int i=0;i<len;i++) fscanf(fpread, "%hd", &buf1[i]);

return 0;

}