在本文中,我们将了解采样和保持电路。它们是模数转换器的关键部分,有助于将模拟信号精确转换为数字信号。我们将看到一个简单的示例并保持电路,它的工作原理,不同类型的电路实现以及一些重要的性能参数。

目录

简介

采样保持电路,有时表示为S/H电路或S&H电路,通常与模数转换器一起使用来采样输入模拟信号并保持采样信号,因此得名为采样保持电路。

在采样保持电路中,模拟信号被采样很短的时间间隔,通常在10微秒到1微秒的范围内。此后,采样值保持不变,直到下一个要采样的输入信号到达。保存样品的持续时间通常在几毫秒到几秒之间。

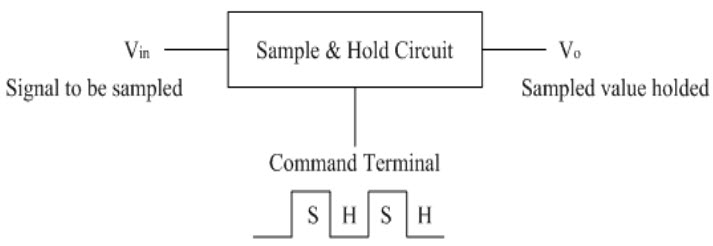

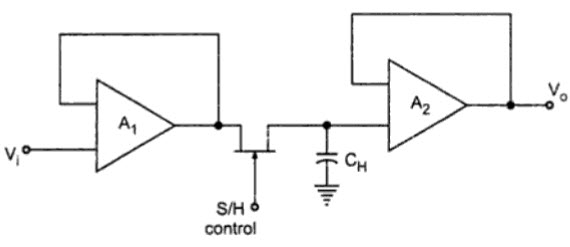

下图显示了一个典型的采样保持电路的简单框图。

采样保持电路的实现要求

如果ADC的输入模拟电压变化超过±1/2 LSB,则很有可能输出数字值是错误的。为使ADC产生准确的结果,输入模拟电压应在转换期间保持恒定。

顾名思义,采样保持电路根据采样命令对输入模拟信号进行采样,并将输出值保持在其输出端,直到下一个采样命令到达。

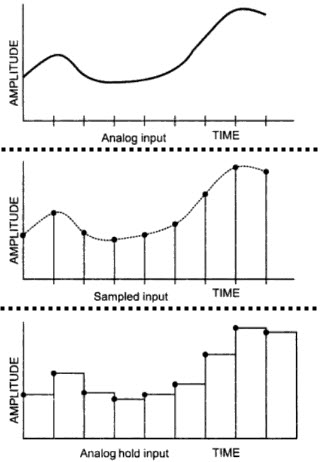

下图显示了典型采样保持电路的输入和输出。

采样保持电路的基本组成

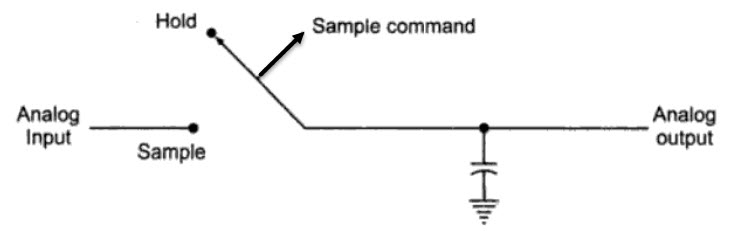

借助一个简化的电路图来了解采样保持电路电路的工作原理

该采样保持电路由两个基本组件组成:

*

模拟开关

*

保持电容

该电路跟踪输入模拟信号,直到采样命令变为保持命令。在保持命令之后,电容器在模数转换期间保持模拟电压。

模拟开关

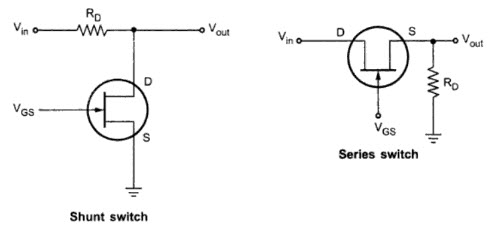

任何场效应管FET,如JFET或MOSFET,都可以用作模拟开关。在这次讨论中,将集中讨论JFET。通过控制栅源电压VGS切换JFET的通断。

当Vgs等于0V时,JFET相当于一个断开的开关。当VGS为较大的负电压(即比VGS(OFF)更负)时,JFET相当于一个闭合的开关。

模拟开关可以是并联模拟开关或串联模拟开关,具体取决于其相对于输入和输出的位置。下图给出了并联模拟开关和串联模拟开关的JFET。

常见的采样保持电路类型

接下来给出几种不同类型的采样保持电路。下面提到的所有电路都使用 JFET 作为开关,其在采样期间,JFET 导通,保持电容中的电荷上升至输入模拟电压的电平。在采样周期结束时,JFET 关闭,保持电容与输入信号隔离。这确保输出电压保持恒定在输入电压值,而不管输入值的微小变化。

为了补偿保持电容器两端的低压降电压,使用了两个缓冲器(电压跟随器),一个在输入端,一个在输出端。

1. 开环型采样保持电路

由于没有反馈,该电路比闭环型采样保持电路相对更快。但是闭环架构中的反馈提供了更高精度的结果。采集时间(在下一节中讨论)必须尽可能短。它取决于三个因素:

* RC 时间常数,其中 R 是 JFET 的导通电阻 (ron),C 是保持电容 CH

* 最大输出电流

* 运算放大器的转换率

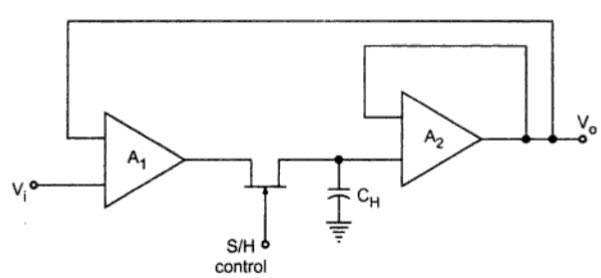

2. 闭环型采样保持电路

对开环型采样保持电路进行改进,得到闭环型采样保持电路。在这种配置中,JFET 的导通电阻被引入反馈回路,因此采集时间取决于其他两个因素,即:最大输出电流和运算放大器的转换率。

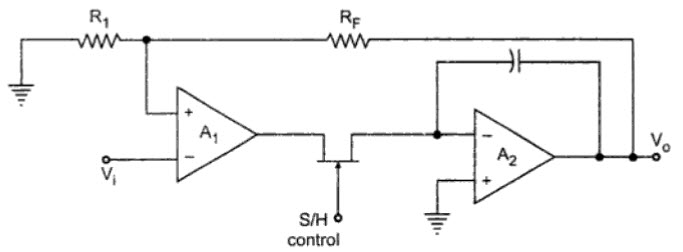

3. 可调增益的闭环型采样保持电路

与前一个电路相比,通过增加电阻,提供电压增益,将电路进一步改进。电路的电压增益可以使用输入电阻 R1 和反馈电阻 RF 计算如下:

4. 进一步改进

与之前的电路相比,最终电路具有更多优势。最重要的是保持电容的位置发生了变化,因此得到,A2 同相端的电压等于电容两端的电压除以 A2 的开环增益。这确保了保持电容器的更快充电时间和之后电路更短的采集时间。

性能参数

采样保持电路的性能可以通过放大器常用的参数来表征,例如输入失调电压、增益误差、非线性等。但是有一些特定于采样保持电路的特性。

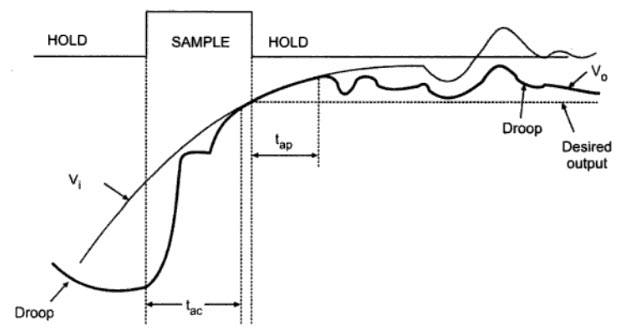

这些特性有助于分析其在从采样模式转换到保持模式(反之亦然)期间以及保持模式操作期间的性能。让我们借助下图了解这些特征。

采集时间tac

在采样期间保持电容中的电荷上升到接近输入电压的电平所需的时间称为采集时间。它受三个因素影响:

*

RC 时间常数

*

运算放大器的转换速率

*

运算放大器的最大输出电流

孔径时间(tap)

在Vo跟踪Vi的开始和保持命令的开始之间的时间延迟称为孔径时间。该延迟通常是由于通过驱动器和开关电路的传播延迟造成的。

为了进行精确的定时操作,必须提前一段孔径时间启动保持命令。

孔径不确定性 (Δ tap)

孔径时间对于所有样本而言并不相同,并且会因样本而异。这种不确定性称为孔径不确定性。这将严重影响保持命令的推进。

保持模式稳定时间 (ts)

保持模式稳定时间是指应用保持命令后输出 Vo 稳定在指定误差范围内(通常为 1%、0.1% 或 0.01%)所用的时间。

保持步长

在从采样模式切换到保持模式的过程中,可能存在开关和保持电容器之间不希望发生的电荷转移(主要是由于寄生电容)。这将影响电容器电压和输出电压。输出电压与所需电压的这种变化称为保持步长。

馈通

同样,开关中的寄生电容可能在保持模式下引起Vo和Vi之间的交流耦合。因此,输出电压可能会随着输入电压的变化而变化,这称为馈通。

保持电压下降

保持电压下降是指保持电容器两端的电压因泄漏电流而下降的现象。

采样保持电路的优点

典型采样保持电路的主要且重要的优点是通过保持采样的模拟输入电压来辅助模数转换过程。

在多通道ADC中,不同通道之间的同步很重要,采样保持电路可以通过同时采样所有通道的模拟信号来提供帮助。

在多路复用电路中,使用采样保持电路可以减少串扰

采样和保持电路的应用

模数转换电路(ADC)、数字接口电路、运算放大器、模拟解复用器、数据分配系统、多路复用器的输出存储脉冲调制系统

总结

本文给出了关于采样和保持电路的基本介绍。介绍了采样保持电路在模数转换器中的重要性、使用MOSFET和电容器的简单采样保持电路、不同类型的采样保持电路、决定采样保持电路性能的一些重要参数以及采样保持电路的应用。