一般拿到PDK除了要检查metal scheme,spice模型之外还要检查rule deck,比如calibre的LVS rule文件,DRC文件,post layout提取用的xrc_rule,如果是starrc抽取则是nxtgrd文件,qrc则是qrcTechfile;另外一些工具也需要用到ict文件,比如layout EAD(EXL)中EAD browser会用到ict文件,电磁抽取工具EMX也是如此。那么这些文件的关系如何呢?

原文链接

RC抽取中的几种工艺文件_瞳阳_新浪博客

RC抽取的过程需要用到工艺文件,一般会有以下几种:

Cadence Synopsys

ict <—> itf process file

captable <—> tluplus rc model for APR tools

qrcTechfile <—> nxtgrd rc model for stand alone RC Ext. tools

下面以Cadence的文件为例做一个简介:

1) ict

工艺文件,主要包括:

— 工艺参数:比如金属的厚度,金属层的方块电阻值,介质层的厚度,介质层的介电常数等。

— 工艺效应系数和PVT系数:比如线宽增大效应,温度系数等。

ict文件是ASCII格式的,是可读的,里面的主要内容还是比较容易看懂的。详细的格式可以参考:Encounter User Guide –> Appendix A: Creating the ICT File

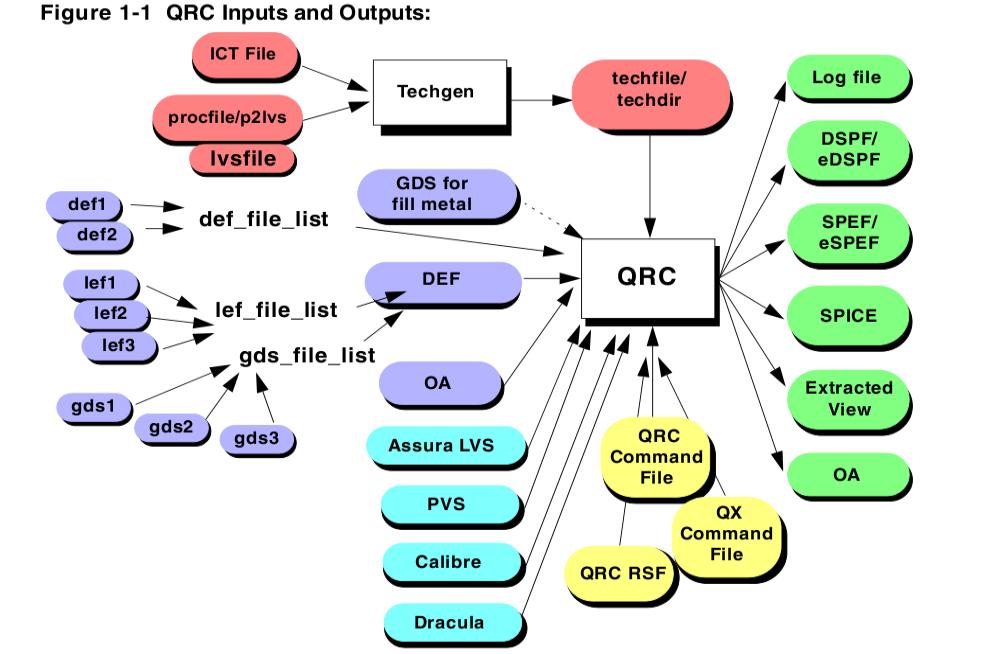

ict文件可以使用techgen命令(qrc)生成qrcTechFile,qrc吃qrcTechFile可以抽取后仿网表

使用EXT软件bin下的viewict可以在图形界面看到工艺层次,用法:EXT install path/bin/viewict xx.ict

2) captable

由ict文件生成,其内容主要是电容电阻的查表。通常由半导体厂提供。

因为ict文件是工艺参数,并不是直接的电阻电容值,如果直接使用,则每一段导线都要根据工艺参数去计算电阻电容,计算量太大。所以,为了减少RC抽取过程中的计算量,节省RC抽取的时间,将ict文件转换成captable。在captable中,由导线的长度和宽度查表即可得到电阻电容值,虽然过程中也要计算一些系数的影响(比如温度系数),但计算量仍然大幅减少了。由此可见,captable的生成过程就是由ict中的工艺参数按照一些特定的导线尺寸计算出相应电阻电容值的过程。生成时间在1~2天的量级。

captable用以下命令生成:generateCapTbl

该命令既可以在Encounter中执行(支持多线程/CPU);也可以单独运行(不支持多线程/CPU)。命令用法详见:Encounter Text Command Reference

captable的精度低于后文所讲的qrcTechfile,主要用于布线之前的步骤。何种阶段使用何种RC抽取引擎要在精度和运行时间之间进行折中。因为布线之前的步骤均使用预布线(trial route),所以没有必要使用qrcTechFile。

captable的详细介绍请参考:Encounter User Guide –> RC Extraction一章

3) qrcTechfile

也由ict文件生成,用于QRC引擎。通常由半导体厂提供。

其原理与captable相同,但对导线的3D建模更加精确,并且会考虑更多的工艺效应,所以其电阻电容值也更加精确。相应的,qrcTechfile的生成非常耗时,通常在10天的量级。

qrcTechfile用以下命令生成:Techgen。这是一个小工具,可以在Encounter的安装目录下找到。具体用法请参考:QRC Techgen Reference Manual

QRC引擎是具有signoff质量的RC抽取工具,一般从routing开始就应该使用QRC引擎进行RC抽取,以获得较高的精度,加速时序收敛。