简介

-

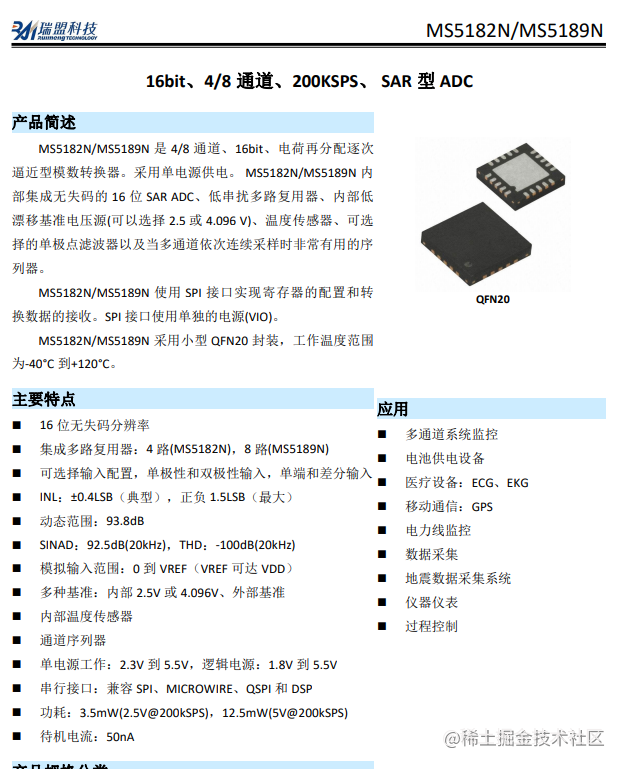

MS5182N

芯片是瑞盟科技的一款4通道的16位

SAR ADC

芯片,其对标的是

ADI

的

AD7682

芯片,或者说基本上两者功能一样,可以作为国产替代。另外其

MS5189

(8通道的)对标的则是

AD7689

。我此次项目中仅使用了

MS5182N

。不过还是吐槽一下,其数据手册做的真是无语,虽然明显有直接从

AD7682

上抄过来的,不过抄的也是不忍足视,我都怀疑其有做详细勘检没。鉴于此,最后我还是直接用

AD7682

的数据手册。

芯片操作

-

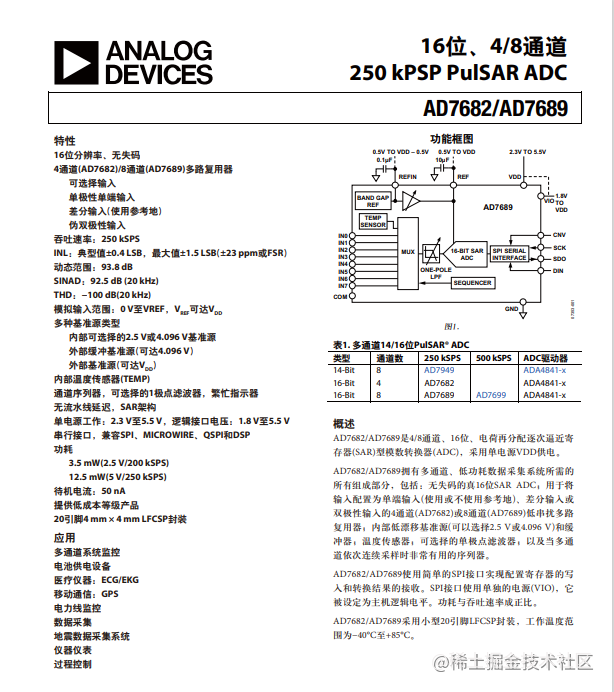

芯片拿到手对于软件或者驱动层开发的人来说,首先关注的是其总线操作方式,以及了解时序操作和寄存器内容了。该芯片是

(Q)SPI

接口的。

读写操作

1.该芯片有两种状态三种读写数据模式。

-

含繁忙指示器

-

RDC (转换期间读取/写入)

- 此模式适合高速SPI

-

RAC (转换后读取/写入)

- 此模式适合任何速度SPI

-

RSC (转换全程读取/写入)

- 此模式适合任何速度SPI

-

RDC (转换期间读取/写入)

-

不含繁忙指示器

-

RDC (转换期间读取/写入)

- 此模式适合高速SPI

-

RAC (转换后读取/写入)

- 此模式适合任何速度SPI

-

RSC (转换全程读取/写入)

- 此模式适合任何速度SPI

-

RDC (转换期间读取/写入)

2.是否使用繁忙指示器,是根据转换结束后的CNV的电平操作状态。

- 如果转换结束后,将CNV置高,则表示禁用(不使用)繁忙指示器。

- 如果转换结束后,将CNV拉低,则表示使用繁忙指示器。

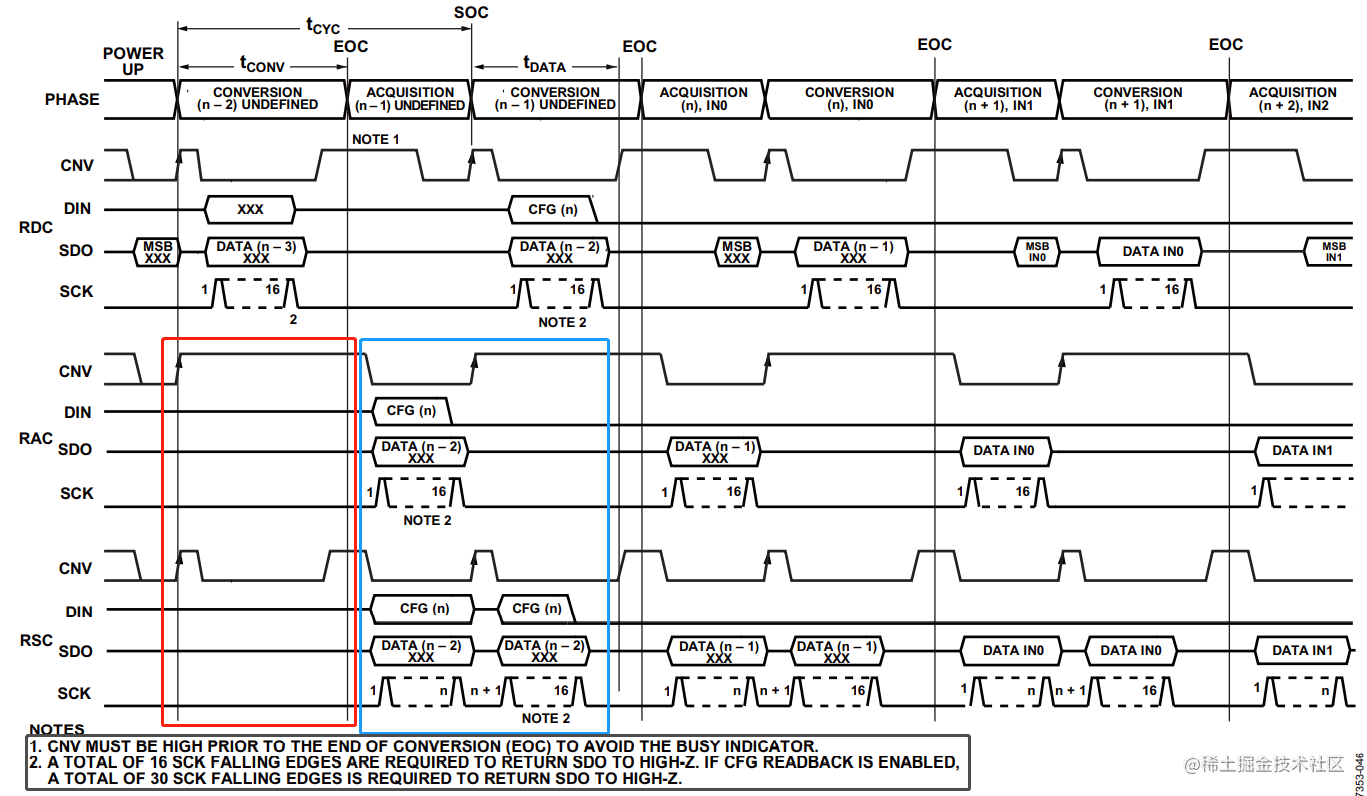

三种读写数据模式的时序解读

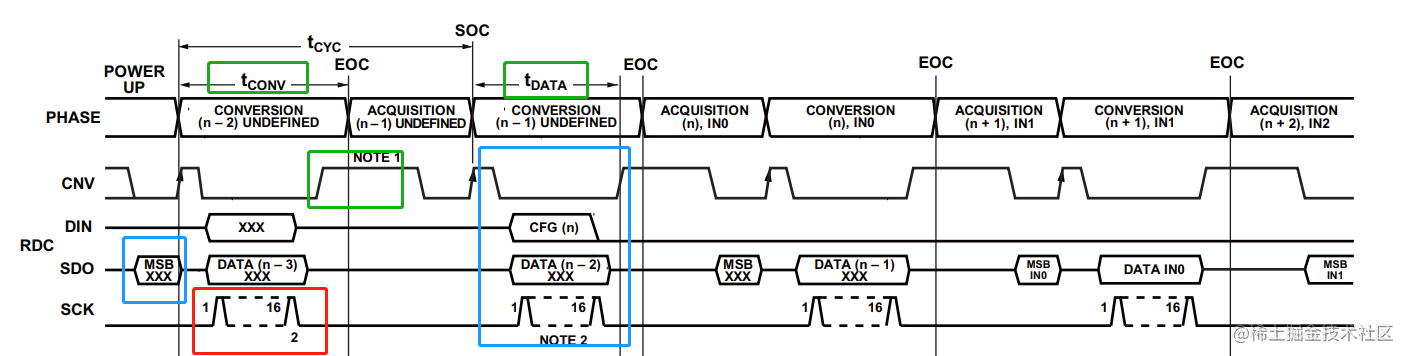

1.RDC (转换期间读取/写入)

-

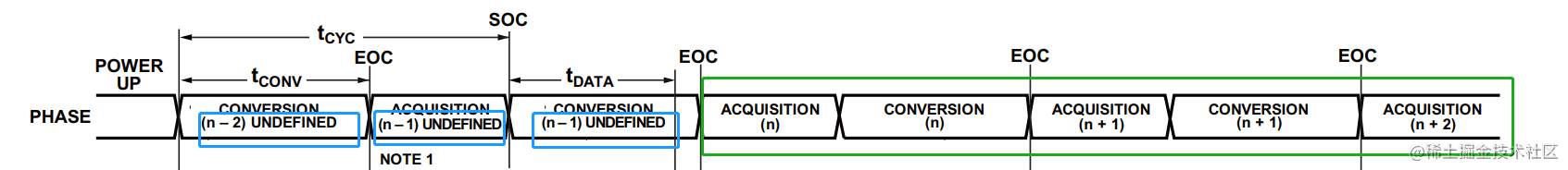

不含繁忙指示器的时序图:

-

注:

-

tCONV

:指转换指令写入时间 -

tCYC

: 转换+采集数据的时间 -

tDATA

:读取数据的时间/转换配置指令发送

-

-

注:

-

从

SCK

时钟信号时序图可以知道,该模式下发送转换指令是需要

16个时钟

,意思就是每次发送指令时要

连续写入两字节

的指令数据(因为

ADC

是

16bit

的)。-

在(

POWER UP

)上电之后,发送(可以是无效配置(

xxx

))转换命令(同时也是读取

n-2

次的数据,但因为时刚上电,所以读取的也是无效的转换数据,

真正的数据是在第一次配置有效指令2次读取之后[就是tDATA那次有效配置开始]

)之后,将

CNV

拉高(即不使用繁忙指示器)一段时间后,进入数据采集(

ACQUISION

)状态,然后再将CNV拉低一段时间,采集结束,然后再将

CNV

拉高,发送

CFG(n)

(

指第n次配置参数

)指令,当前也是读取第

(n-2)

次的转换数据时刻,如此反复之。

!!!所以读取数据时,需要注意的时在写当前配置参数时

CFG(n)

,同时接收的是

前2次CFG(n-2)

发出配置指令下的转换数据。

有此图上电后的两次转换是无意义(

CONVERSION UNDEFINEED

)的,数据直接丢弃。

-

在(

-

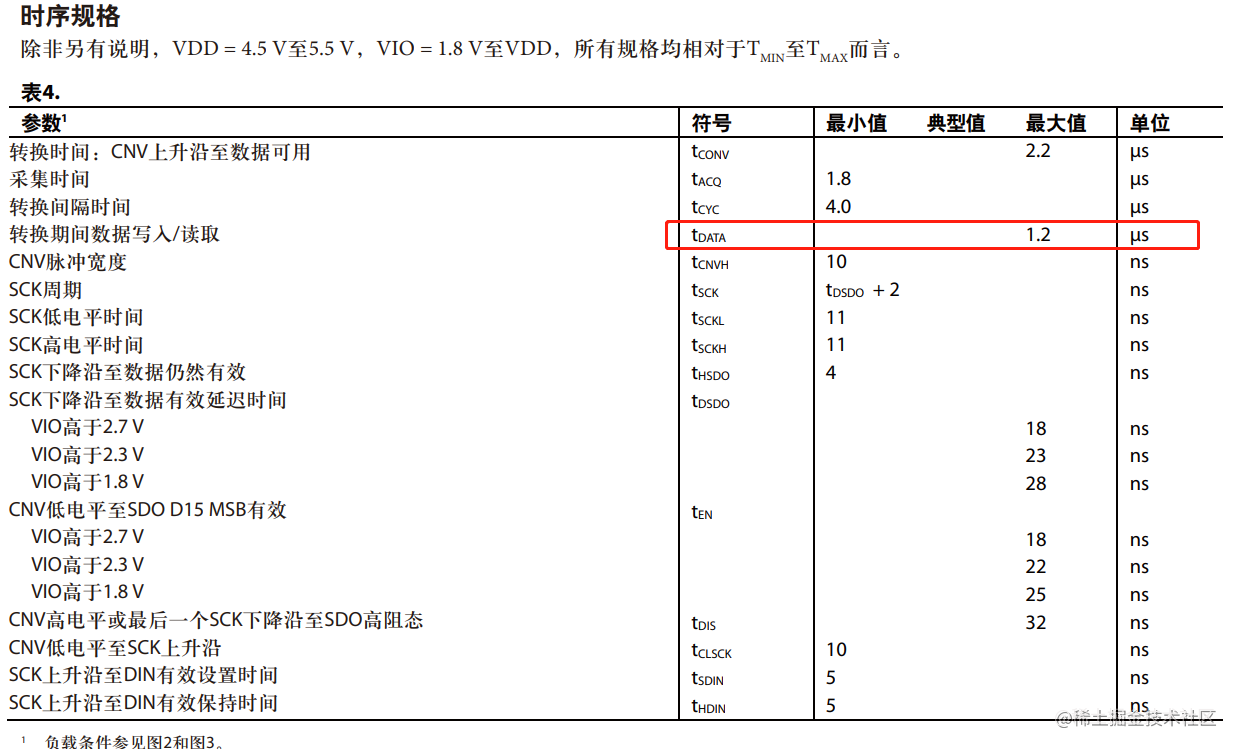

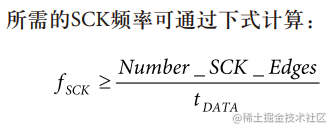

因为数据读取/写入是在

tDATA

期间,而此时间是有严格时间控制的,见下图。

所以对时钟要求较高,如下图:

一般用于高速

SPI

(或者说常见

MCU

模拟

SPI

可能不适合该

RDC

模式)

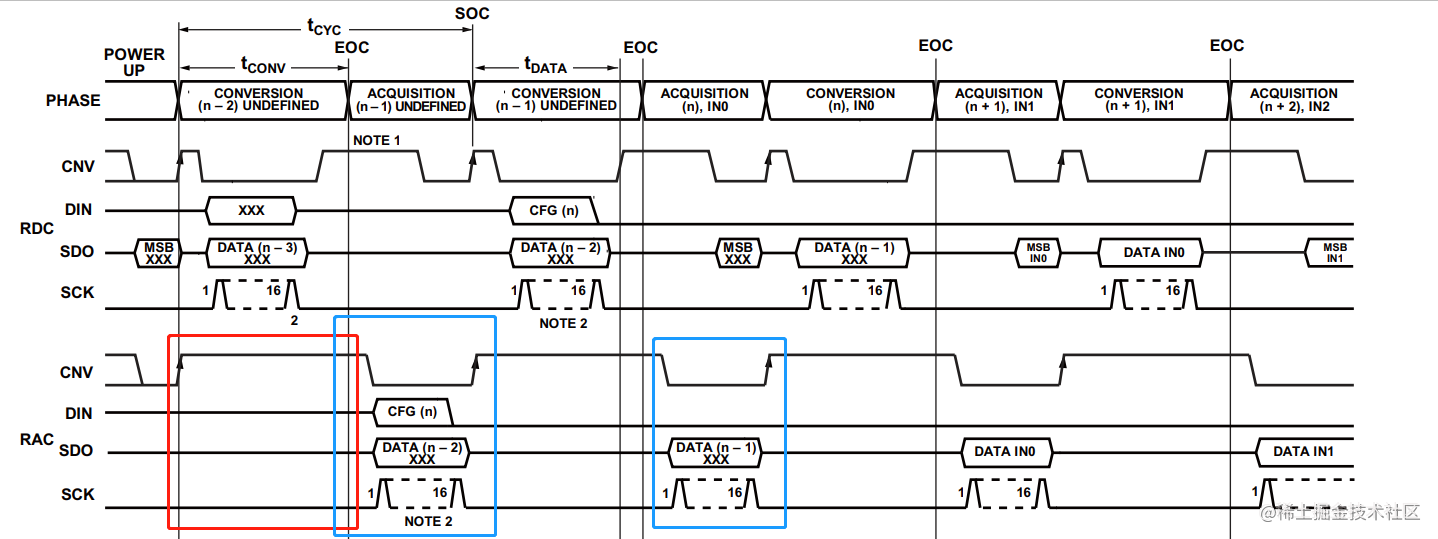

2.RAC (转换后读取/写入)

-

不含繁忙指示器的时序图:

-

注:

-

tCONV

:指转换指令写入时间 -

tCYC

: 转换+采集数据的时间 -

tDATA

:读取数据的时间/转换配置指令发送

-

-

注:

-

相比于上面

RDC

模式,从

RAC

模式的时序图看到,在上电后(

POWER UP

),不是在转换期间(

tCONV

)时发送配置(也是读取

第(n-2)次

配置指令转换的数据),而是在采集期间(

ACQUISION

)发送配置,在转换期间时,

CNV

引脚时拉高状态,在经过(

tCONV

)时间后,然后再拉低。 -

因为数据读取/写入发生在

tACQ

期间,而此时间没有最大限制,见下图,所以低速度

SPI

也可以使用。

3.RSC (转换全程读取/写入)

-

不含繁忙指示器的时序图:

-

注:

-

tCONV

:指转换指令写入时间 -

tCYC

: 转换+采集数据的时间 -

tDATA

:读取数据的时间/转换配置指令发送

-

-

注:

-

相比于

RAC

模式,从

RSC

模式的时序图看到,其时序读写类似,上电后(

POWER UP

),其不是在转换期间(

tCONV

)时发送配置(也是读取

第(n-2)次

配置指令转换的数据),而是在采集期间发送配置,但在上电后(

POWER UP

)后进入转换期间(

tCONV

)时,

CNV

引脚有一个先拉高再拉低的过程,然后在发送配置指令(读取数据)是在采集(

ACQUISION

)和转换整个时期,且其是将配置指令拆分成两次发送,每次发送8字节(从

SCK

时钟可以看出),且在采集(

ACQUISION

)和转换的时刻有一个CNV拉高再拉低的变化。可以认为其是

SPI

的

8bit

数据读写模式,而前面是SPI的

16bit

读写模式。 -

因为数据读取/写入发生在

tACQ+tDAT

A期间,参考上面

RAC模式

,而此时间没有最大限制,见上图,所以低速度

SPI

也可以使用。

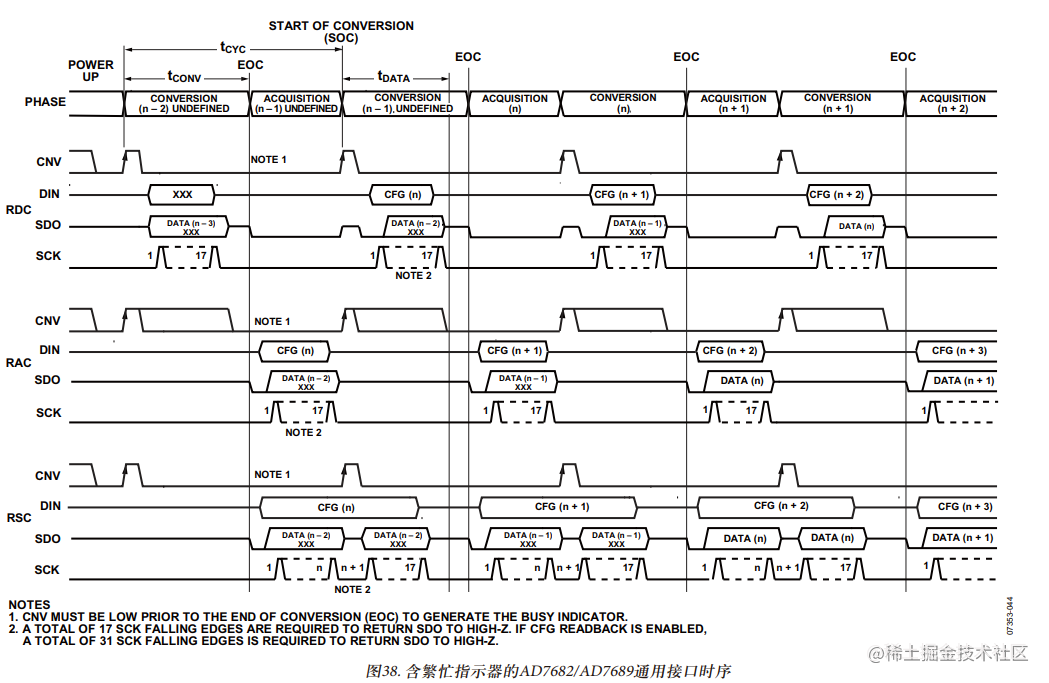

注:以上是无繁忙指示器的时序讲解,但是含有繁忙指示器的其实与其一样,只是每个模式的SCK多了一个时钟(本来16个SCK,但是繁忙指示器是有17个SCK的),如下含繁忙指示器的时序图。

- 含繁忙指示器的时序图: