内存(DRAM)作为当代数字系统最主要的核心部件之一,从各种终端设备到核心层数据处理和存储设备,从各种消费类电子设备到社会各行业专用设备,是各种级别的CPU进行数据处理运算和缓存的不可或缺的周转“仓库”,一个强大的核心处理单元也必须配备一个高速运转的宽通路的数据访问和存储单元。近20多年来,DRAM也快速地从20世纪末期的SDRAM发展到21世纪DDRRAM。在21世纪的前10年,DDR标准主要是个人信息处理终端的代表设备—-PC和个人工作站类驱动,快速从DDR1演进到DDR3。而近10年来,进入移动互联时代后海量数据爆发,AI和深度学习以及5G驱动,在个人信息终端上基本可以胜任的DDR4标准,明显显得力不从心。今天DDR5正在昂首阔步地配合以PCIE5.032Gbps为代表的第5代高速I/O数据传输走向最终的市场化。

一

. DDR

标准发展和

DDR5

简介

下图展示的是RAM(RandomAccess Memory)20多年来的发展和信号特点以及设计演进。

图1 DDR标准发展和信号特点演进

作为当前市场主流的DDR4标准和业界正在集中攻关的DDR5标准,对比有何差异呢?

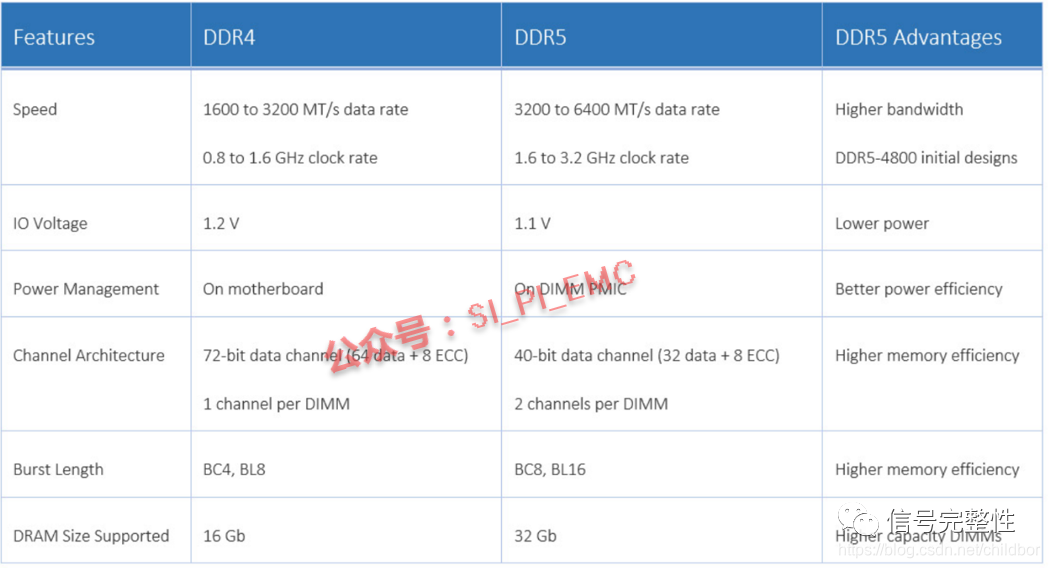

如下表所列,从芯片开发到电路系统设计角度来看相比,DDR5为了实现更高带宽和吞吐量进一步提升读写速率和改变通道架构以及猝发读写长度,目前规划的最高速率达8400MT/s。为了实现更低功耗和电源管理I/O电压降到1.1V,并在DIMM条上完成电源管理工作以实现更高的电源效率(主要是缩短电源传输路径以降低损耗和减小潜在的干扰)。为了提高数据带宽,不仅提升速率同时采用双通道架构,提升读写效率,采用双通道32data + 8 ECC,BurstLength也从4/8提高到8/16,最后还支持更高容量的DRAM器件,从DDR416 Gb加倍到32 Gb。总之,DDR5作为业界备受期望的第5代I/O的内部数据共享和传输标准将与PCIExpress 5.0乃至6.0等高速接口标准一起重塑iABC时代的大数据流的高速公路。

表1 DDR4和DDR5比较(源自Rambus)

图2 DDR5 总线架构和标准标准DDR5 内存条

从物理层信号角度来看,DDR5主要有如下特点:

1.采用分离式全速率时钟,对应6400M T/s频率最高达3.2GHz。

图3 DDR5 DQS控制DQ读写时序

时钟控制命令信号,选通信号控制数据,如上图示。对时钟信号抖动的要求更加严格,对各种命令信号与数据和地址信号的时序要求也更高。

2.更宽的总线,单端信号,从RCD(Registering ClockDrivers)芯片来看采用Multi-Drop架构。

基于今天更宽的总线需求,在一块刀片服务器上可能支持1000+个并行数据通道。且由于继续采用单端信号且速率倍增,传统只在串行差分电路上考虑的损耗问题也开始困扰DDR5.因此在DDR5设计和验证测试上,不仅需要考虑传统的串扰问题还增加了对电路损耗问题的考虑。

3.双向复用的数据总线,读写数据分时复用链路。

由于有限的链路通道和布板空间等资源读写操作继续采用共享总线,因此需要分时操作。从验证测试角度来看也需要分别对读和写信号进行分离以检查其是否满足规范。

图4 DDR5读写共享总线

4.猝发DQS和DQ信号在更高速率的背景下在有限带宽的链路传输时带来更多ISI效应问题。

在DQS读写前导位,猝发第一个bit等等均有不同的效应和表现。此外考虑到存储电路在设计上不同于串行电路存在较多的阻抗不匹配,因此反射问题或干扰带来的ISI也会更严重。

图5 DDR5在接收端采用更多的类似高速串行总线的信号处理

因此在接收侧速率大于3600MT/s时采用类似高速串行电路和标准总线中已经成熟的DFE均衡技术,可变增益放大(VGA)则通过MR寄存器配置,以补偿在更高速率传输时链路上的损耗。DDR4标准采用的CTLE作为常用的线性均衡放大,虽然简单易实现但是其放大噪声的副产品也更为常见,考虑到DDR5总线里的反射噪声比没有采用。另外考虑到并行总线的串扰和反射等各信号抖动的定义和分析也会随之变化。

从测试角度来看,示波器是无法得到TP2点即均衡后的信号的,而仅能得到TP1点的信号,然后通过集成在示波器上的分析软件里的均衡算法对信号进行均衡处理以得到张开的眼图。眼图分析的参考时钟则来自基于时钟信号的DQS信号。另外眼图测试也从以往仅对DQ进行扩展到包括CMD/ADDR总线。

以上我们介绍了DDR5的一些新的变化和挑战。下面介绍一下DDR5的验证和测试的一些问题和解决方案。

当前DDR5规范尚未完全制定完毕,DDR5颗粒以及辅助DB和RCD芯片目前主要还在DIMM应用阶段,未进入嵌入式系统阶段。典型的DDR5生态系统,涉及DDR5总线的主要包括DIMM产品和系统集成产品。当前主要有三种DIMM产品:UDIMM(UnbufferedDIMM),RDIMM(Registered DIMM),LRDIMM(Load-Reduced DIMM). DDR5生态系统如下图示:

图6 DDR5生态系统

典型地在DIMM上,与DDR5总线相关除了核心的颗粒DRAM之外,还有DB(LRDIMM上用buffer芯片),RCD等芯片。从上图可以看到针对不同功能的芯片部件到DIMM直到系统级产品集成,分别有不同的测试需求。比如针对DRAM颗粒以及DB和RCD等,需要进行TX,RX及Protocol测试,而对整个DIMM产品而言则要进行RX测试和协议测试。

对DDR5有一些研究的工程师应该都知道,不管是Tx端还是在Rx端的测试,DDR5与前几代总线将会有非常大的区别,比如在探测上无法探测到最终端,这样就会导致信号发生发射,也无法测试到均衡之后的结果。

图7DDR5 BGA Probe和板上安装示意图

即使如上图所示的BGA Probe夹具已经提供了最接近真实信号测试点的位置,然而依然存在误差。因此如果有BGAProbe的模型或S参数,还可以用示波器上的去嵌功能进行De-Embed操作。如下图示:

图8 InfiniiSim用于DDR BGA Probe去嵌示意图

还有很多测试相关的问题,比如Rx测试、DIMM槽的测试夹具、协议测试等等。