74HC595是8位串行移位寄存器,其中带有移位寄存器和存储寄存器,这两个寄存器分别采用不同的时钟控制。串行数据输入到内部8位移位寄存器然后再并行输出。

01

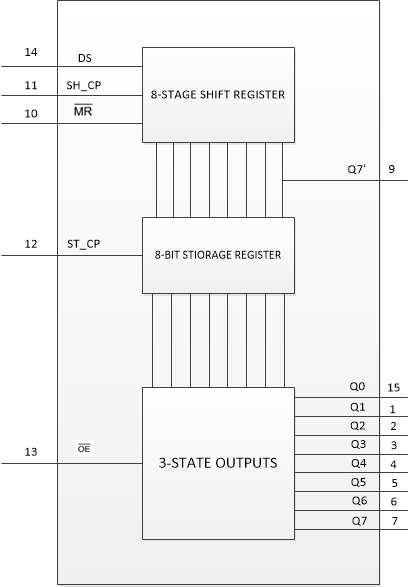

74HC595内部结构

如图所示为74HC595的内部结构图,首先14引脚DS为串行移位数据线,串行数据由DS处输入。11号引脚SH_CP为移位寄存器的时钟输入。12号引脚ST_CP为存储寄存器的时钟输出。Q7’为级联输出端,Q0-Q7为8位数据输出。

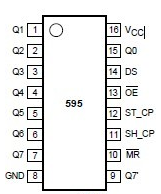

接下来对74HC595的各引脚功能进行描述。

Q0~Q7:8位数据输出。

OE:使能端,高电平时禁止输出,此处直接接地。

MR:数据清零端,低电平时将移位寄存器清零,此处直接接高。

Q7’:级联输出端,级联时接下一个595的DS端。

DS:串行数据输入端。

ST_CP:存储寄存器的时钟输入。上升沿时移位寄存器中的数据进入存储寄存