一、

AHB

总线介绍

AHB总线用于性能要求较高的系统互连,比如内部memory、高带宽的外设、GMAC、eMMC/SD等,其仍然为分时独占式总线,也就是说一个时间点总线只会完成一个传输事件。下图是一个典型的AHB总线互连例子,图中Manager为总线的Master设备,Subordinate为总线的Slave设备。AHB总线互连逻辑包括一个地址译码器和一个多路选择器。地址译码器用于将Master发送的地址转换成合适的sel选择信号;多路选择器将各个Slave的输出数据合理的选择给Master。图中只画出了一个Master设备,实际上AHB总线支持多个Master对多个Slave结构。

目前最新AHB总线版本为AHB5和AHB-Lite,对于只有一个Master的总线,结构可以简化很多,因此可单独使用AHB-Lite协议。

二、AHB

总线信号

按照上述概念可将AHB总线信号分类,如下表所示:

|

|

|

|

|

|

|

|||

|

HCLK |

时钟→总线 |

1 |

时钟,上升沿数据有效。 |

|

HRESETn |

复位→总线 |

1 |

复位,低有效,该信号可直接和系统总线复位连接。 |

|

|

|||

|

HADDR |

Master→总线 |

max=64 |

AHB总线地址,最大64bits。 |

|

HBURST |

Master→总线 |

max=3 |

用于规定Burst传输次数和地址递增方式。 |

|

HMASTLOCK |

Master→总线 |

1 |

锁定Master传输,锁定期间传输无法被打断。 |

|

HPROT |

Master→总线 |

0/4/7 |

保护控制信号,用于指示本次传输类型。 |

|

HSIZE |

Master→总线 |

3 |

用于指示每次传输的数据大小。 |

|

HNONSEC |

Master→总线 |

1 |

指示当前传输是否安全。 |

|

HEXCL |

Master→总线 |

1 |

用于指示该传输是否为独占传输(Exclusive Access)。 |

|

HMASTER |

Master→总线 |

max=8 |

用于指示当前是哪个Master发起了传输,每个Master有一个唯一的HMASTER ID。 |

|

HTRANS |

Master→总线 |

2 |

|

|

HWDATA |

Master→总线 |

max=1024 |

写数据,最大位宽支持1024bits,建议在32bits – 256bits之间。 |

|

HWSTRB |

Master→总线 |

max=128 |

写数据字节使能,位宽为HWDATA的位宽除以8。 |

|

HWRITE |

Master→总线 |

1 |

读写指示信号,“1”为写,“0”为读。 |

|

|

|||

|

HRDATA |

Slave→总线 |

max=1024 |

读数据,最大位宽支持1024bits,建议在32bits – 256bits之间。 |

|

HREADYOUT |

Slave→总线 |

1 |

Slave端设备准备就绪信号,用法和APB的PREADY类似。 |

|

HRESP |

Slave→总线 |

1 |

Slave端设备的应答信号,表明当前传输是否成功,“1”错误。 |

|

HEXOKAY |

Slave→总线 |

1 |

表示独占传输(Exclusive Transfer)是否成功。 |

|

|

|||

|

HSELx |

总线→Slave |

1 |

Slave设备选择信号,用法和APB的PSEL类似。当Slave被选中且为非IDLE传输时,HSELx必须和地址、控制信号同一拍有效。 |

|

|

|||

|

HREADY |

总线→Slave 总线→Master |

1 |

该信号由总线内部产生,用于通知Master和Slave上次传输已经结束,总线已经准备就绪开始下一次传输。 |

- HTRANS[1:0]

|

HTRANS[1:0] |

类型 |

说明 |

| 00 | IDLE | IDLE表示没有数据传输,Master使用IDLE来表示非数据传输,一般用IDLE传输终止一次locked传输。Slave必须立即响应Master发送的IDLE传输,并将OKAY应答送到HRESP上,传输内容Slave必须忽略。 |

| 01 | BUSY | BUSY传输允许在Burst传输的中间插入空闲周期,以表示Master会继续burst但下一次传输不能立即发送。当Master使用BUSY传输时,下一次传输的地址和控制信号必须准备好。只有未定义长度的Burst可以在Burst结束的时候插入BUSY传输标志。Slave必须立即响应BUSY传输,并将传输内容忽略。 |

| 10 | NONSEQ | NONSEQ用于指示一次Single传输,或一次burst传输的开始。地址和控制信号和前一次传输不同,会产生变化。 |

| 11 | SEQ | Burst传输的剩余部分被标记为SEQ,表示连续传输,地址和控制信号和前一次保持一致。 |

- HSIZE[2:0]

|

HSIZE[2:0] |

类型 |

说明 |

| 000 | Byte | 8bits,传输一个字节。 |

| 001 | Halfword | 16bits,传输一个半字。 |

| 010 | Word | 32bits,传输一个字。 |

| 011 | DoubleWord | 64bits,传输两个字。 |

| 100 | 4 Words | 128bits,传输四个字。 |

| 101 | 8 Words | 256bits,传输八个字。 |

| 110 | 16 Words | 512bits,传输十六个字。 |

| 111 | 32 Words | 1024bits,传输三十二个字。 |

HSIZE用于表示单次数据传输的大小,其数值小于等于数据宽度,比如数据宽度是32bits,那么HSIZE只能是000/001/010三个数值。在Burst传输过程中,该数值必须保持不变。

- HBURST[2:0]

|

HBURST[2:0] |

类型 |

说明 |

| 000 | SINGLE | 单次传输 |

| 001 | INCR | 未定义长度的增量Burst传输 |

| 010 | WRAP4 | 4拍回环Burst传输 |

| 011 | INCR4 | 4拍增量Burst传输 |

| 100 | WRAP8 | 8拍回环Burst传输 |

| 101 | INCR8 | 8拍增量Burst传输 |

| 110 | WRAP16 | 16拍回环Burst传输 |

| 111 | INCR16 | 16拍增量Burst传输 |

由表中可以看出,传输可分成SINGLE、INCR和WRAP类型,每种又按照每次Burst节拍数分成不同情况。一拍为Burst传输的最小传输单位,具体理解在后续介绍。INCR burst的每次传输的地址是连续的,且每次传输的地址数值相较于上一次是递增的。WRAP burst在地址增加到地址边界时,地址会返回到最开始地址。地址边界根据拍数和传输大小计算,HBURST和HSIZE确定总传输数据量大小。例如,一个WRAP4传输4bytes数据,如果开始地址为0x34,那么4拍的数据地址为0x34、0x38、0x3C和0x30。

单次传输可以使用SINGLE标识,或使用未定义大小的INCR标识,一般使用SINGLE标识。

- HPROT[3:0](AHB5以下版本,用于数据保护)

|

HPORT[3:0] |

说明 |

| [0] |

0: Opcode fetch 1: Data access |

| [1] |

0: User access 1: Privileged access |

| [2] |

0: Non-bufferable 1: Bufferable |

| [3] |

0: Non-cacheable 1: Cacheable |

- HPROT[6:0]( AHB5扩展内容,用于Memory,bit3不同于AHB5以下版本)

|

HPORT[6:0] |

名称 |

说明 |

| [0] | Data/Inst |

0: Opcode fetch 1: Data access |

| [1] | Privileged |

0: unprivileged access 1: Privileged access |

| [2] | Bufferable |

如果[4:3]均无效的话,那么该bit位生效 0: Non-bufferable,写响应必须由最终的目的地址提供,而不是中间的buffer。 1: Bufferable,写响应可由中间经过的节点提供,但需要及时传递写传输到目的端。 |

| [3] | Modifiable |

0: 传输的数据不可纠正修改; 1: 传输的数据等可纠正修改; |

| [4] | Lookup |

0: 传输不需要查找cache,且必须传递到目的端; 1: 传输必须查找cache; |

| [5] | Allocate |

0: 传输不会分配到cache; 1: 传输分配到cache; |

| [6] | Shareable |

0: 传输不可共享,访问的memory区域不能被其他Master访问,访问的应答不会确保被其他Master可见。Device类型的memory,该bit为0; 1: 传输可共享,访问的memory区域可以被其他Master访问。 |

对于Memory类型,可通过HPROT[6:2]判断memory类型,具体如下表所示:

|

HPROT[6] |

HPROT[5] |

HPROT[4] |

HPROT[3] |

HPROT[2] |

Memory 类型 |

| 0 | 0 | 0 | 0 | 0 | Device-nE |

| 0 | 0 | 0 | 0 | 1 | Device-E |

| 0 | 0 | 0 | 1 | 0 | Normal Non-cacheable,non-shareable |

| 0 | 0/1 | 1 | 1 | 0 | Write-through, Non-shareable |

| 0 | 0/1 | 1 | 1 | 1 | Write-back, Non-shareable |

| 1 | 0 | 0 | 1 | 0 | Normal Non-cacheable, Sahreable |

| 1 | 0/1 | 1 | 1 | 0 | Write-through, Shareable |

| 1 | 0/1 | 1 | 1 | 1 | Write-back, Shareable |

- 用户信号

|

信号 |

方向 |

说明 |

| HAUSER | Master→总线 | 用户自定义,推荐宽度0-128bits |

| HWUSER | Master→总线 | 用户自定义,推荐宽度0-DATA_WIDTH/2 |

| HRUSER | Slave→总线 | 用户自定义,推荐宽度0-DATA_WIDTH/2 |

| HBUSER | Slave→总线 | 用户自定义,推荐宽度0-16bits |

该组信号为用户自定义信号,具体传输内容和含义需要用户自己决定,一般不建议使用该组信号。AHB协议不定义这些信号的功能,因此,在多个拥有用户自定义信号的系统中,可能会带来信号不兼容的问题。

三、AHB

总线传输

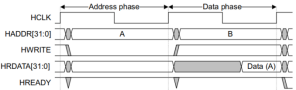

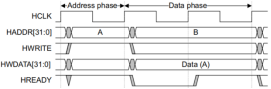

AHB传输分成两个阶段:地址阶段和数据阶段。地址阶段HWRITE、HADDR等控制信号同一拍有效,随后HREADY拉高表示当前地址已生效。数据阶段HWDATA、HRDATA等和数据相关的信号有效,表示数据读写的开始,数据阶段可能会跨多个HCLK时钟周期,根据传输数据量大小而定。

下图是AHB总线的单次读写传输,包括立即读写和等待读写传输,由于和APB总线类似,具体说明可参考APB总线。

注意地址阶段和数据阶段是可以pipeline的,如果有多次连续传输,但地址不同,可以采用如下图所示的时序完成。在A的数据阶段,可以启动下一次传输的B的地址阶段。

3.1 Burst传输

上图是Burst传输举例,各个时钟周期的动作如下:

T1时刻发起4拍读Burst传输,地址等控制信号送入总线;

-

T2时刻Master未能主板好第2拍burst,插入BUSY标志delay burst传输;

-

T3时刻Master发出第2拍burst,SEQ标志跟在BUSY后面,Slave忽略T3的数据;

-

T4时刻Master发出第3拍burst,过程和T3相同;

-

T5时刻Master发出最后一拍burst,过程和T3相同,Slave端HREADY拉低,T4时刻的读数据返回delay;

-

T6时刻Slave端的HREADY拉高有效,HRDATA返回T4时刻请求;

-

T7时刻Slave端的HREADY拉高有效,HRDATA返回T5时刻请求;

下图是WRAP4 Burst传输的一个例子,注意地址在0x3c后回环到0x30。

下图是INCR4 Burst传输的一个例子,地址一直增加到0x34。

下图是WRAP8 Burst传输的一个例子,注意在0x3C之后地址回环到0x20。

下图是INCR8 Burst传输,地址一直增加到0x42。

下图是INCR Burst传输,包含两次Burst传输,一次2拍,一次3拍。

3.2 Lock传输

Lock传输由Master通过HMASTLOCK信号发送给总线,用于表明当前的传输不可分割和打断,必须在此次传输完成后才能启动另一次传输。一个典型的Lock传输例子是用来维护处理器发出的SWP指令,保证读写操作之间有个完整的操作,如下图所示:

Lock传输完成后,建议Master发送一次IDLE传输,允许在Lock传输的开始、中间和结束时插入IDLE传输。目前大部分的Slave并不能处理HMASTER信号,如果Slave可以被多个Master访问,则必须要求Slave处理HMASTER信号。例如,一个多端口的memory控制器(MPMC),则必须正确识别Master发送来的HMASTER请求。

不推荐HMASTER和IDLE同时有效,但这样做也并不会产生错误。同样不推荐Master Lock一串IDLE传输,或在Lock传输结束后不插入IDLE,这会影响总线仲裁。

Lock传输中的每一拍,均要求保持相同的Slave地址,但AHB总线不会检查是否保持一致,需要添加额外的验证模块来确保上述要求。

3.3 Waited传输

Slave使用HREADYOUT信号插入wait状态,要求更多的准备时间来处理数据。在等待期间,Master必须严格控制传输状态的改变,包括传输类型和地址。

3.3.1

传输类型改变

当Slave在wait状态时,传输类型只有在以下几种情况下可以改变,其他情况必须保持不变,这几种情况为:IDLE、固定长度Burst时的BUSY、未定义长度Burst是的BUSY。

wait状态下的IDLE传输,Master允许IDLE传输到NONSEQ传输类型改变,当HTRANS改变成NONSEQ,Master必须保持NONSEQ不变,直到HREADY拉高。

上图是Master端的IDLE传输时序,各个时钟周期的动作如下:

-

T1时刻,Master发起SINGLE Burst,访问地址A;

-

T2时刻,Slave HREADY拉低表示尚未就绪,同时Master插入IDLE传输,地址为Y;

-

T3时刻,Master继续插入IDLE传输,地址为Z;

-

T4时刻,Master改变传输类型为NONSEQ,发起INCR4 burst传输,地址为B;

-

T5时刻,HREADY仍为低,Master保持HTRANS不变;

-

T6时刻,HREADY拉高,SINGLE Burst到地址A的传输结束,数据A返回Master,同时发送地址B的第一拍;

-

T7时刻,INCR4的第二拍发送,第一拍数据B返回。

wait状态下的固定长度Burst传输,Master允许由BUSY到SEQ传输类型改变,当HTRANS传输类型改变为SEQ时,Master必须保持HTRANS不变,直到HREADY拉高。

上图是Master端的BUSY到SEQ切换传输时序,各个时钟周期的动作如下:

-

T1时刻,Master发起下一拍INCR4 burst,访问地址0x24;

-

T2、T3时刻,Slave HREADY拉低表示尚未就绪,Master插入一次BUSY传输;

-

T4时刻,Master将传输类型切换为SEQ,并发起下一拍Burst,地址为0x28;

-

T5时刻,由于HREADY依旧拉低,Master必须保持SEQ传输不变;

-

T6时刻,HREADY拉高,0x24的请求数据返回;

-

T7时刻,Master发送下一拍Burst,同时0x28的请求数据返回。

wait状态下的未定义长度Burst传输,Master允许在HREADY为低时,由BUSY状态到任一状态改变。如果BUSY后面切换到SEQ,则表示Burst继续,如果后面切换到IDLE或NONSEQ,则表示Burst终止。

上图是Master端的BUSY到NONSEQ传输时序,各个时钟周期的动作如下:

- T1时刻,Master发起下一拍INCR burst,访问地址0x64;

- T2、T3时刻,Slave HREADY拉低表示尚未就绪,Master插入BUSY传输;

- T4时刻,Master将传输类型切换为NONSEQ,并发起一次新的INCR4 Burst,地址为0x10;

- T5时刻,由于HREADY依旧拉低,Master必须保持NONSEQ传输不变;

- T6时刻,HREADY拉高,0x64的请求数据返回,INCR传输结束;

- T7时刻,0x10请求数据返回,INCR4第二拍请求发送。

3.3.2 地址改变

当Slave在wait状态时,Master只能在下面两种情况下改变地址,其他情况必须保持不变,这两种情况为:IDLE传输、错误应答。IDLE传输可参考传输类型改变时的例子,地址从A到Y到Z改变,参

考下图

。这里重点说下错误应答后的地址变化,如果Slave产出的ERROR应答,那么Master允许改变地址。

上图是一个wait状态下的错误应答时序,各个时钟周期的动作如下:

-

T1时刻,Master发起下一拍INCR burst,访问地址0x24;

-

T2、T3时刻,Slave HREADY拉低表示尚未就绪,但HRESP应答为OKAY,Master发起下一拍INCR4 burst,访问地址为0x28;

-

T4时刻,Slave发送ERROR错误应答,表示0x24请求出现错误;

-

T5时刻,Master接收ERROR应答,并将INCR4终止,切换到IDLE传输,Slave HEADY拉高有效,HRESP应答ERROR,表示0x28请求出现错误;

-

T6时刻,Slave HRESP应答OKAY,表示IDLE传输OKAY。

四、EBT(Early Burst Termination)

Burst传输的中间可以插入BUSY传输,表示Master需要更多的时间准备下一次burst传输。对于INCR传输,Master可以在插入BUSY传输后,决定是否继续Burst传输,还是终止此次Burst传输。在这种情况下,可以接收Master发送一个NONSEQ或IDLE传输来有效的终止未定义长度的Burst传输。对于固定长度的Burst传输,不允许插入BUSY传输后立即终止Burst,必须是SEQ传输来终止Burst。

但是,在一些特殊情况下,Burst也会被终止,这些特殊情况为:Slave错误应答和多层AHB互连终止。这种非正常Burst终止,称为EBT。

4.1 Slave错误应答

如果Slave发出ERROR应答,那么Master可以取消剩下的burst传输。然而,协议未规定必须停止发送,Master也可以把剩下的数据发送完。如果Master取消了剩下的数据发送,那么Master必须在两个周期的ERROR应答中,将HTRANS改为IDLE状态。

如果Master没有完成剩下的数据发送,那么不要求Master下次访问Slave时必须重新发送之前的Burst数据。例如,如果Master只完成了8拍中的3拍数据,那么不需要下次访问同样slave时,再将之前的5拍数据重新发送。

4.2 多层AHB互连终止

Burst终止对于Master而言要求较为宽松,但是对于Slave而言,需要处理Burst终止带来的传输问题。当一个多层AHB互连的总线被用在拥有多个Master的系统中时,多层互连总线可以终止一次Burst,这样其他Master可以访问对应的Slave设备。Slave设备要求正确地处理上述情况。

五、AHB

总线仲裁策略

AHB主要有三种仲裁策略:固定优先级/轮询、时间片、权值令牌。仲裁主要发生在有多个Master同时抢占总线时,选择合适的仲裁策略,可以将总线性能调优,有利于SoC总体性能的提升。

参考

Synopsys的AHB文档,学习总线仲裁策略和方法。