ILA可以加在代码里使用,也可以加在网表里使用。在这里举例加在代码中使用,硬件平台:Xilinx AX7020

1.打开vivado,新建项目(选择对应的芯片型号)

2.添加源文件,编写RTL代码

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2019/03/29 14:03:40

// Design Name:

// Module Name: counter

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//

module counter(

input clk,

output [3:0]led

);

wire clk;

(* keep = "TURE" *)reg [3:0] cnt = 4'd0;

assign led = cnt;

always@(posedge clk)

begin

cnt <= cnt + 4'd1;

end

endmodule

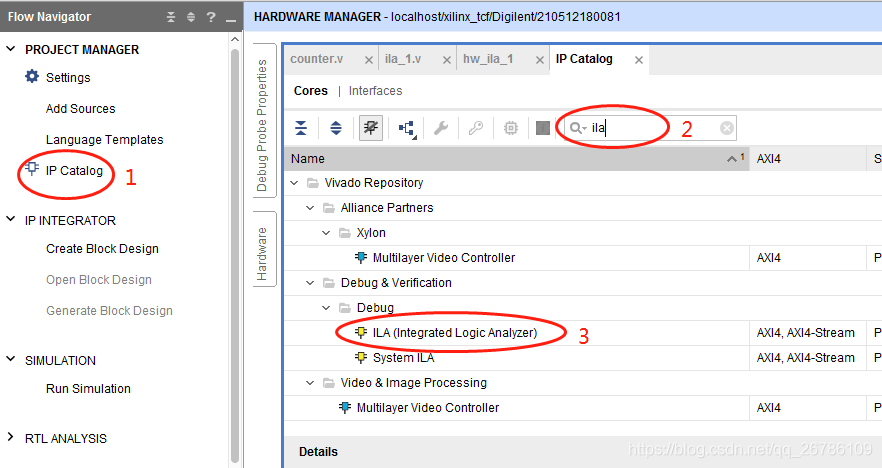

3.加入ILA核

在vivado工程中打开IP Catalog选项,找到ILA核

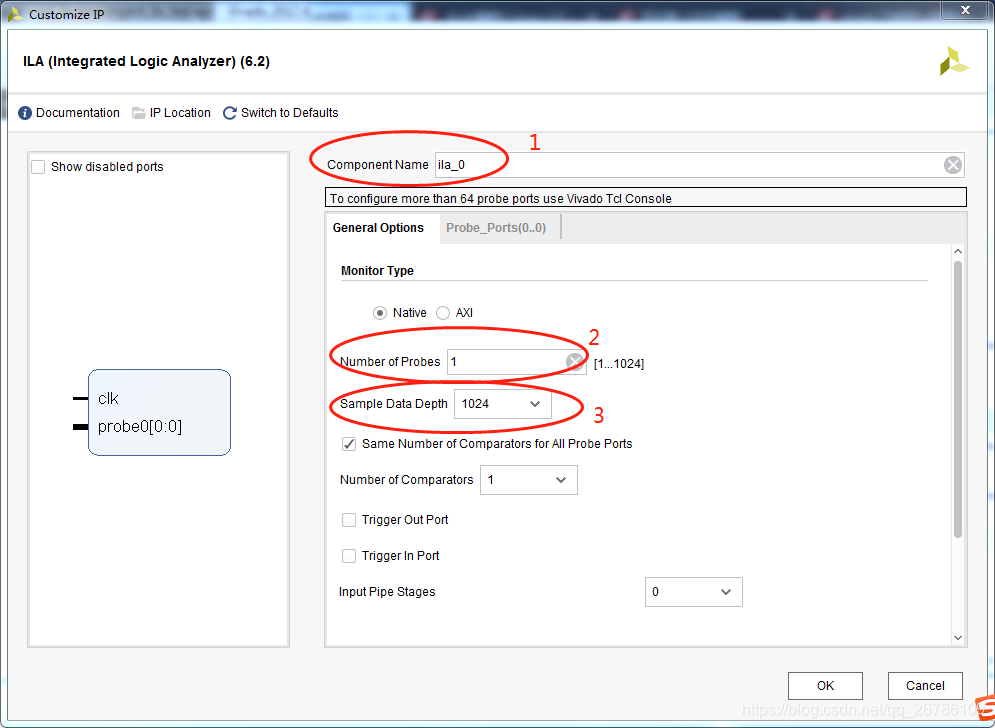

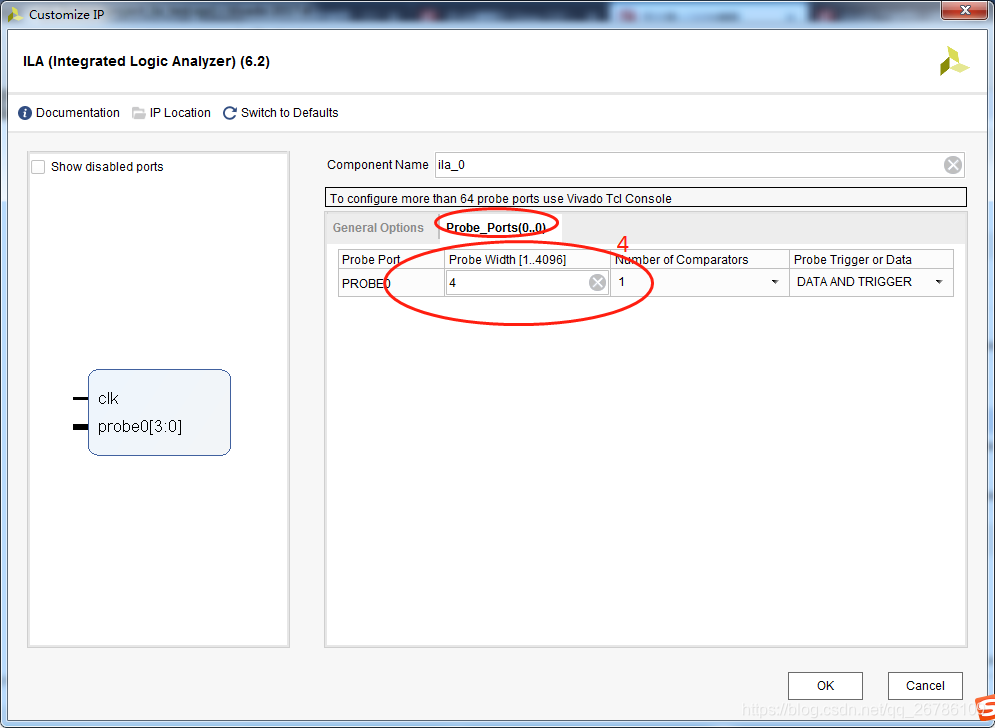

配置ila核,主要配置4个地方:1.组件的名字,2. 需要抓取的信号的个数,3. 抓取的信号的深度,4.所抓取的信号的宽度,此例子的cnt是4bit。OK!

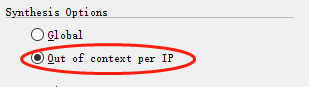

4.IP核配置完成,默认选择,Generate

5.在RTL源代码中添加例化ILA核,ILA核的clk信号需要连接到需要观察信号的相应时钟域,在一个RTL设计中是可以添加多个ILA核的,用于观察不同时钟域的信号。

`timescale 1ns / 1ps

module counter(

input clk,

output [3:0]q

);

wire clk;

(* keep = "TURE" *)reg [3:0] cnt = 4'd0; //在RTL中的信号前加上(*keep = "TRUE"*)即表示抓取该信号

assign q = cnt;

always@(posedge clk)

begin

cnt <= cnt + 4'd1;

end

ila_1 u_ila(

.clk(clk),

.probe0(cnt)

);

endmodule6.添加xdc约束文件,绑定引脚

set_property PACKAGE_PIN U18 [get_ports clk]

set_property IOSTANDARD LVCMOS33 [get_ports clk]

set_property IOSTANDARD LVCMOS33 [get_ports {led[3]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[2]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[1]}]

set_property IOSTANDARD LVCMOS33 [get_ports {led[0]}]

set_property PACKAGE_PIN J16 [get_ports {led[3]}]

set_property PACKAGE_PIN K16 [get_ports {led[2]}]

set_property PACKAGE_PIN M15 [get_ports {led[1]}]

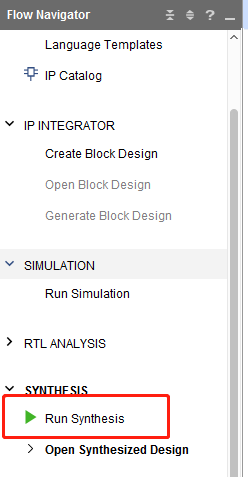

set_property PACKAGE_PIN M14 [get_ports {led[0]}]7.综合

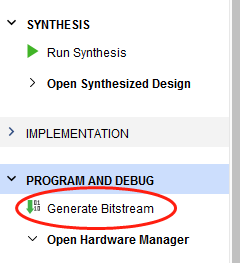

8.生成bit文件,生成后选择Open Hadrware Manager

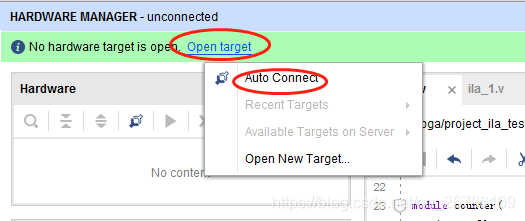

9.连接硬件

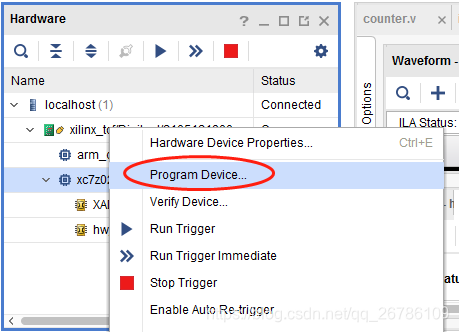

10.下载调试

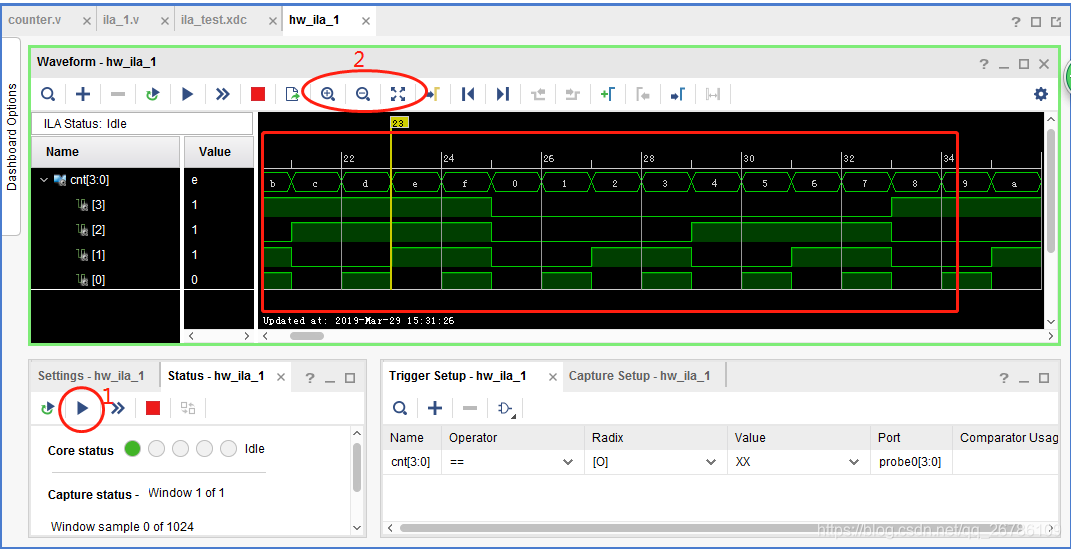

11.下载成功后会自动弹出ILA波形界面,选择RUN触发,通过放大缩小可以清晰看到波形时序。

12.完美结束!

版权声明:本文为qq_26786109原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接和本声明。