一、实验目的

熟悉并掌握Verilog HDL和Vivado的使用

二、实验环境

Vivado2021.2

三、实验目标

学习使用 Verilog 完成4选1多路选择器的设计和实现,并使用 Vivado工具对设计进行仿真和分析验证。

四、实验原理

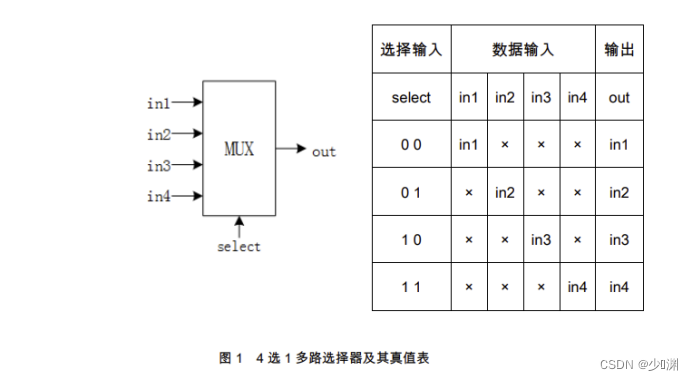

多路选择器(MUX)是一种在多路数据传送过程中,能够根据需要将其中任意一路选 出来的电路,其原理图和真值表如下图所示。

五、实验内容

5.1

vivado的下载和安装

为了完成4选1多路选择器,我们需要使用Verilog HDL 语言就是编写和仿真,而最知名的软件就是vivado。

为了安装vivado,首先需要登录它的官网:

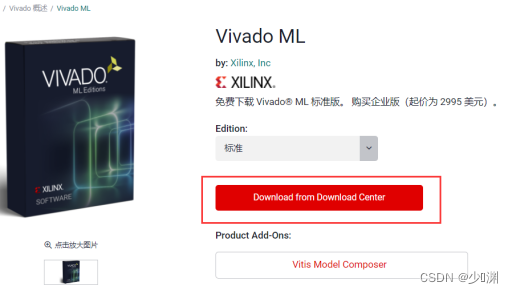

可以看到如下界面:

我们点击版本,显示如下:

点击标准版进行下载(周围的同学有选择下载企业版的,但是部分同学下载企业版后会因为缺少某些dll文件而打不开,所以建议下载标准版)

继续点击中间的download:

这里需要注意,我下载的时候是2022年五月,所以我比较不信任2022年1月的版本,所以我选择了2021年的2月版本。点击之后如下:

可以发现有三个选项可以下载,他们的区别是:第一个是windows的web版本,第二个是linux的web版本,第三个是Windows的直接下载版本。Web版本的好处是,可以仅仅下载很少的内容,然后只需要在有网的情况下,等待其安装完即可;直接下载的好处是下载完解压之后不需要网络。

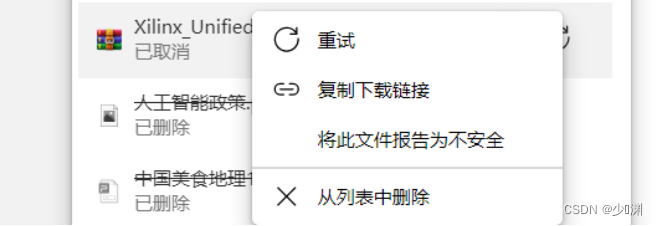

我选择的是直接下载,但是下载的实在太慢了。这里提供两种方法解决:

第一种方法是,在点击下载后,浏览器右边会出现下载的图标,如下:

右键选中:

复制下载链接,然后打开迅雷:

将复制的链接添加进去,就可以以相对快的速度下载了。

第二种方法是通过VPN进行下载,因为官网在国外,使用国内的网下载较慢,通过VPN可能稍微快点

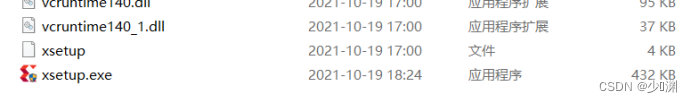

下载完成后,得到一个文件夹:

![]()

点进去,往下翻,找到

找到这个exe文件后,以管理员身份运行,就可以开始安装了。

首先进入到欢迎界面,下一步后,界面如下:

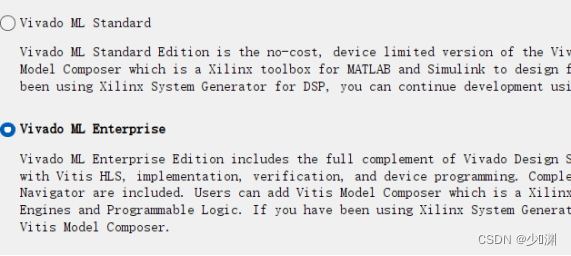

这里选择第一个标准版。下一步:

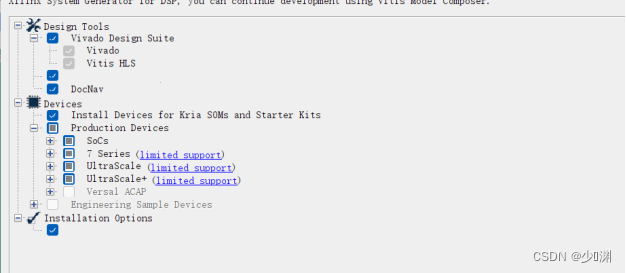

2021.2版本默认选中了上面这些,占用82.47G的硬盘空间,如果硬盘空间够的话,建议是全选的,如果不够的话,可能可以去掉SoCs。然后继续下一步:

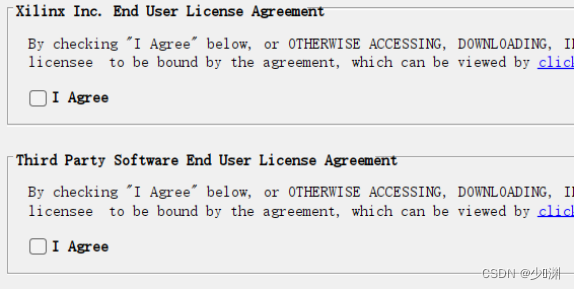

都选择同意,下一步:

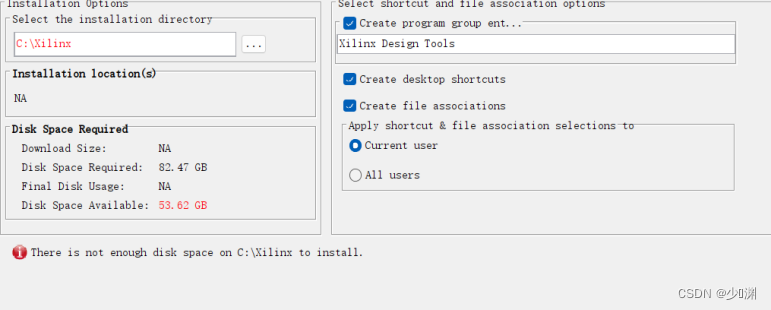

这个需要选择路径了,一般肯定是不会放在C盘的。这时候需要在D或者E盘新建一个Xilinx文件夹,并将路径修改到那个文件夹。需要注意的是,

路径一定不可以有中文!!

选择后,点击下一步,就等待安装即可:

5.

2

vivado的项目创建

安装完毕后,桌面会多出几个小图标:

点击选中的那一个,进入如下界面:

下面介绍如何创建一个进行多路选择的项目,点击Create Project:

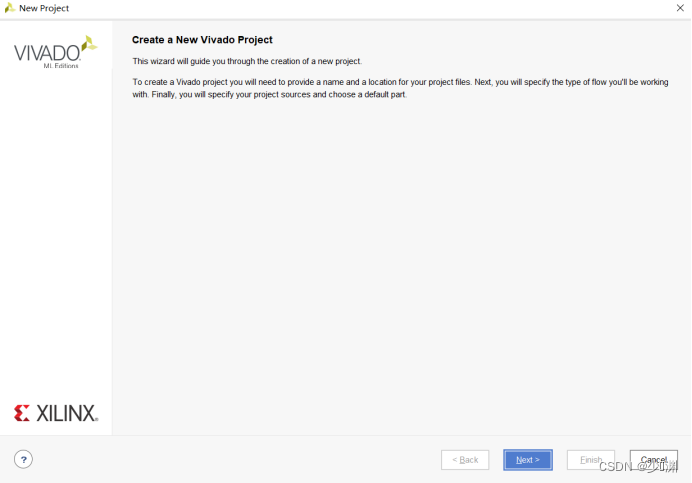

点击next:

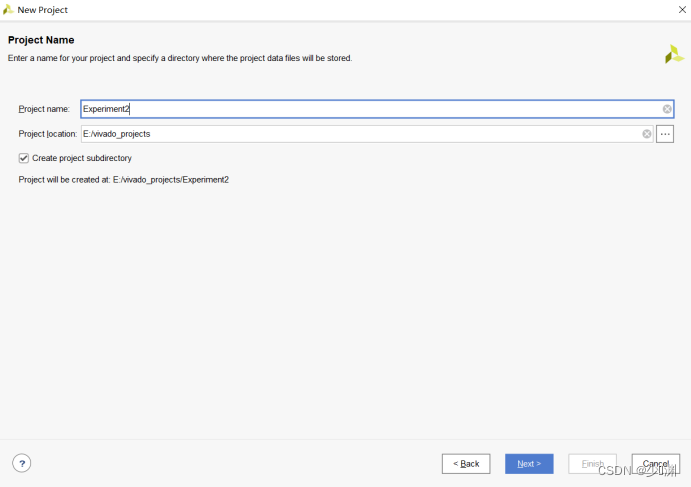

写上项目名和路径,依然不要有中文:

默认,然后next:

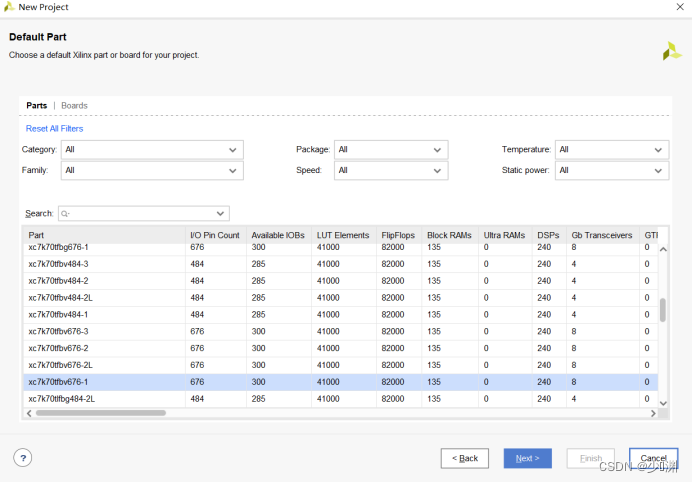

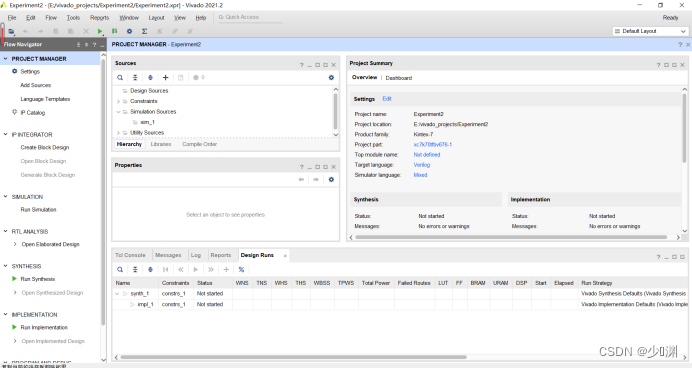

选择硬件数据:选择器件或者板卡,Parts表示器件,当然如果是板卡就点击Boards,我们实验一般都是使用parts,然后在底下的part中选取一个合适的即可(不会选默认也行)这样完成创建之后,界面如下:

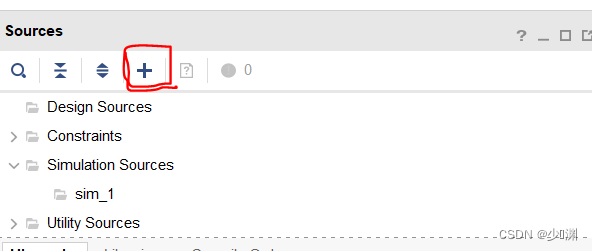

点击这个加号:

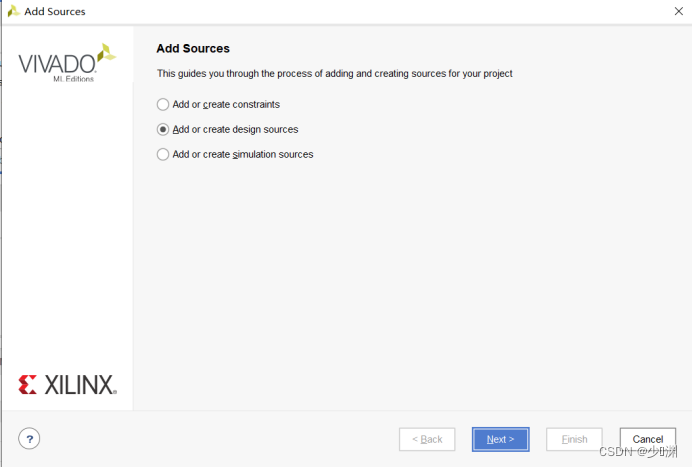

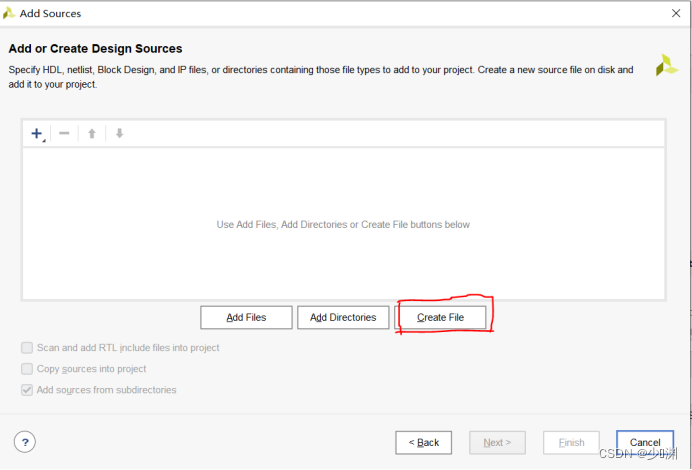

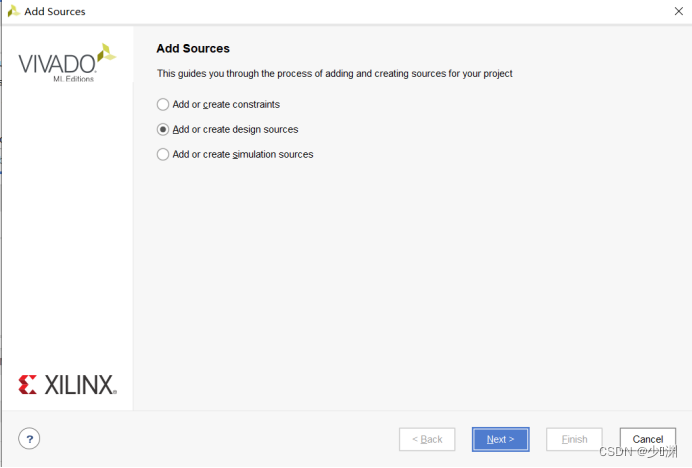

选择第二个,next:

选择CREATE files:

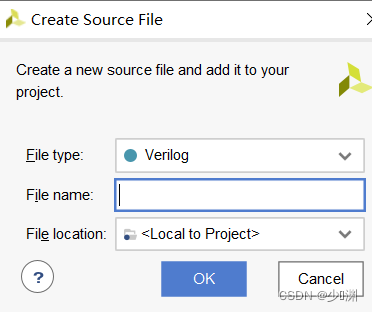

选择Verilog语言,定义一个文件名,然后确定。

选择port,因为我们实现的是4选1,需要5个input和1个output,所以我们直接点击加号添加到满足条件为止,然后OK。这样就完成了源文件的创建。

5.

3

Verilog语言编写4选1 选择器

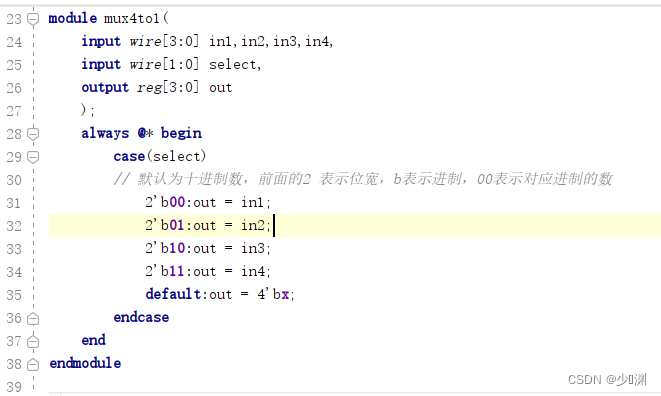

在进入到design source文件后,就可以进行Verilog的编写了。我编写的代码如下:

下面我来解释一个它们的含义:

Module是Verilog语言的一个基本单位,它是一个电路,通过输入和输出端口与其外部交互,以module+模块名开头,以endmodule结束。

在其中括号里定义了所需要的输入输出端口。

Input和output分别代表了我们所需要的五个输入端口和一个输出端口。

Wire和Reg是Verilog最常用的两个数据类型,wire 类型表示硬件单元之间的物理连线,由其连接的器件输出端连续驱动;寄存器(reg)用来表示存储单元,它会保持数据原有的值,直到被改写。它们的位宽默认为1,当位宽大于1时,就像上图表示的那样,以向量的形式写出。Wire[3:0]就表示位宽为4,最高有效位为0,最低有效位为3。

之后的always属于一种过程结构,Verilog的过程结构有always和initial。initial 语句从 0 时刻开始执行,只执行一次,多个 initial 块之间是相互独立的;与initial 语句相反,always 语句是重复执行的。always 语句块从 0 时刻开始执行其中的行为语句;当执行完最后一条语句后,便再次执行语句块中的第一条语句,如此循环反复。

之后的case相当于多个if-else语句,在select不同的时候,将输出结果赋值为对应的输入。

编写完设计代码后,我们再新建一个仿真案例测试:

点击这个加号:

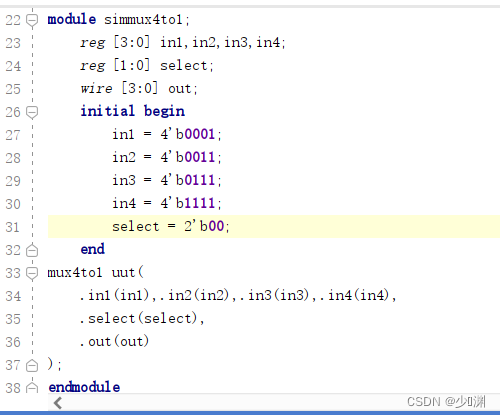

这次选择第三个,创建一个simulation sources,之后的过程与前面一样,不再赘述。创建后,编写代码如下:

现在是另一个模块了,所以模块依然以module+模块名开头,以endmodule结尾。因为与前一个模块相对,所以他们的输入输出要保持一致。并且该模块作为测试模块,需要对输入输出端口进行初始化,所以使用initial语句进行。初始化之后,我将select赋值为00,很明显输出应该为in1,现在需要验证是否正确。

为了将该模块和之前编写的设计模块联系起来,需要通过模块例化来完成。我采用命名端口进行连接,将需要例化的模块端口与外部信号按照其名字进行连接,端口顺序随意,可以与引用 module 的声明端口顺序不一致,只要保证端口名字与外部信号匹配即可。完成连接后,就可以开始测试了。

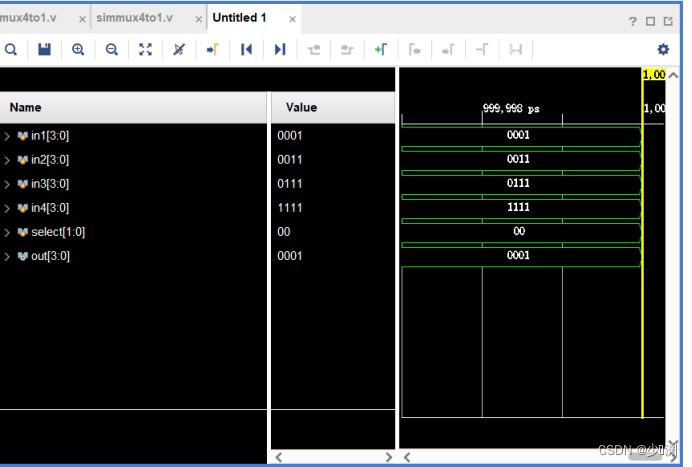

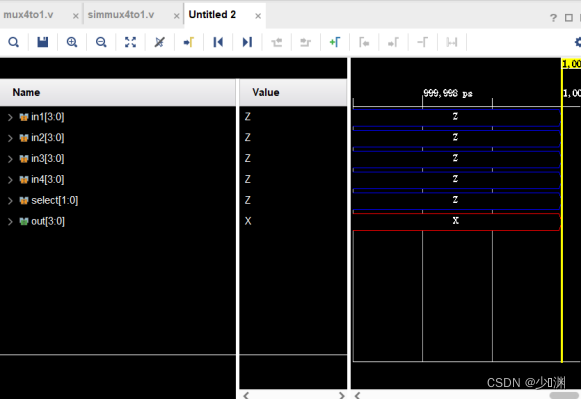

点击页面左侧的Run Simulation,得到如下结果:

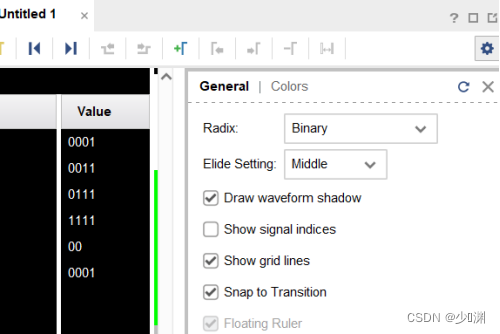

因为仿真显示默认为十六进制,所以为了显示二进制方便观察,可以点击右上角的齿轮,将Radix改成binary即可。

之后也可以

通过修改select的值来重复确认设计是否正确

,这里不再赘述。也可以通过点击:

Open Elaborated Design来查看设计的电路图(可能比较需要内存,我内存不够,运行会闪退)

5.

4

实验过程中遇到的问题和解决方案

5.4.1 安装问题

问题1

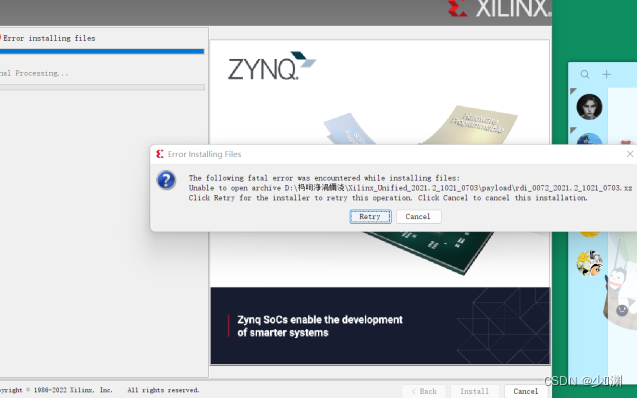

:在安装中如果出现:

这种情况,但是在之前选择存取路径时明明没有中文。

解决方案

:出现这种情况的原因是,可能是当解压安装包之后,解压后的文件夹存放的路径有中文。可以选择将路径中的中文更改为英文的方式解决。

问题2(同学的问题)

:

显示缺失dll文件,这种情况可能是装了专业版或者电脑本身缺少文件。

解决方案

:如果是装了专业版,建议重新安装;如果是缺少了文件,可以向正常安装的同学要对应的文件,存放在指定的路径即可。

问题3(同学的问题)

:

打开vivado显示win11上无法使用的问题。

解决方案

:经测试,关闭此警告后,仍可以正常运行vivado,应该不需要解决。

5.4.2 使用问题

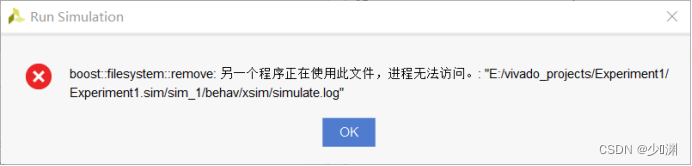

问题1

:在进行仿真时,显示一个程序正在使用。

解决方案

:这种情况在百度之后,我发现有两种可能,一种是使用了其他代码编辑器打开了该文件;另一种情况就是上一次仿真没有关闭。极大可能是第二种。最简单的解决方法是关闭所以与vivado有关的进程,并重新打开,省时省力。

另外,仿真案例正确的关闭方式是:

点击最右边那个×,而不仅仅是将那个仿真窗口关闭。

问题2

:

所有运行结果总是呈现高阻状态。

解决方案

:这种情况可能是因为两个模块没有连接好,具体可能是因为两个模块的端口格式不匹配等问题,检查并保持一致即可。

——————————————————-分割线—————————————————————

今天到这里结束,以后会更新全加器、比较器、译码器等计算机组成原理实验内容