目录

6、读写控制——ALE(Address Latch Enable)地址锁存允许:

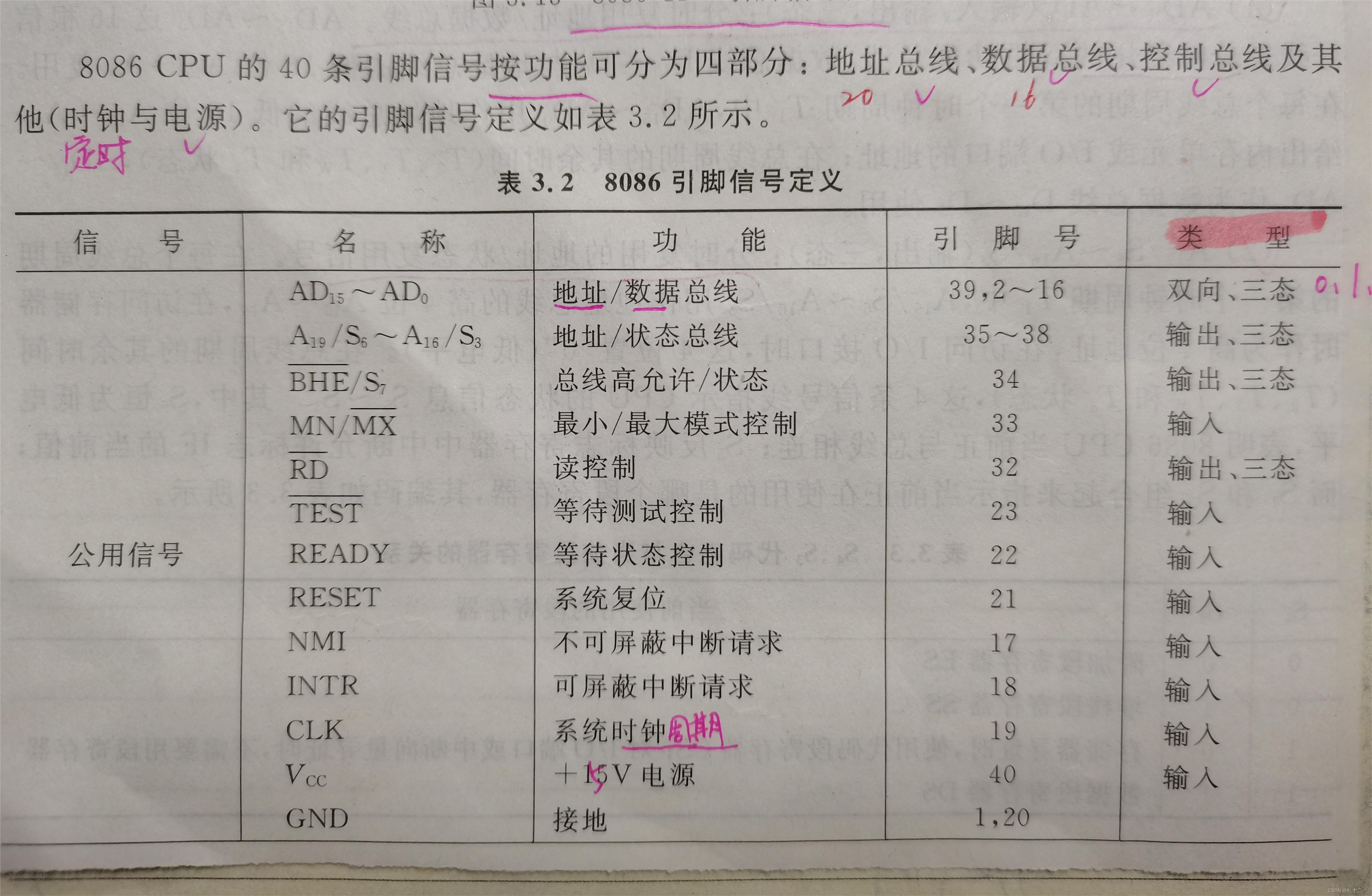

三、8088/8086CPU 引脚

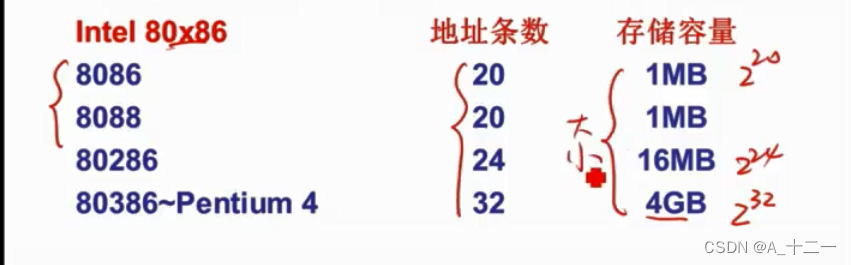

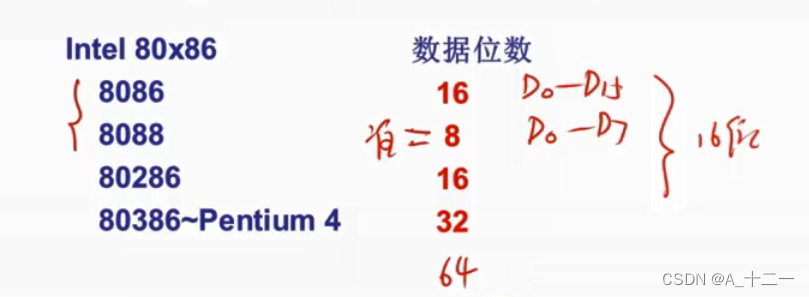

- 8088为准16位CPU(数据线为8位);8086为真正的16位微处理器(数据线为16位)

1、小知识点:

分时复用:一个引脚在不同的时刻具有两个甚至多个作用;公交车上下车

总线复用的目的是为了减少对外引脚个数

三态:高电平、低电平、高阻态

2、40个引脚(总线)信号

- 地址和数据复用,地址和状态复用

- 读写控制

- 中断请求和响应

- 总线请求和响应

- 其他

-

8088和8086的区别

3、地址、数据复用

- AD0~AD7:8位地址、数据分时复用,双向、三态

-

-

存储器读总线周期:

-

- 处于中间:悬浮态 = 高阻态

-

4、地址、状态复用

- A19/S6~A16/S3

- 地址、状态分时复用引脚,输出、三态

-

访问

存储器

的T1输出高四位地址A19~A16,证明:CPU访问内存时:20位AB; -

访问

外设

的T1全部输出低于低电平无效,证明:CPU访问外设接口时16位AB

5、地址线、数据线小总结:

6、读写控制——ALE(Address Latch Enable)地址锁存允许:

- 输出、三态、高电平有效

- 在由高电平变为低电平时,将20位地址缩入“地址锁存器”;

- 只在T1时工作

7、IO/M* 外设/存储器访问

- 输出,三态

- IO读总线周期:高电平有效

- 内存读总线周期:低电平有效

8、WR* 写控制

- 输出,三态,低电平有效

-

低电平时,CPU正在

写出

数据传送给主存或I/O端口

9、RD* 读控制

- 输出,三态,低电平有效

-

低电平时,CPU正在从存储器或I/O端口

读入

数据

10、IO/M*、WR*、RD*组合

这些组合起来:

- 控制4种基本的总线周期;

- 决定了系统中数据传输的方式

|

总线周期 |

IO/M* | WR* | RD* |

| 存储器读 | 0 | 1 | 0 |

| 存储器写 | 0 | 0 | 1 |

| I/O读 | 1 | 1 | 0 |

| I/O写 | 1 | 0 | 1 |

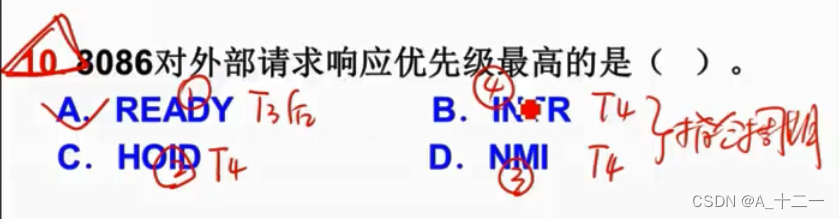

11、Ready 就绪

- 输入、高电平有效

-

CPU在总线周期的T3中,测试:

- ready = 1,继续下一步

- ready = 0,CPU插入“等待周期”,Tw一定插在“T3——T4”之间

12、DEN* 数据允许

- 输出、三态、低电平有效

- 低电平时,表示当前DB上正在传送数据,允许收发器收发数据

13、DT/R* 数据发送/接收信号

- 输出,三态

-

表明当前总线上数据的流向

- 高电平时,数据自CPU输出——发送

- 低电平时,数据输入CPU——接收

-

在8086最小工作模式下,决定CPU最终接受或发送数据的引脚

14、中断请求和响应——INTR 可屏蔽中断请求

- 输入,高电平有效

- 高电平时,表示请求设备向CPU申请可屏蔽中断

- 中断的功能:主机与外设进行数据交换

- 是否响应受控于IF:IF = 1 开中断

- 可以被屏蔽

15、INTA* 可屏蔽中断响应

- 输出,低电平有效

- 低电平时,表示来自INTR引脚的中断请求已经被CPU响应,CPU进入中断响应周期

16、NMI 不可屏蔽中断请求

- 输入,上升沿有效

- 有效时表示外界向CPU发出不可屏蔽中断请求,与IF无关

- 处理掉电等系统故障

- 不能被CPU屏蔽,优先级高于INTR

- 不可通过程序设置

NMI 与 INTR 的区别

| NMI | INTR | |

| 名称 | 不可屏蔽中断请求 | 可屏蔽中断请求 |

|

中断类型 |

外中断 | 外中断 |

| 中断类型号 | 2型 | 由外设提供 n型 |

| IF | 无关 | IF = 1 开;IF = 0 关 |

| 触发方式 | 边沿(上升沿) | 高电平有效 |

| 响应信号 | 无 |

INTA* |

| 相应条件 | 当前指令执行结束 | 开中断、指令结束 |

17、总线请求和响应引脚——HOLD 总线请求

- 输入,高电平有效

- 表示总线请求设备向CPU申请占有总线

- 通知CPU收回对总线的控制权

18、HLDA 总线响应

- 输出,高电平有效

- 表示CPU已响应总线请求并已将总线释放

- 此时CPU的地址总线、数据总线及具有三态输出能力的控制总线将全面呈现

19、RESET 复位请求

- 输入,高电平有效

- 当该信号有效时,将使CPU初始化

-

86/88复位后,

CS = FFFFH、其他寄存器,包括:IP = 0000H

20、CLK 时钟输入

- 给CPU提供内部定时信号

21、Vcc 电源输入

- 向CPU提供+5V电源

22、GND 接地

8088的引脚接地,则工作于最大工作模式:MN/MX* = 0

23、MN/MX* 工作模式选择

- 接高电平时MIN,86/88工作在最小模式

- 低电平时MAX,在最大模式

引脚小结:

-

CPU引脚分成三类系统总线信号:

- 8088:8位数据线:D0~D7

-

8086:16位

数据线

:D0~D15 -

20位

地址线

:A0~A19 -

控制线

:- ALE、IO/M*(8086:M/IO*)、WR*、RD*、READY、INTR、INTA*、NMI

- HOLD、HLDA

- RESET、CLK、Vcc、GND

-

地址总线(AB)

-

单向、三态

总线,用于传送

地址信息

-

其位数决定可直接寻址的范围

-

-

-

数据总线(DB)

- 双向,三态总线,用于传送数据信息

- 其位数有8位,16位,32位,64位等

-

-

控制总线(CB)

- 传送控制,状态信息

- CPU对主存或外设接口的读(RD)或写(WR)信号

引脚注意点

-

-

8086写I/O总线周期的控制信号,一直保持低电平有效的是:M/IO*

-

版权声明:本文为A_lIjInnUo原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接和本声明。