简介

峰值检测电路是一种检测信号在某一周期内峰值的电路,当输入信号上升大于前次采样的信号时,电路工作与采样状态,并且跟踪输入信号。当输入信号下降时,保持采样值。其输出为一个采样周期的峰值。

原理

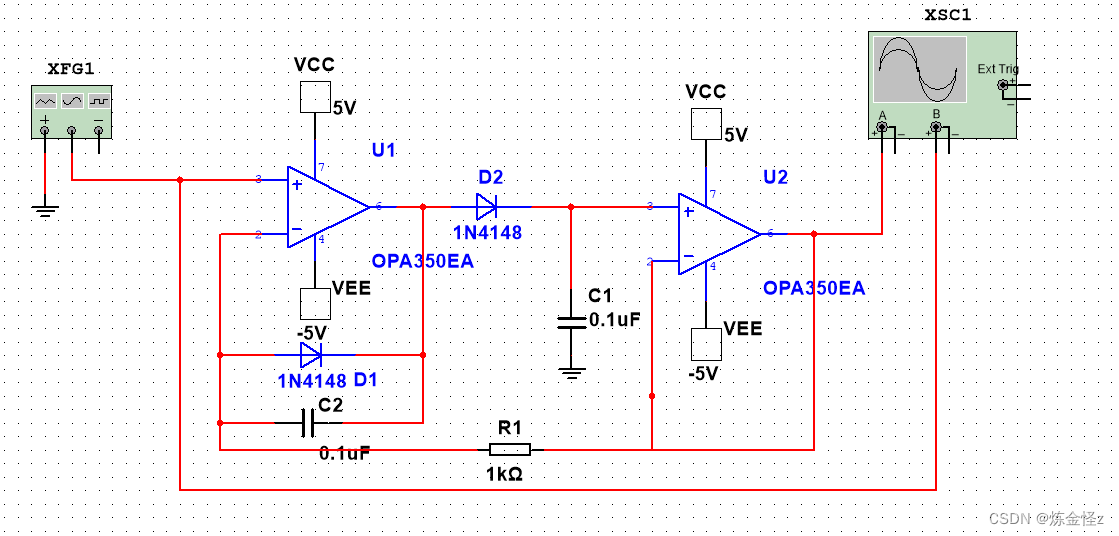

如图所示为一种由同相运算放大器构成的峰值检波电路。

当ui大于电容C两端的保持电压值时,D1 截止,D2导通,电路进人采样周期,ui=uo。当ui下降时,U1同相端电位低于反相端,使V导通,保持电容C复位。

输入信号峰值=1VPP

版权声明:本文为qq_45890466原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接和本声明。