本系统设计实现得功能是:

实现数据采集,采集上位机发送的ASK信号,然后通过串口发送采集到的数据。

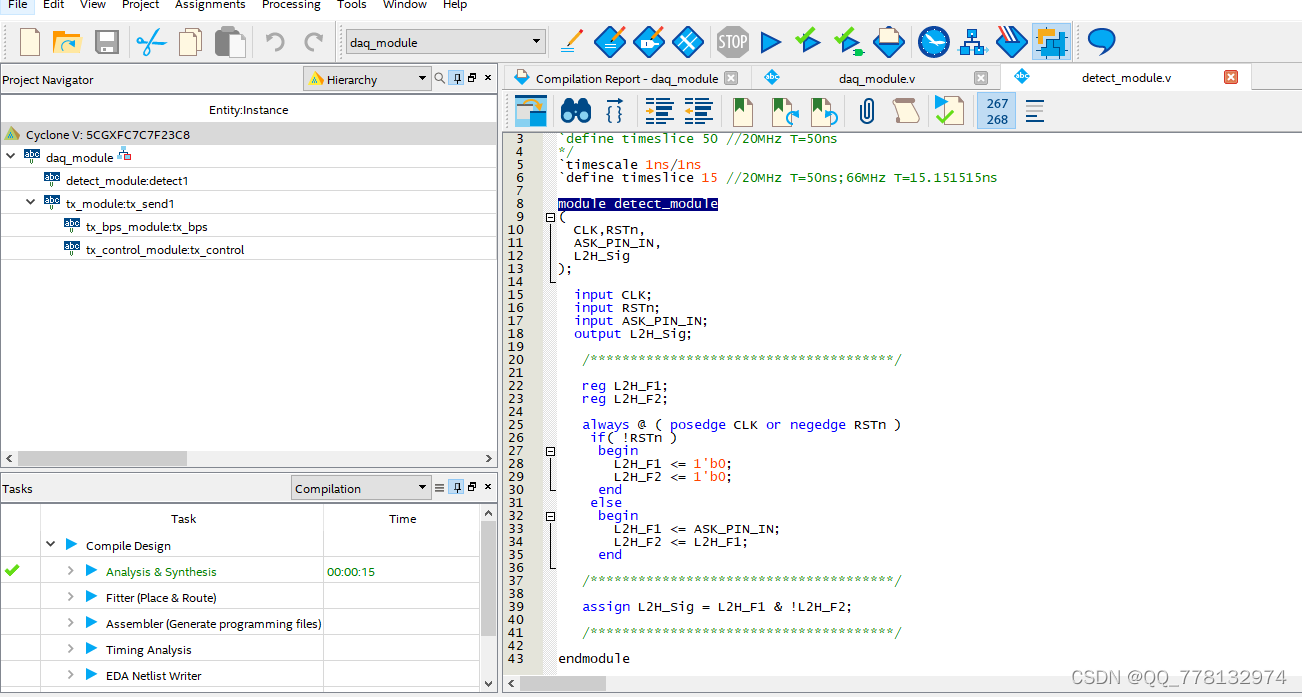

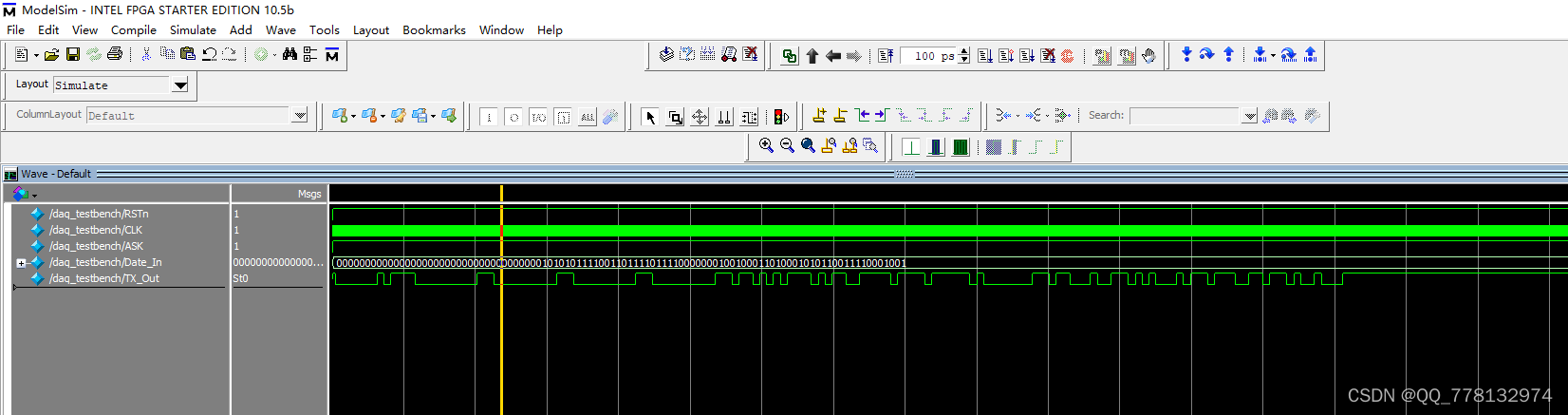

本系统在quartusII下实现,并在modelsim下进行仿真实现,也可在vivado下实现。

下面是工程截图和仿真截图:

该系统顶层模块代码如下:

/*

timescale 1ns/1ns

define timeslice 50 //20MHz T=50ns

*/

timescale 1ns/1ns

define timeslice 15 //20MHz T=50ns;66MHz T=15.151515ns

module daq_module

(

RSTn,CLK,

ASK_PIN_IN,

Date_In,

TX_Out

);

output TX_Out;

input RSTn

版权声明:本文为QQ_778132974原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接和本声明。