PYNQ-Z2使用Vitis2020.2新建PS端开发工程

-

软件版本:

Vitis2020.2

开发套件 -

PYNQ开发包资料:

密码:l4gl

-

将PYNQ-Z2资料包

Board_File

中的

PYNQ-Z2

文件夹复制到

Vitis

安装目录下

Vivado\2020.2\data\boards\board_files

,这样在创建工程时可以快速选择板卡文件

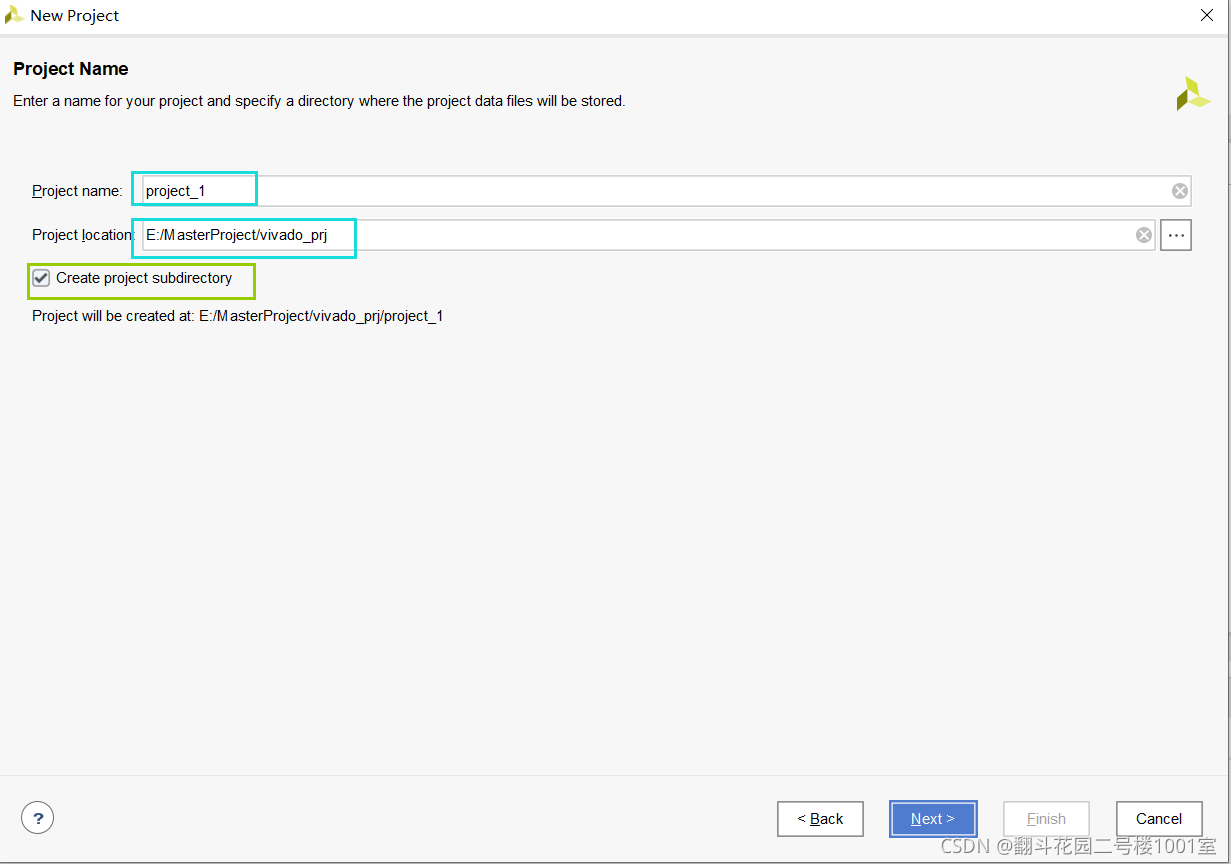

1、安装

Vitis

,打开

vivado

,左上角依次点击

File

–>

project

–>

New

,然后点击

next

,依次输入工程名,和存放的路径,如果勾选

Create project subdirectory

,那么会自动在刚才选择的存放路径下新建一个文件夹存放新的工程.

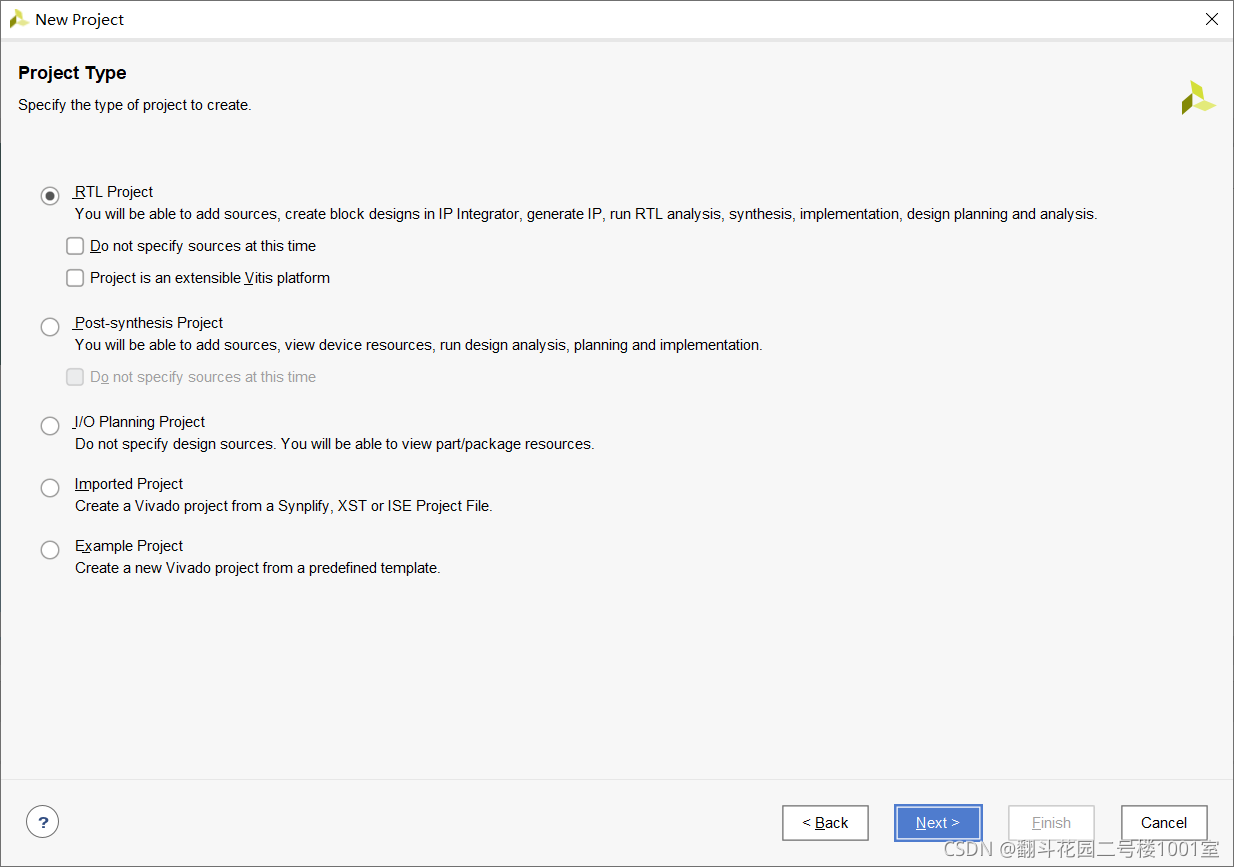

下一步选择

RTL Project

然后一直点击

next

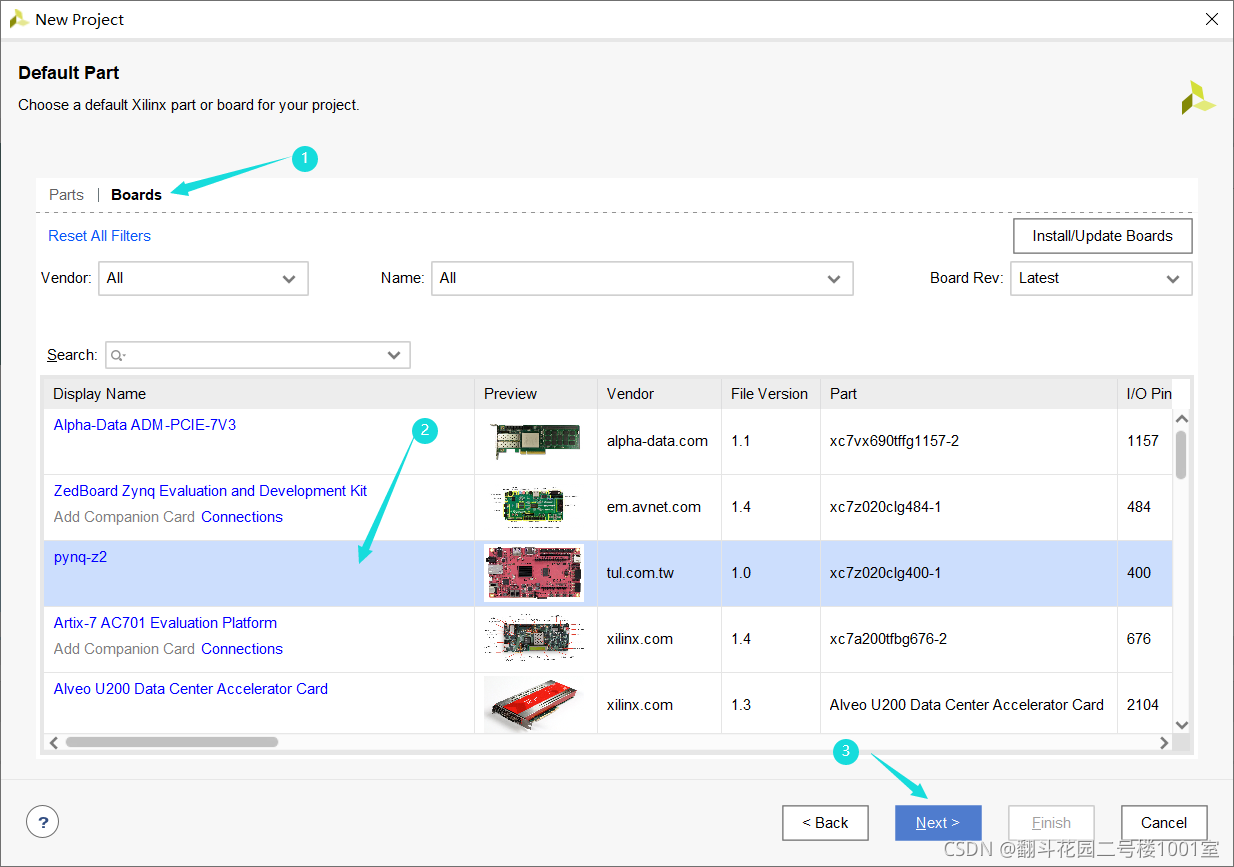

,这里让你选择你的芯片型号(如果你是其他的板子,直接选相应的型号就是了),我们直接点击

Boards

,选择我们导入的PYNQ-Z2板子(是因为我们前面将

pynq-z2

的

board file

复制到了相应的路径里,所以在这路可以直接选择)

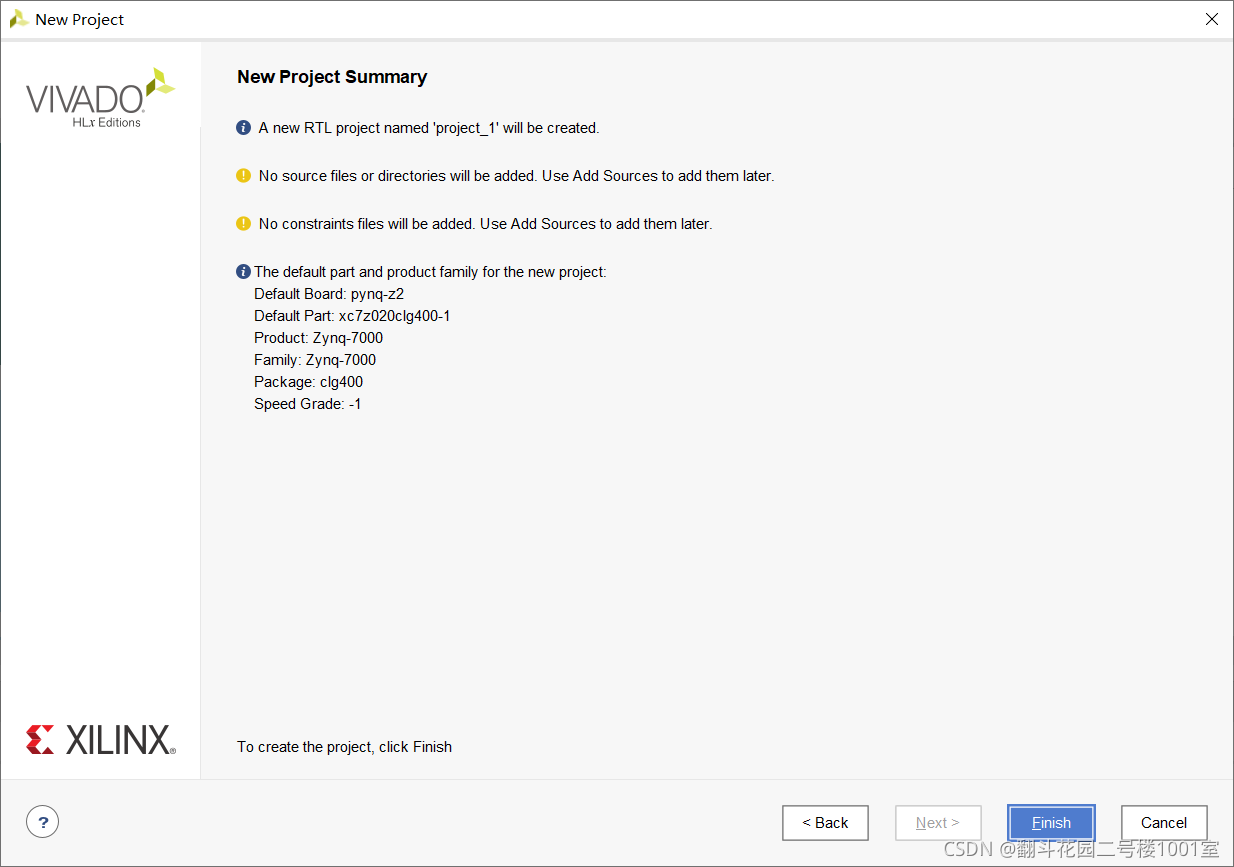

然后点击

next

,在这里我们可以看见我们所操作的全部信息,以及芯片的具体型号

点击

Finish

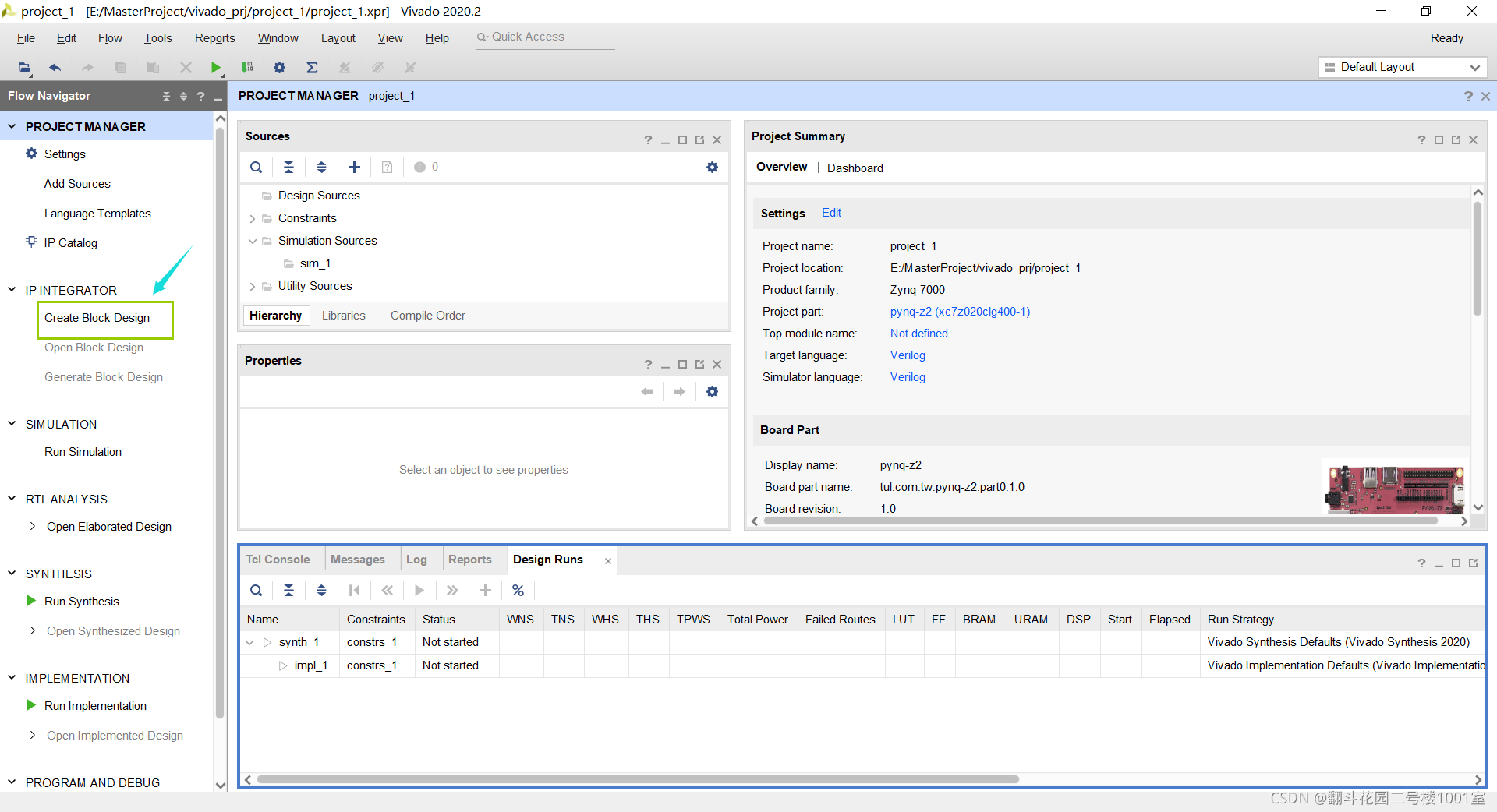

,等待工程的创建.创建完成后如下:

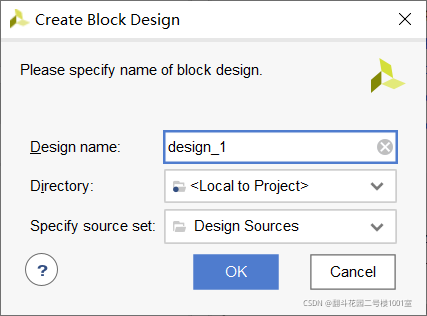

点击

Creat Block Design

,我们创建一个zynq的ip核,直接点击

ok

.

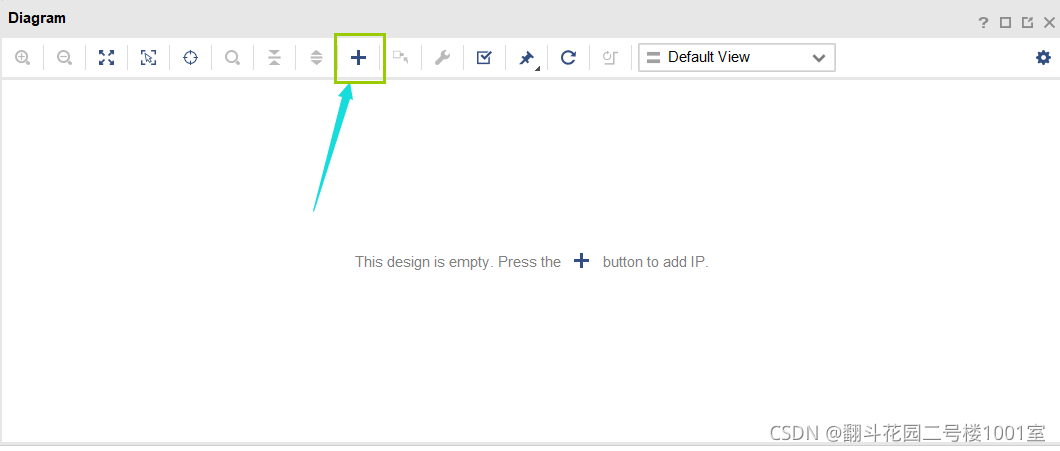

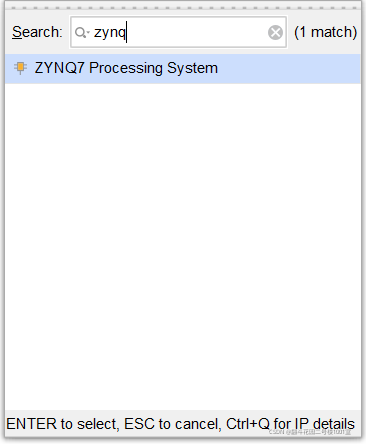

点击

+

号

输入

zynq

,点击

ZYNQ7

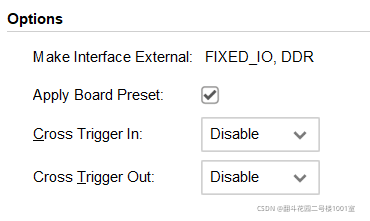

直接点击

Run Block Automation

,这里注意

Apply Board Preset

一定要打钩,这样我们前面复制的

board file

会自动将

ddr

,

时钟

等基本配置给设置好,就不用一个一个要我们去设置了.然后点击

ok

就会得到如下所示:

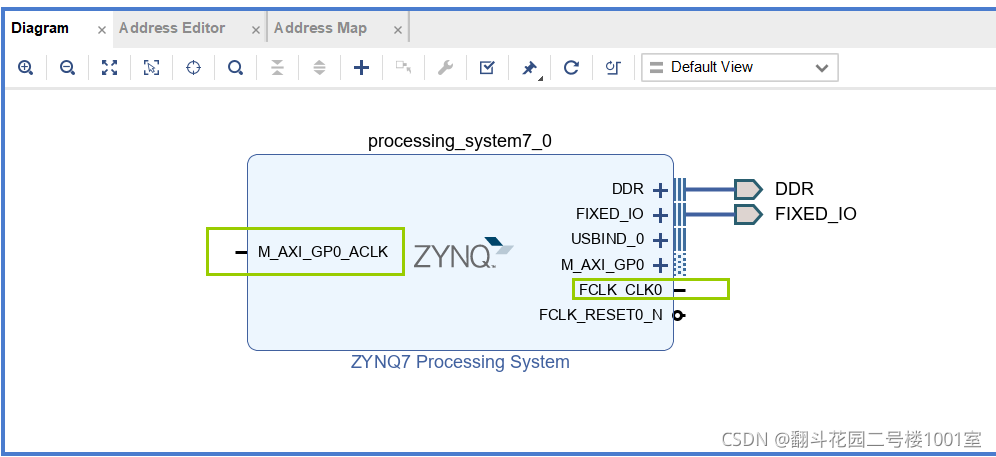

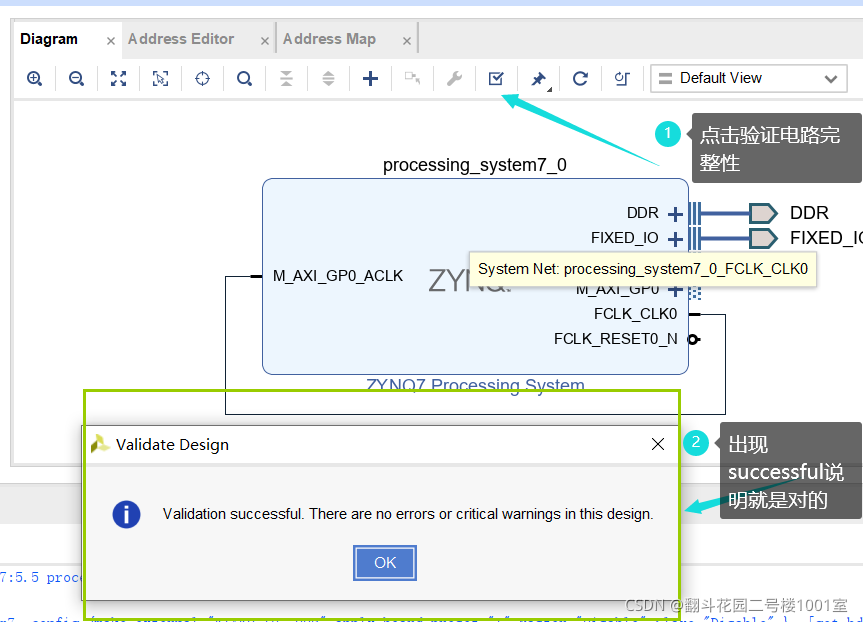

我们将方框中的时钟连接起来.,并点击图中的方框钩,验证电路完整性

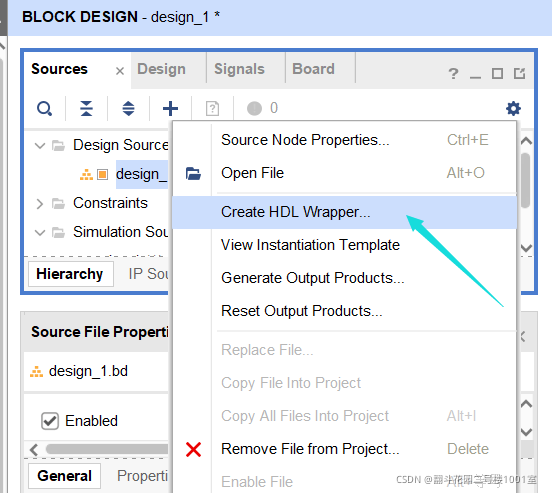

在左边的

Sources

栏中,右键我们创建的ip,点击

Creat HDL Wrapper

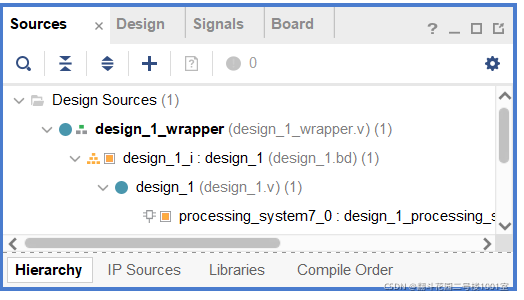

保持默认,点击ok.这样我们顶层的Verilog模块就出来了,可以看见有个.v文件

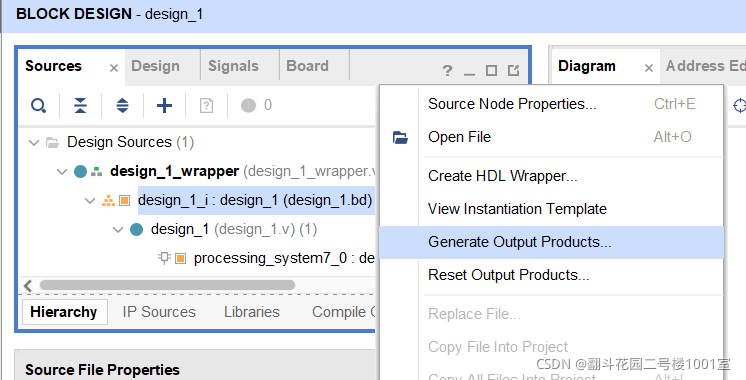

再次右键我们的模块,点击

Generate Output Products

,

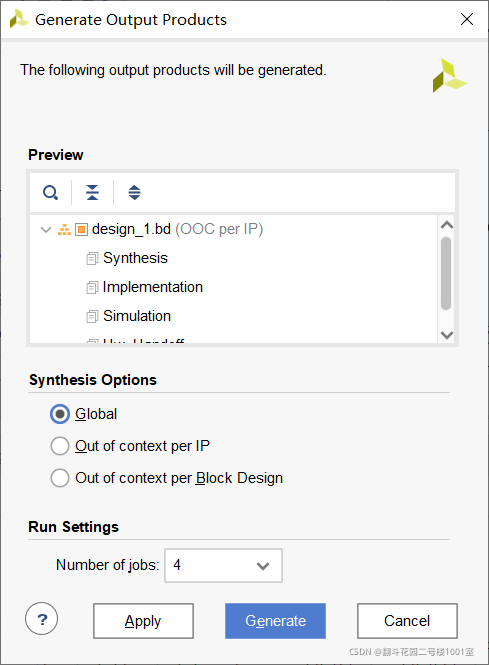

选择

Global,

–>

Generate

等待…

创建成功

左上角,依次

File

–>

Export

–>

Export HardWare

,一直保持默认点击下去,并

Finish

.这样我们

Vivado

的工作就做完啦.

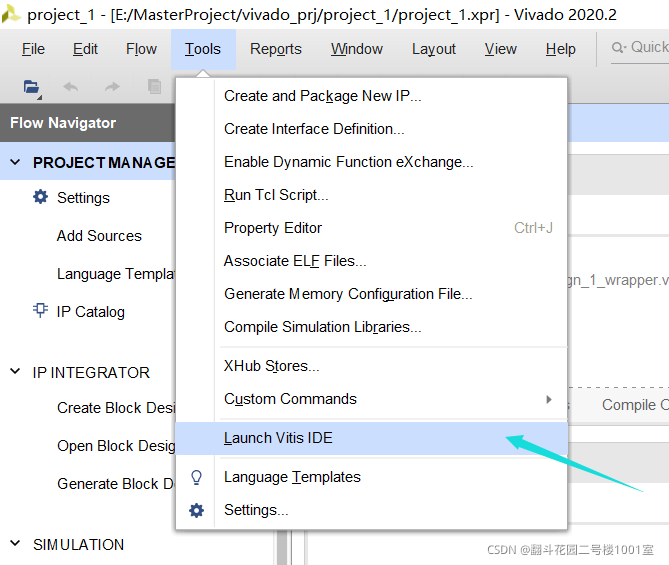

现在启动

Vitis

,在工具栏中选择

Tools

–>

Launch Vitis IDE

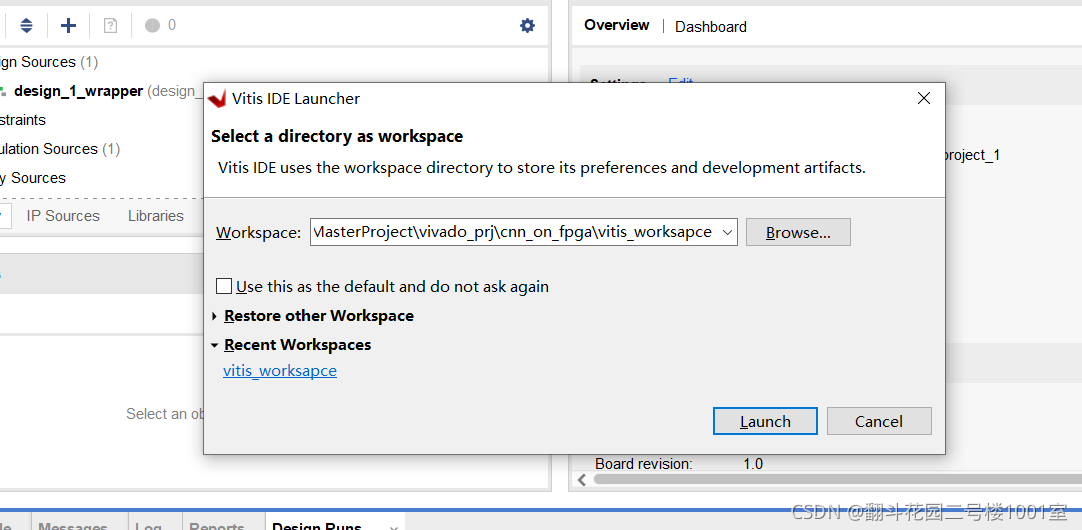

选择一个路径作为你的

work space

,点击

launch

.

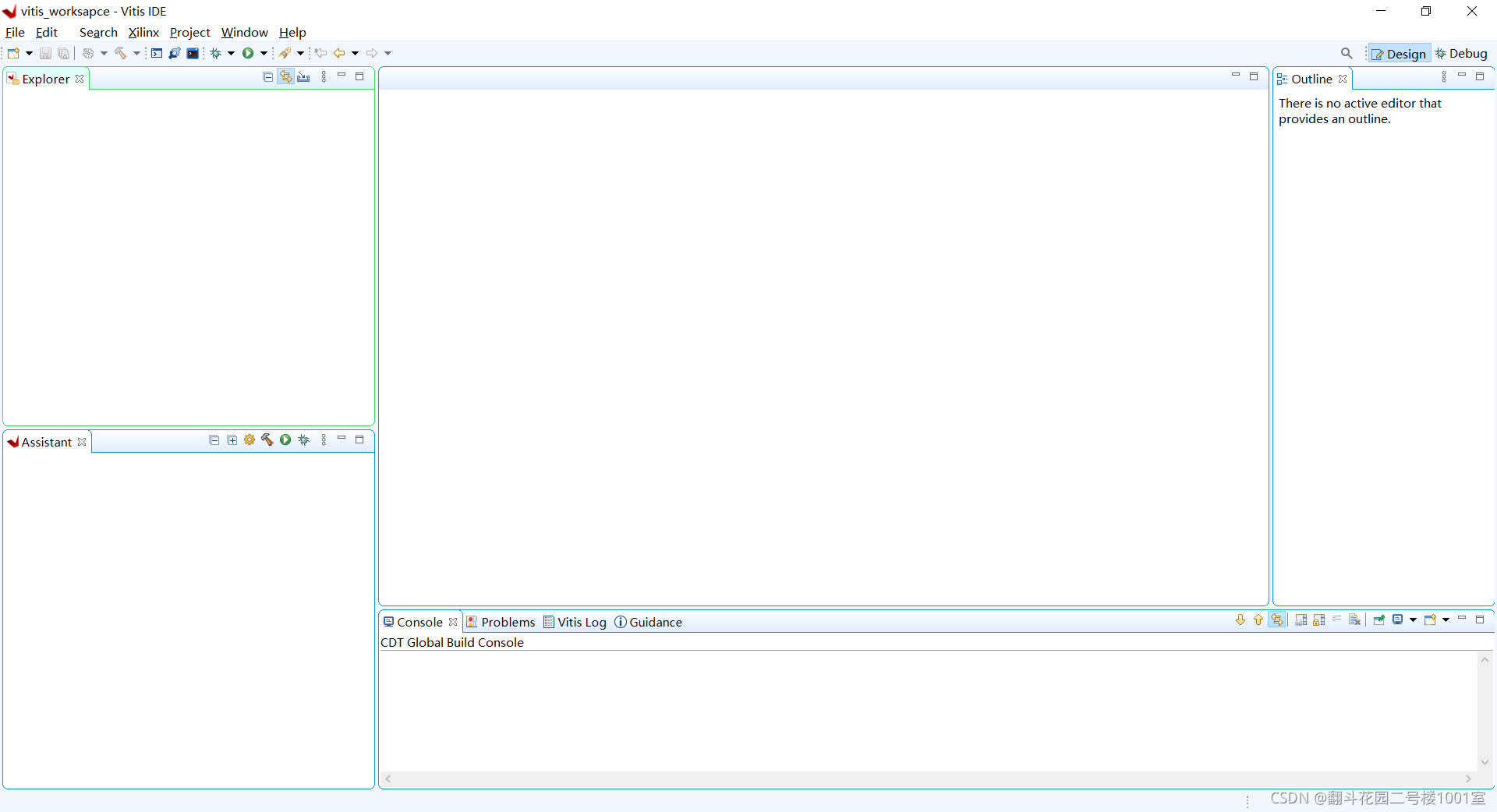

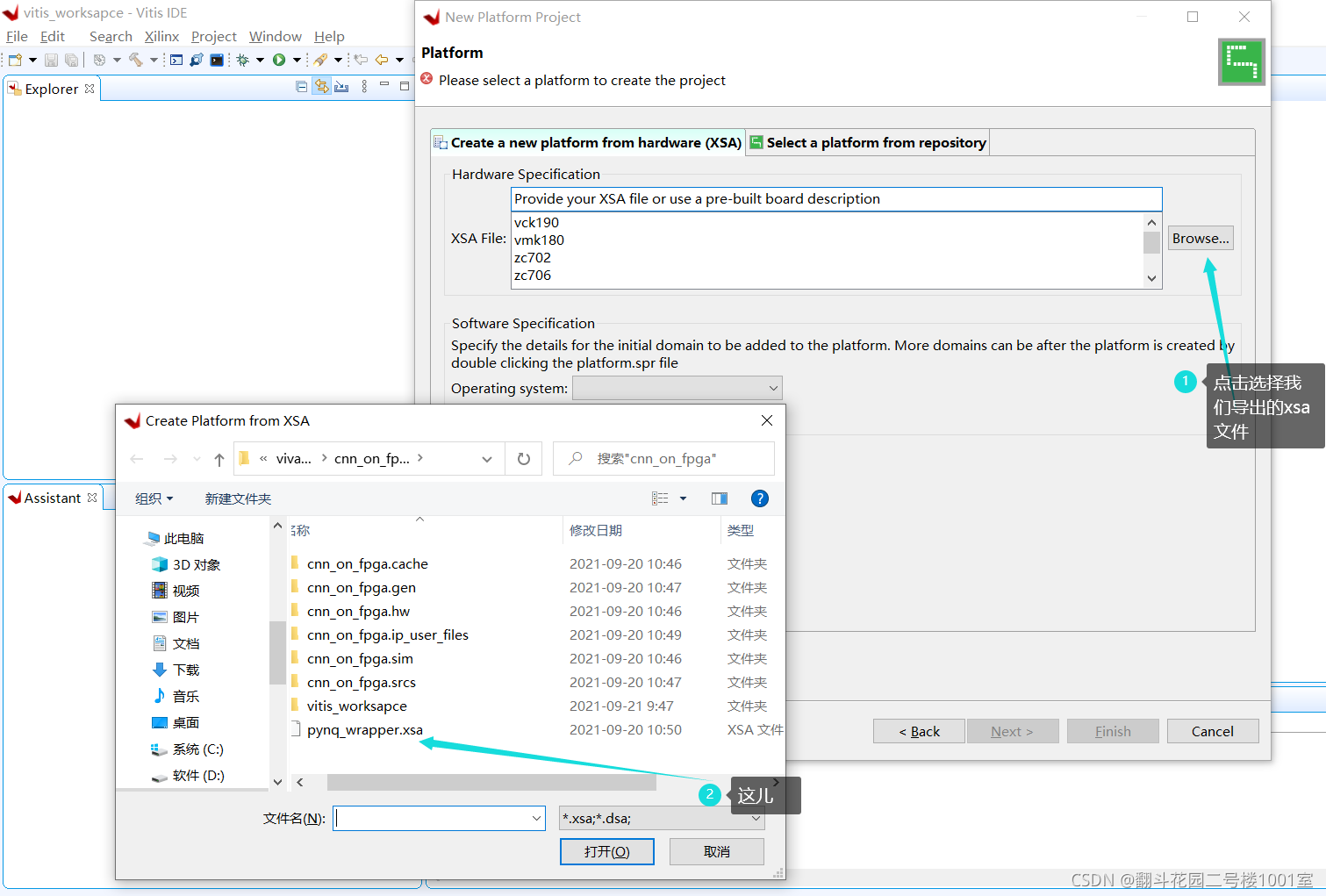

进入

Vitis

的主界面

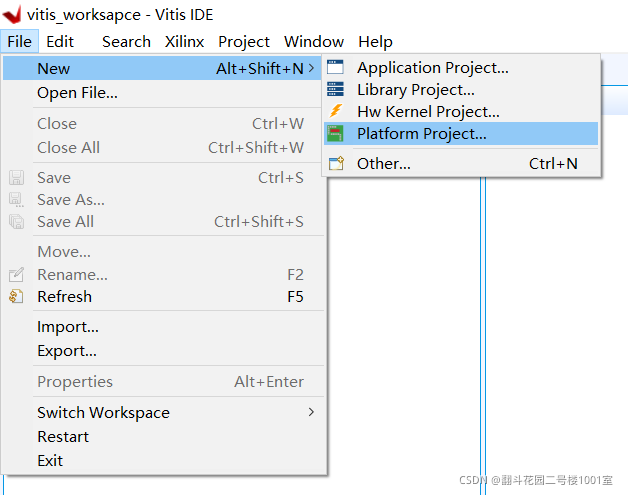

左上角

File

–>

New

–>

Platform Project

输入

Platform

的工程名,点击

next

,在这里我们选择我们之前在

Vivado

中导出的

xsa

文件,选择完成

Finish

.这样

Platform

创建完成.

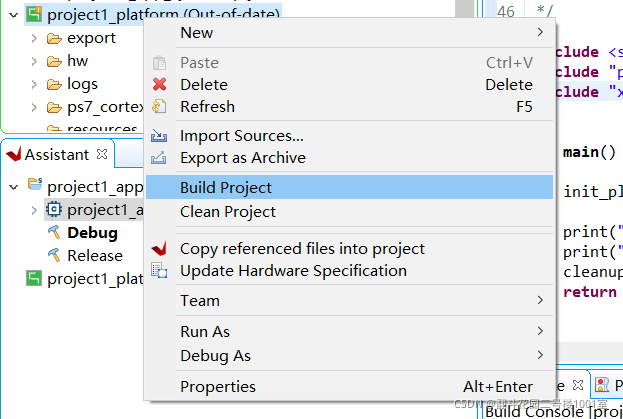

右键

Platform Project

,点击

Build Projet

,我们编译一下

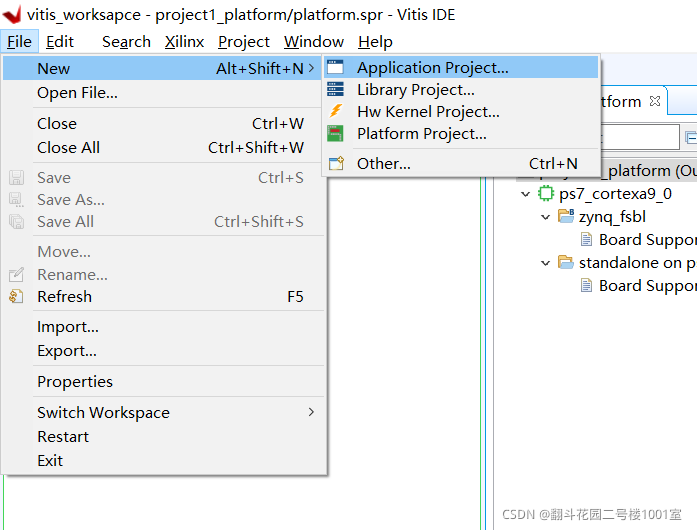

接下来创建应用开发工程,他必须是依托platform创建,左上角

File

–>

New

–>

Application Project

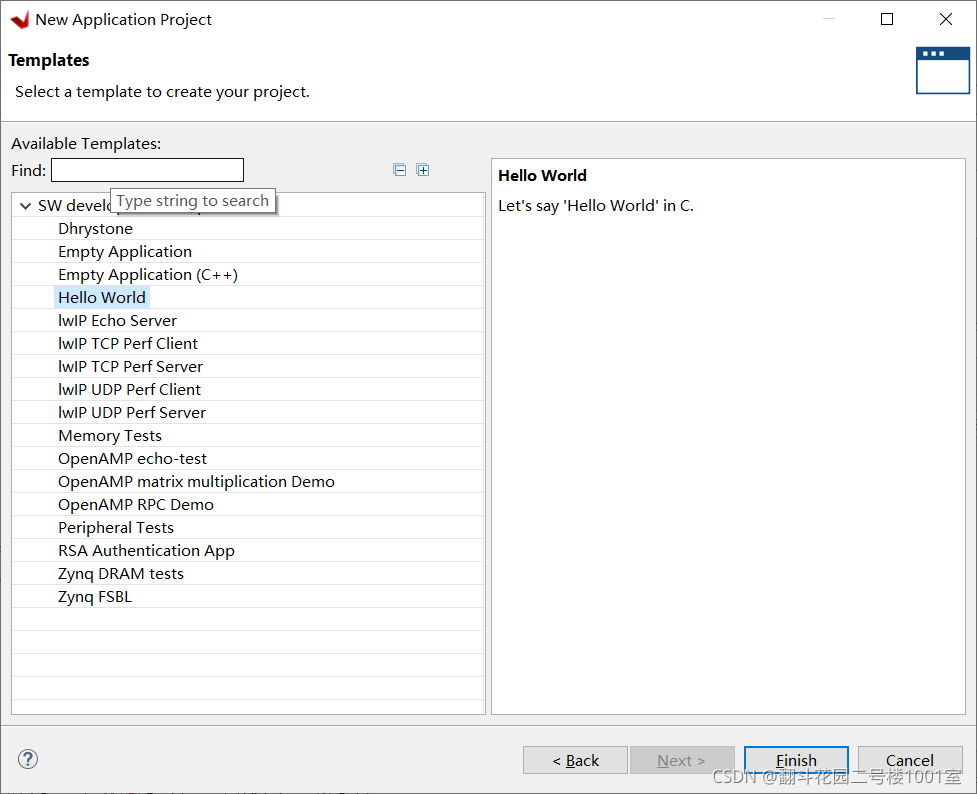

一路一直next下去,该输入的就输入名字,我们选择一个

hello world

工程.

Finish

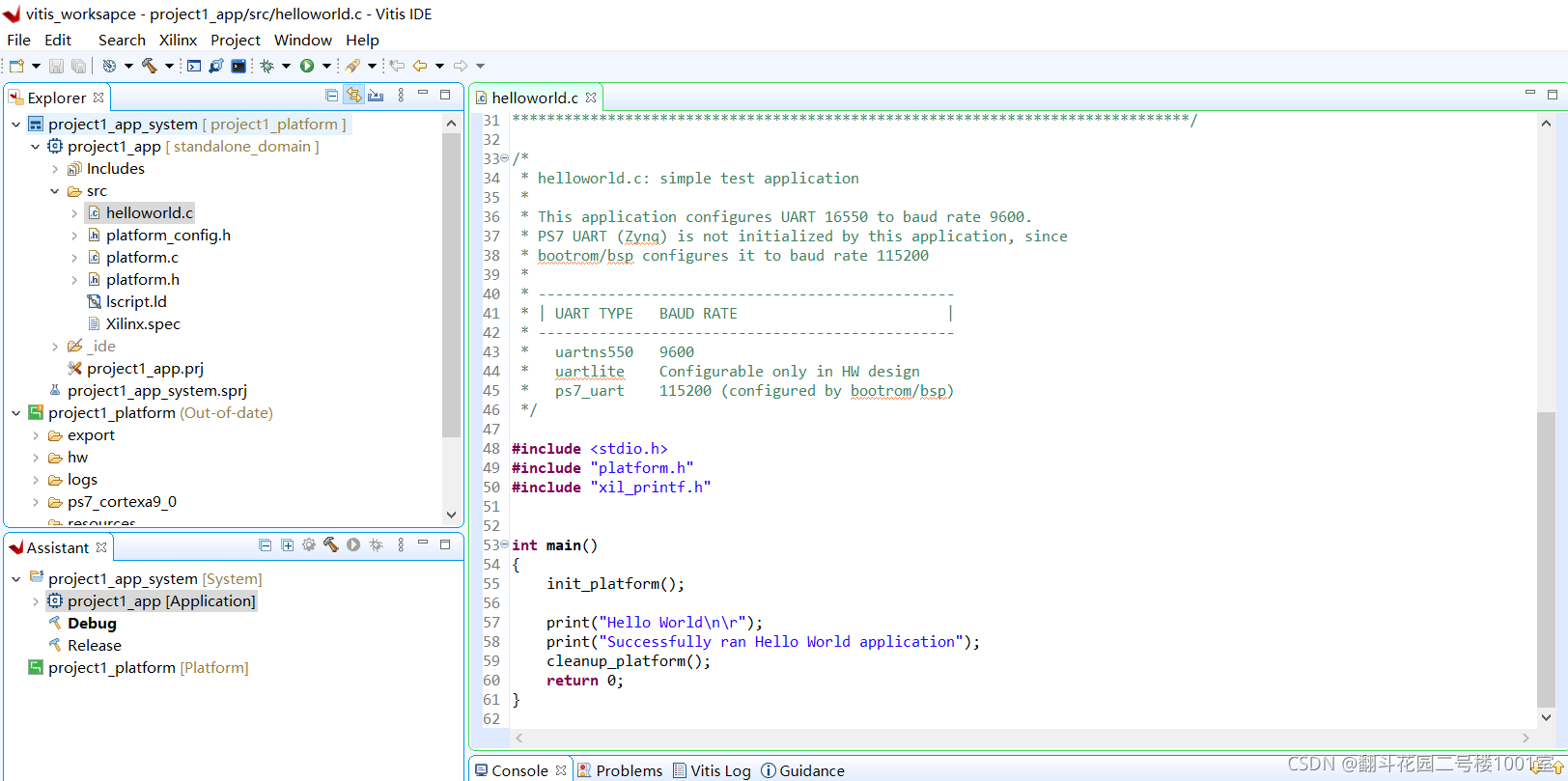

,然后就创建完毕啦.

在左边

src

文件夹下我们可以看见源码

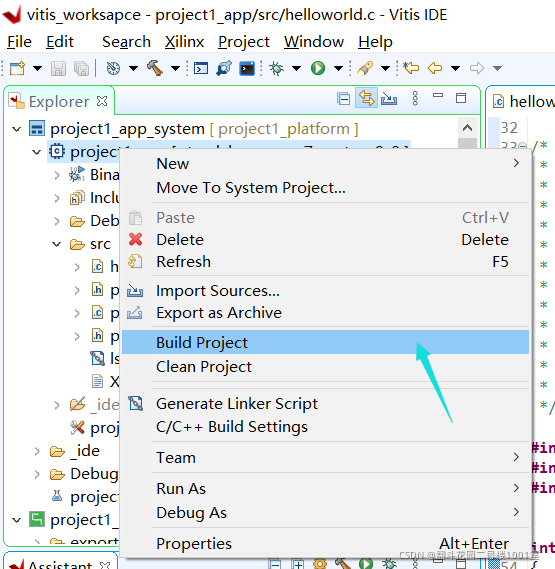

我们依然需要

Build

一下

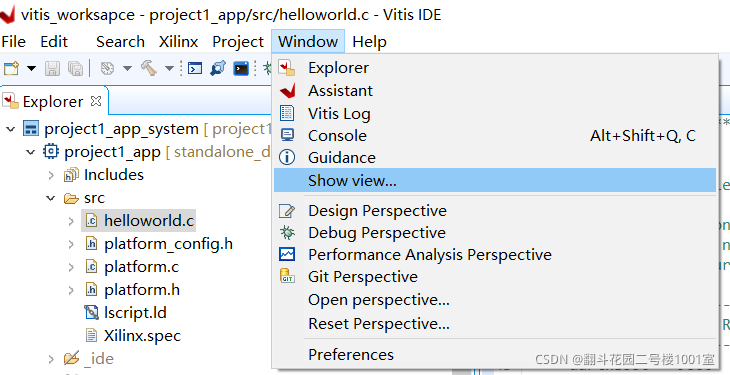

开发板上电,跳冒接到

JTAG

,在工具栏中选择

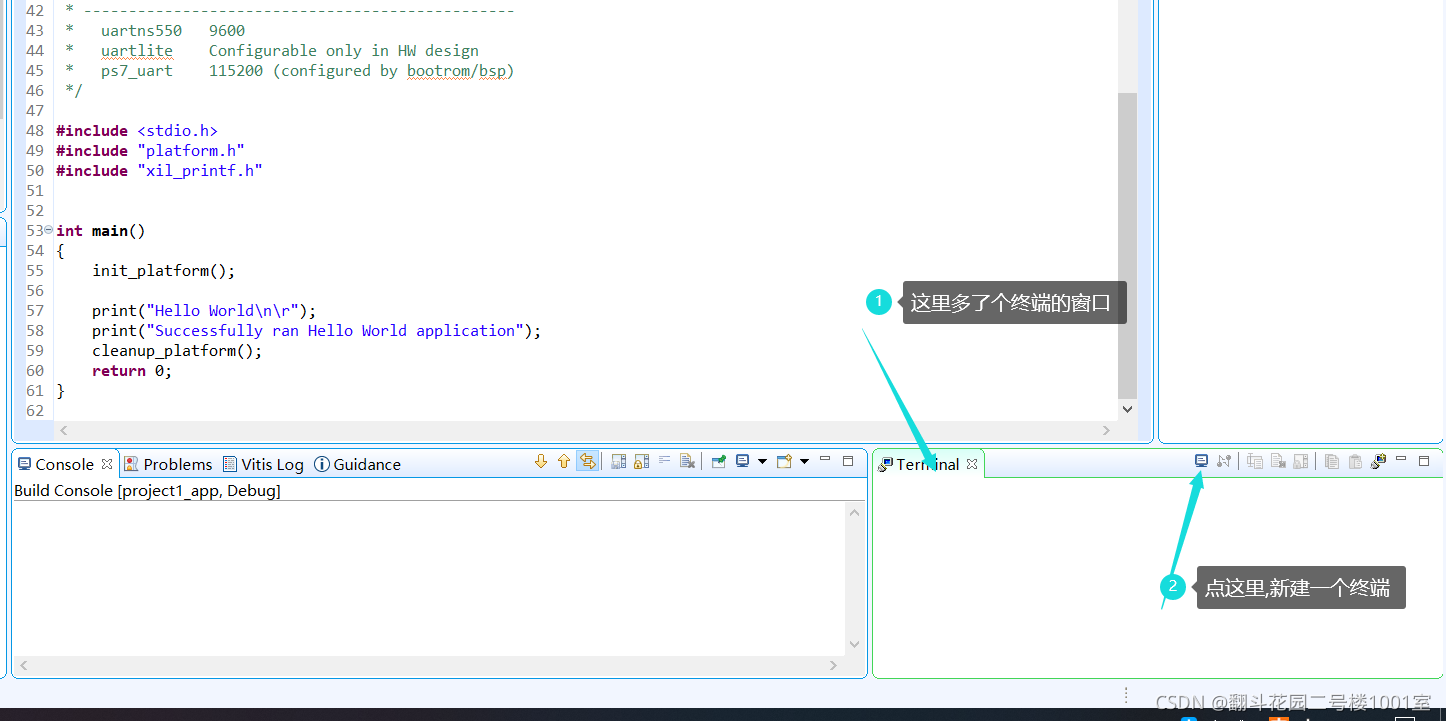

window

–>

show View

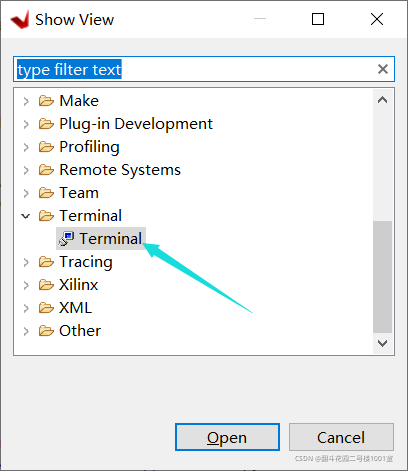

,我们创建一个串口终端.方便接收打印输出.

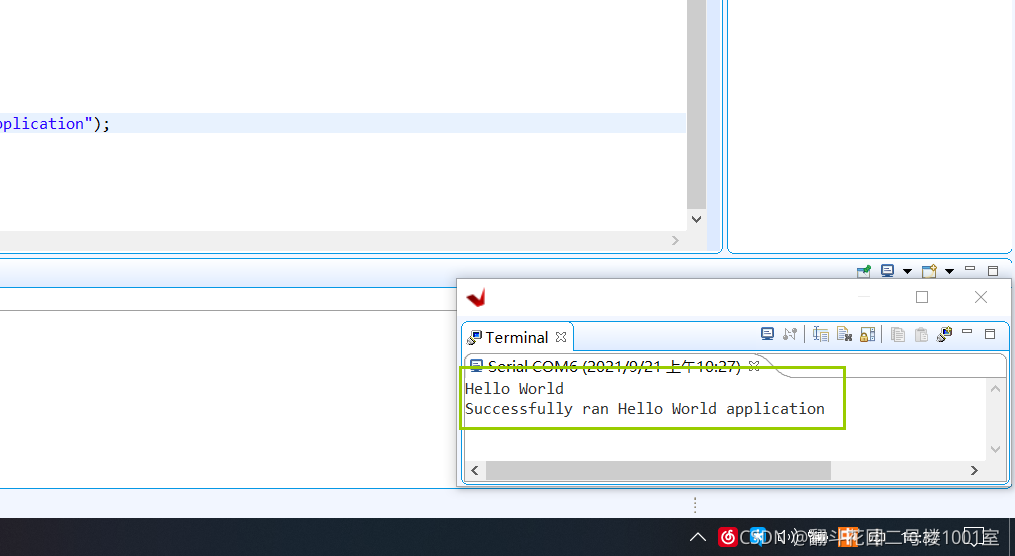

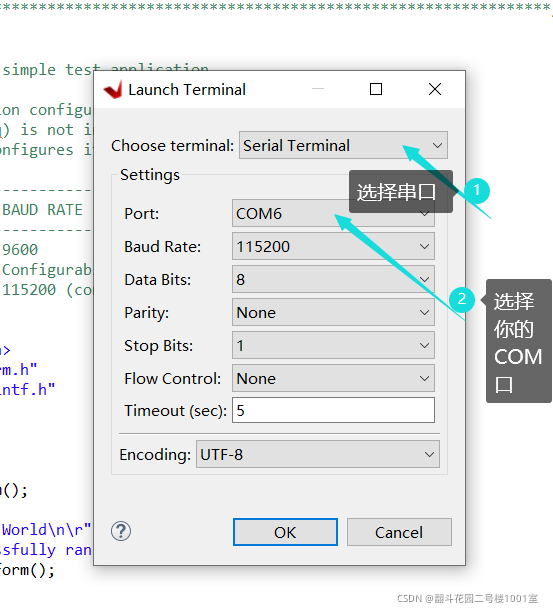

选择

Terminal

右下角多出一个窗口,我们点击

2

,新建一个终端

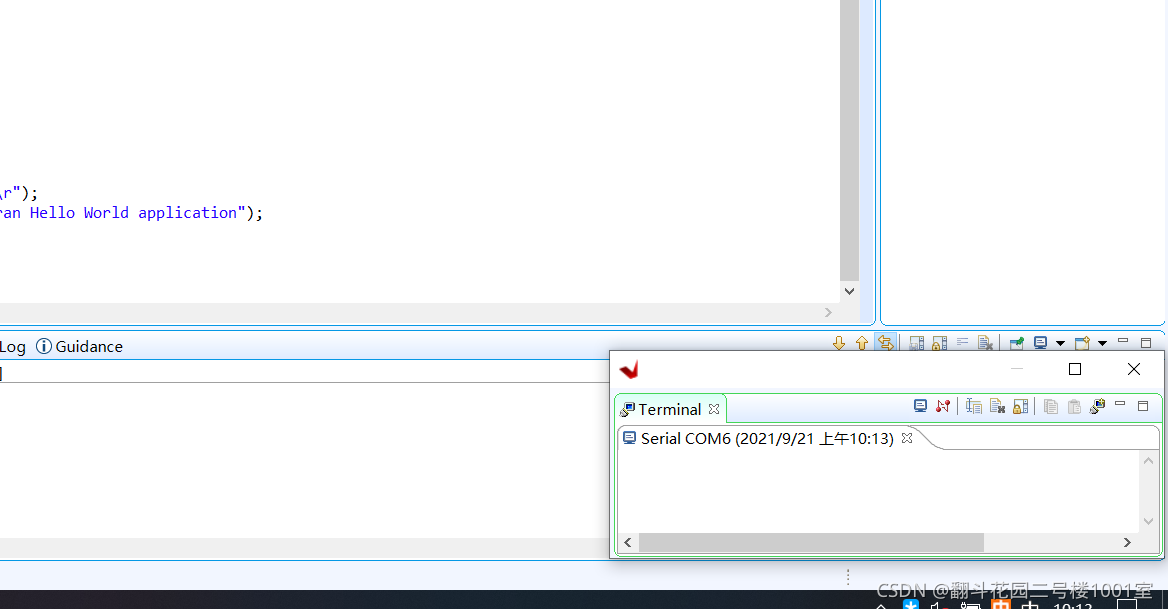

连接成功

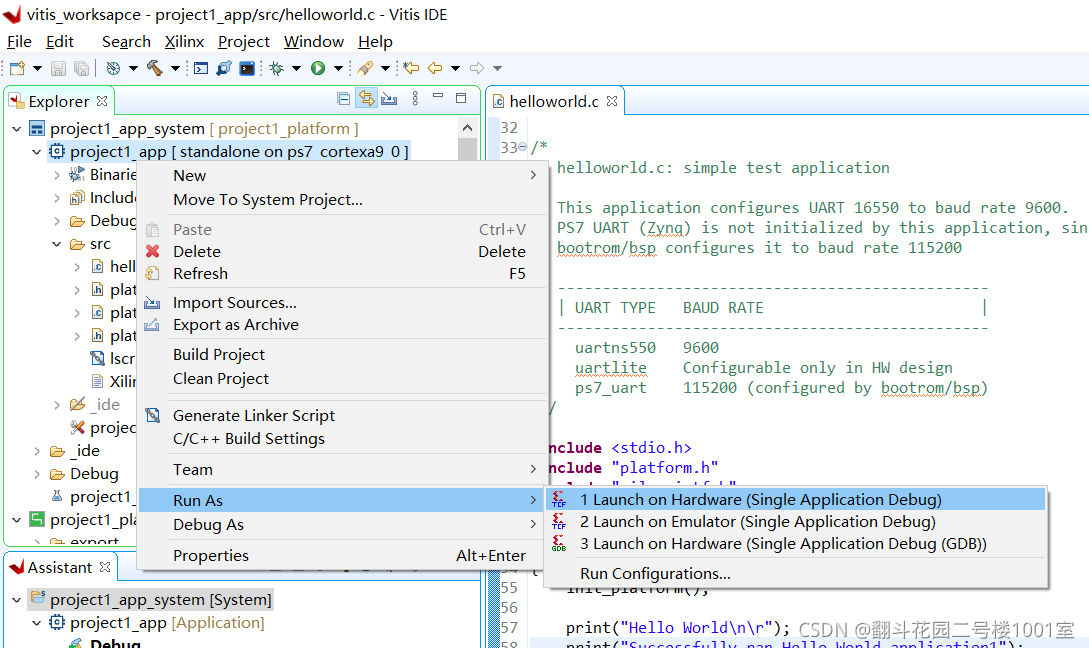

我们运行一下,右键

工程

,选择

run

输出了

Hello world

,整个工程创建成功.