Verilog Language

1.Basics

1.0

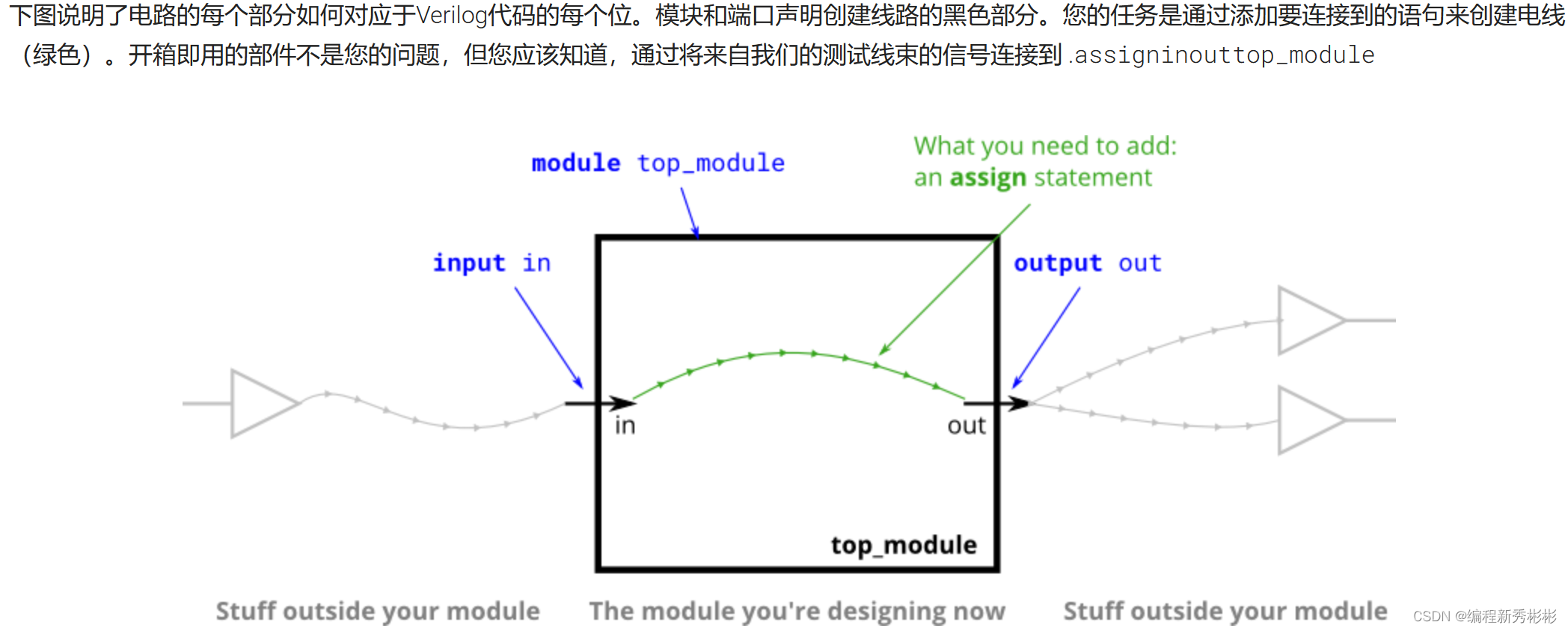

1.1 Simple wire

创建一个具有一个输入和一个输出的模块,其行为类似于电线。

module top_module( input in, output out );

assign out = in;

// Note that wires are directional, so "assign in = out" is not equivalent.

endmodule

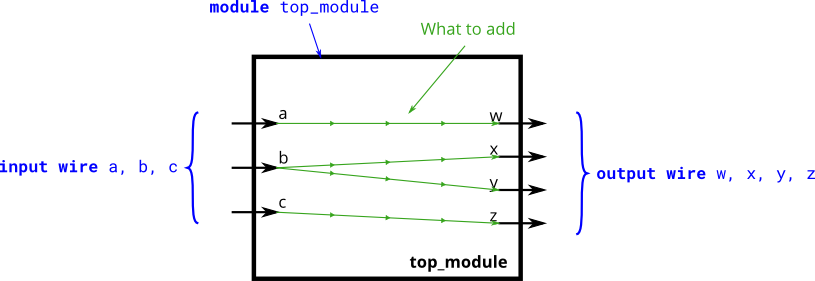

1.2 Four wires

创建一个具有 3 个输入和 4 个输出的模块,其行为类似于建立这些连接的电线:

a -> w

b -> x

b -> y

c -> z

下图说明了电路的每个部分如何对应于Verilog代码的每个位。 从模块外部,有三个输入端口和四个输出端口。

module top_module (

input a,b,c,

output w,x,y,z );

assign w = a;

assign x = b;

assign y = b;

assign z = c;

// If we're certain about the width of each signal, using

// the concatenation operator is equivalent and shorter:

// assign {w,x,y,z} = {a,b,b,c};

endmodule

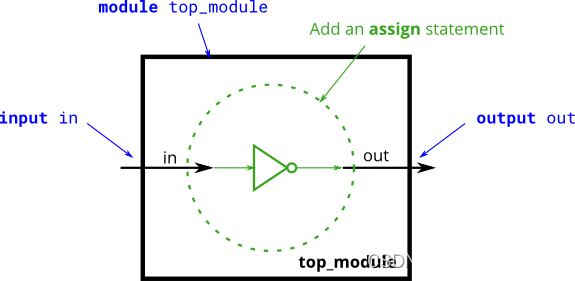

1.3 Inverter(NOT gate)(非门)

创建一个实现 NOT 门的模块。

该电路类似于线,但略有不同。当从导线连接到导线时,我们将实现逆变器(或“非门”)而不是普通导线。

NOT gate(非门),逻辑取反符号!,按位取反符号~

module top_module(

input in,

output out

);

assign out = ~in;

endmodule

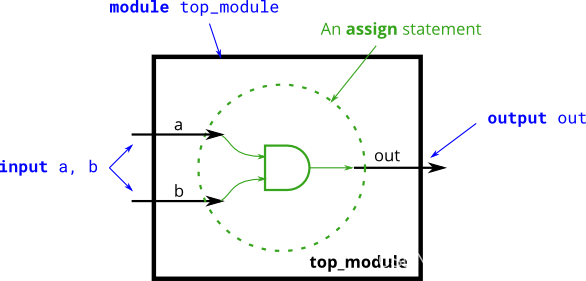

1.4 AND gate(与门)

创建实现 AND 门的模块。

Verilog有独立的位与(&)和逻辑与(&&)操作符,就像c一样。在这里使用的是一位操作符,所以选择哪个并不重要。

module top_module(

input a,

input b,

output out );

assign out=a&b;

endmodule

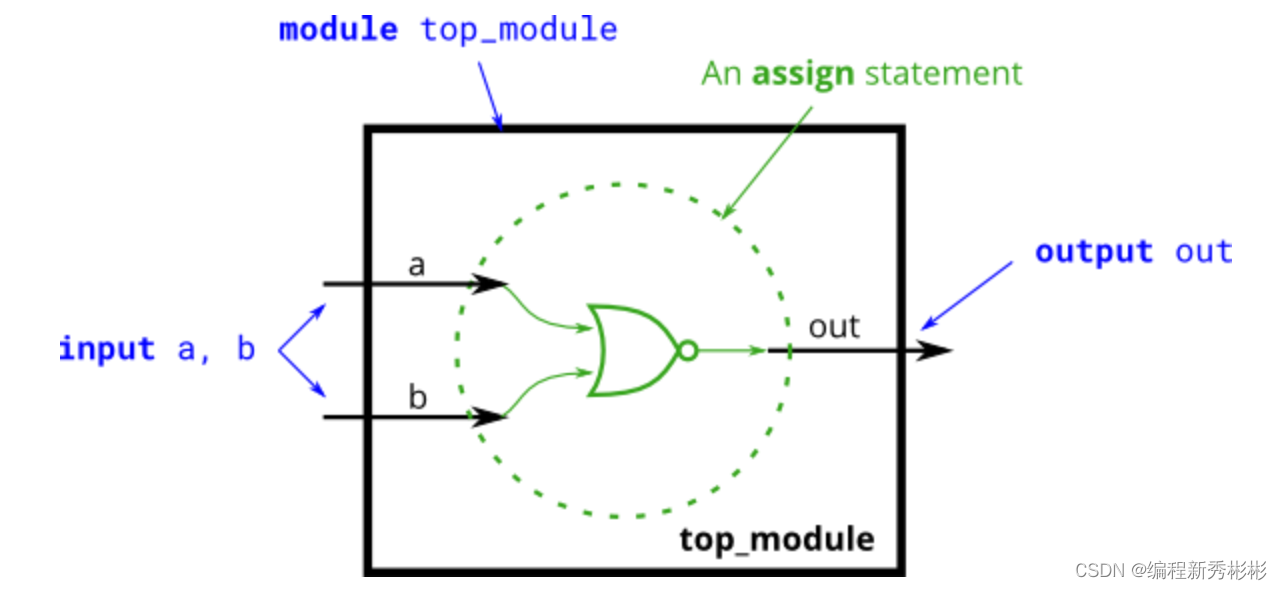

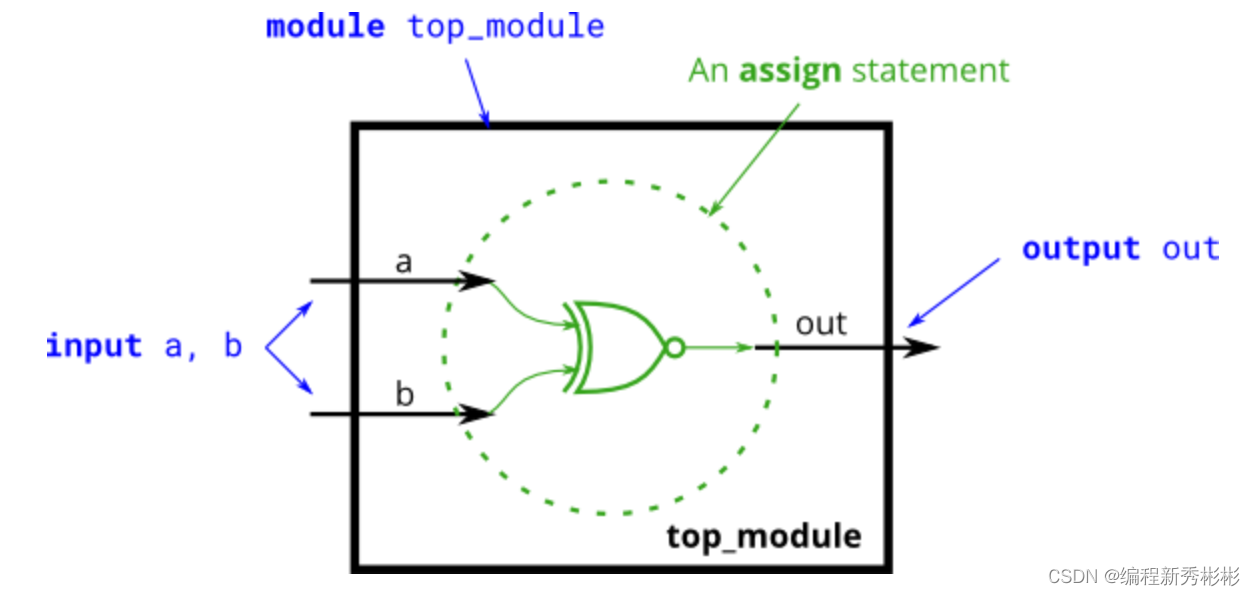

1.5 NOR gate(或非门)

创建实现 NOR 门的模块。NOR 门是输出反相的 OR 门。NOR 函数在 Verilog 中编写时需要两个运算符。

Verilog有独立的位或(|)和逻辑或(||)操作符,就像c一样。在这里使用的是一位操作符,所以选择哪个皆可。

module top_module(

input a,

input b,

output out );

assign out=!(a|b);

endmodule

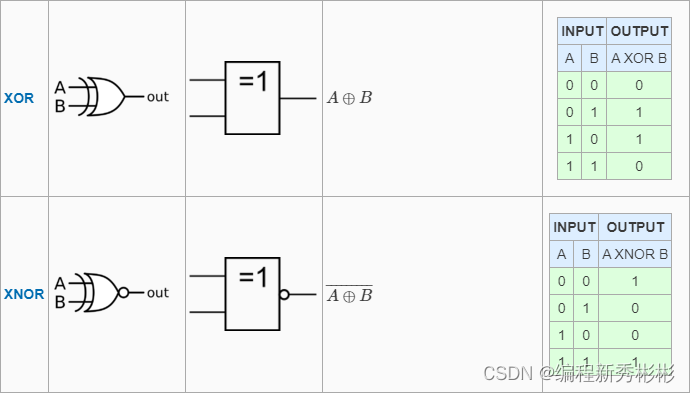

1.6 XNOR gate(同或门)

创建一个实现 XNOR 门的模块。

异或门 XOR

同或门 XNOR

位异或操作符是^,没有逻辑异或运算符。

module top_module(

input a,

input b,

output out );

assign out=a^~b;

endmodule

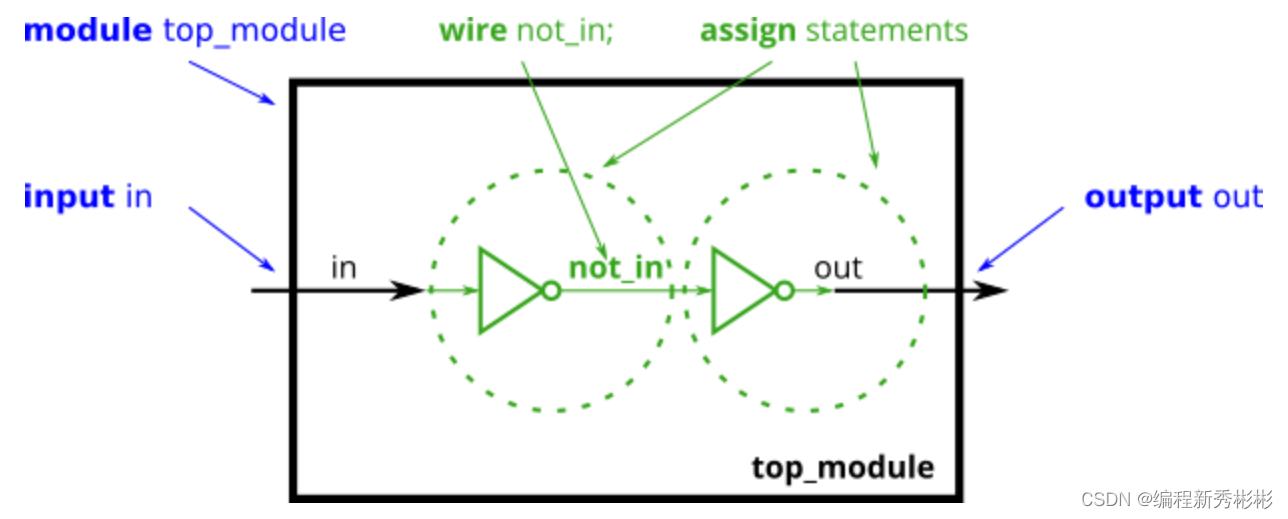

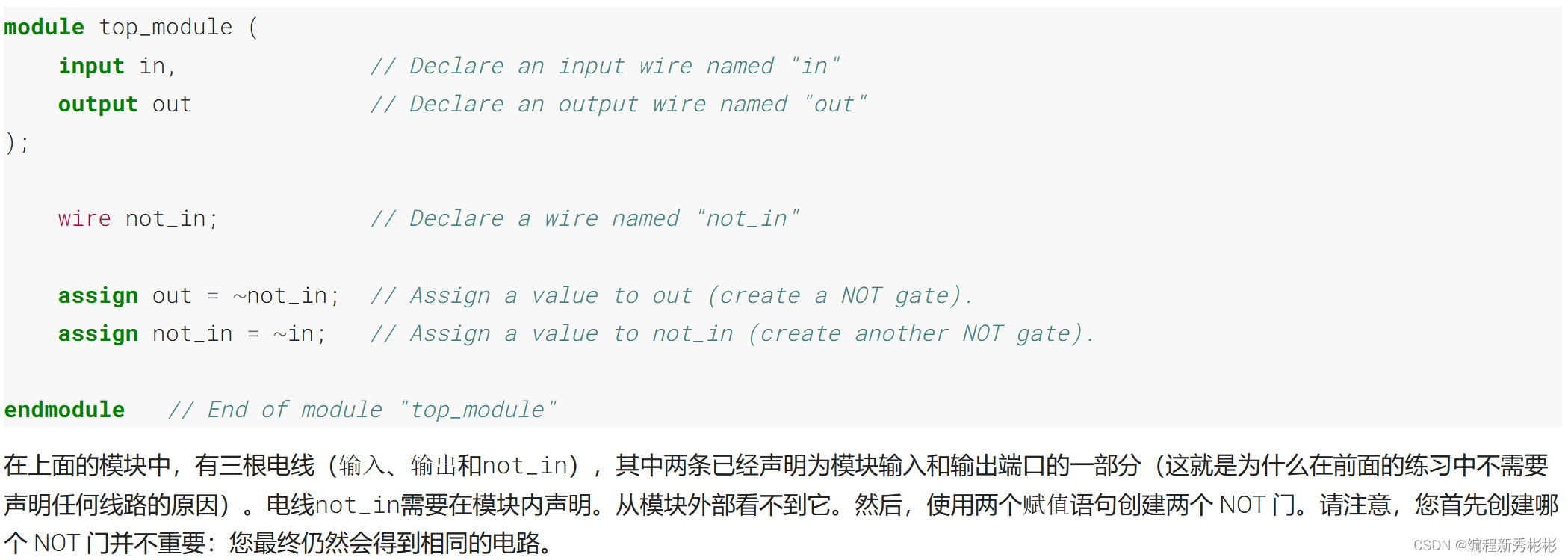

1.7 Declaring wires

到目前为止,电路非常简单,输出是输入的简单功能。随着电路变得越来越复杂,需要电线将内部组件连接在一起。当需要使用电线时,应该在模块的主体中声明它,在首次使用之前的某个地方。

例

实践

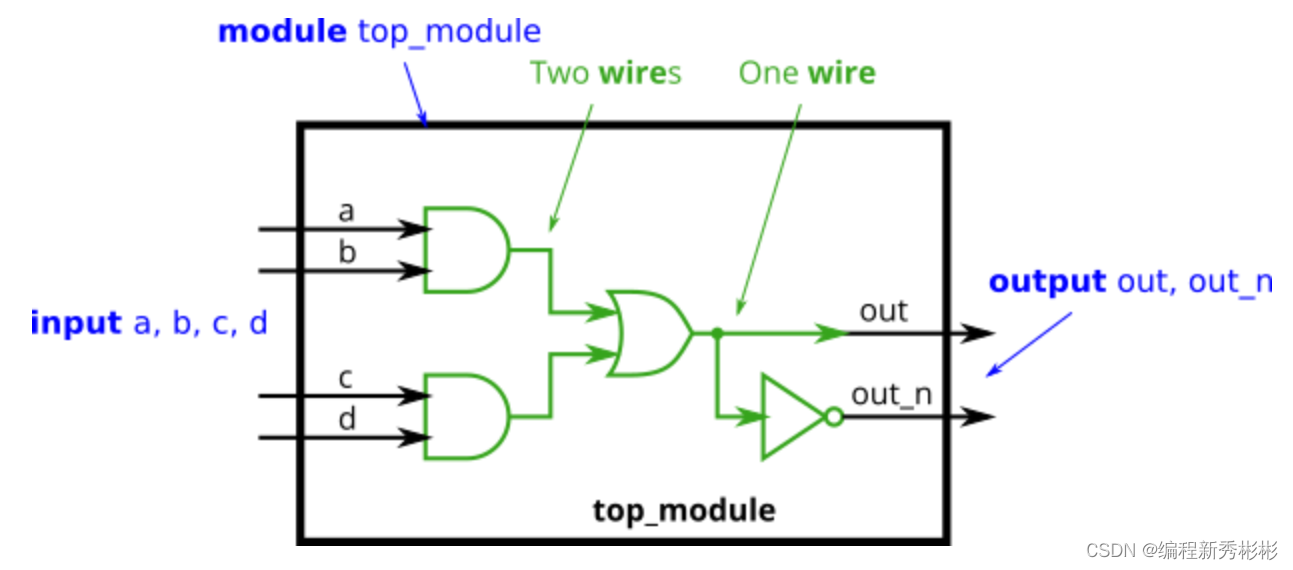

实现以下电路。创建两条中间导线(命名为您想要的任何名称)以将 AND 和 OR 门连接在一起。请注意,馈入 NOT 门的导线实际上是导线输出,因此您不一定需要在此处声明第三根导线。如果您遵循图中的电路结构,则最终应该得到四个分配语句,因为有四个信号需要分配值。

`default_nettype none

module top_module(

input a,

input b,

input c,

input d,

output out,

output out_n );

wire wire1,wire2;

assign wire1=a&b;

assign wire2=c&d;

assign out=wire1|wire2;

assign out_n=~out;

endmodule

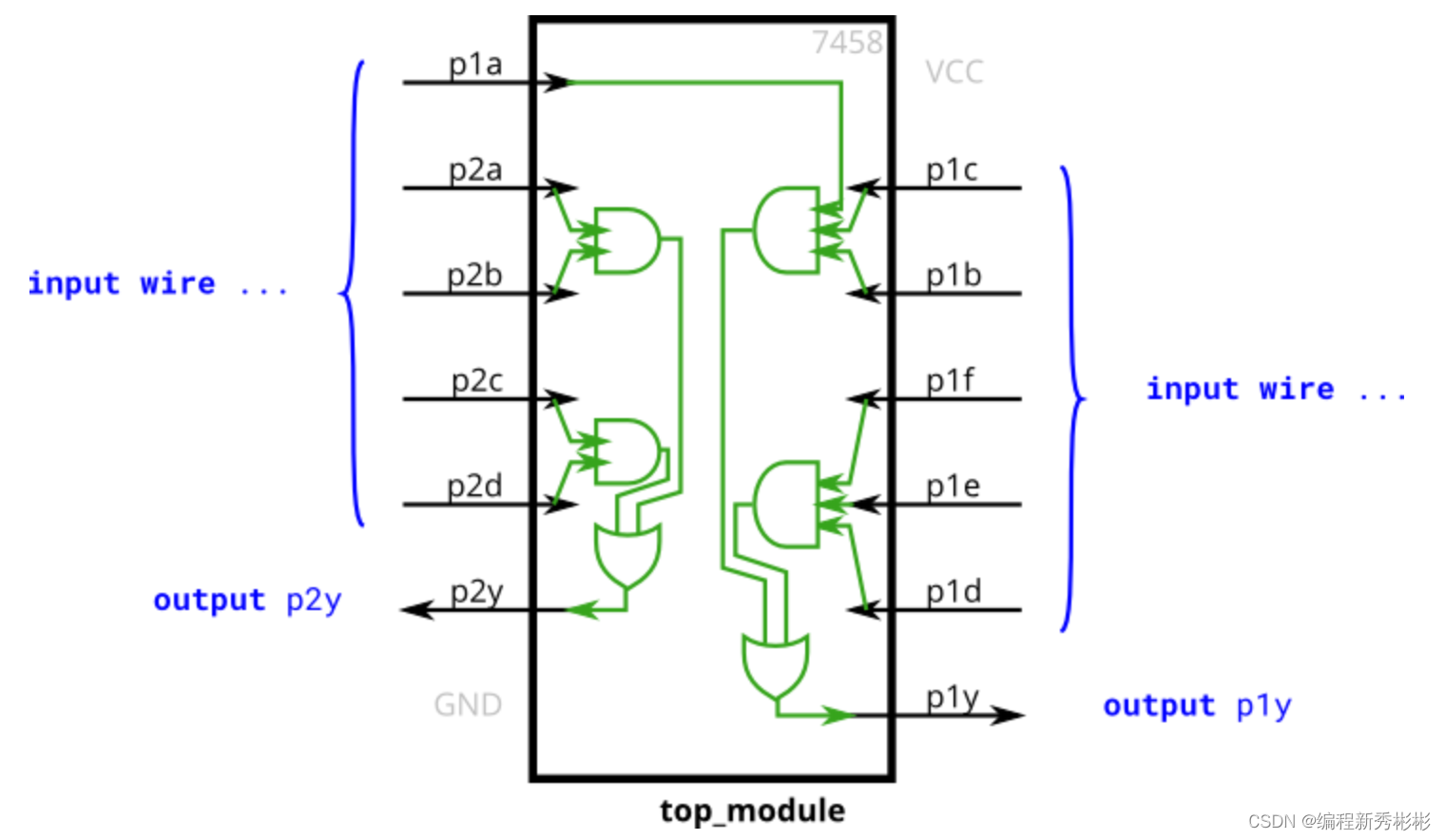

1.8 7458 chip

7458 是一款具有四个 AND 门和两个 OR 门的芯片。

创建与 7458 芯片具有相同功能的模块。它有 10 个输入和 2 个输出。可以选择使用语句来驱动每根输出导线,也可以选择声明 (四) 根导线用作中间信号,其中每根内部导线由其中一个 AND 门的输出驱动。

module top_module (

input p1a, p1b, p1c, p1d, p1e, p1f,

output p1y,

input p2a, p2b, p2c, p2d,

output p2y );

assign p1y=(p1a & p1b & p1c)|(p1d & p1e & p1f);

assign p2y=(p2a & p2b)|(p2c & p2d);

endmodule