目录

大家好,这里是程序员

杰克

。一名平平无奇的嵌入式软件工程师。

对于学习Xilinx FPGA(ZYNQ)而言,官方提供的很多IP核都有使用AXI总线,用于ARM核和FPGA的高速数据交互。因此学习AXI总线是必不可少的。而AXI协议是AMBA总线架构的一部分内容。基于此,本系列推文开始总结与分享AMBA总线架构的AXI部分内容。

下面正式进入本章推送的内容。

01 AXI协议简介

AXI(Advanced eXtensible Interface)协议是ARM 公司推出的总线架构AMBA(Advanced Microcontroller Bus Architecture)的一部分内容。其支持high-performance、high-frequency的系统设计,用于Manager和Subordinate组件间的通讯。

AXI协议特性

-

适用于high-bandwidth和low-latency的设计.

- 无需复杂的brideges便可实现high-frequency操作.

- 适用于高延迟的初始化访问接口的memory controllers

- 向后兼容AHB和APB接口

AXI协议传输特性

-

单独的地址/控制和数据通道

-

支持字节不对齐的数据传输(通过Byte strobes[字节选通])

-

支持brust[突发]传输(仅发送起始地址)

-

独立的write和read data通道,可提供低花销的DMA接口

-

支持无序事务执行

02 AXI协议架构

AXI协议架构

AXI协议基于事务的方式定义了5个独立的通道,通道名称以及信号开头缩写如下:

-

写请求通道Write request(信号开头缩写:AW)

-

写数据通道Write data(信号开头缩写:W)

-

写响应通道Write response(信号开头缩写:B)

-

读响应通道Read request(信号开头缩写:AR)

-

读数据通道Read data(信号开头缩写:R)

数据在Manager和Subordinate间传输通过以下方式:

- Manager通过write data通道传输数据给Subordinate(write transaction)

- Manager通过read data通道从Subordinate读取数据(read transaction)

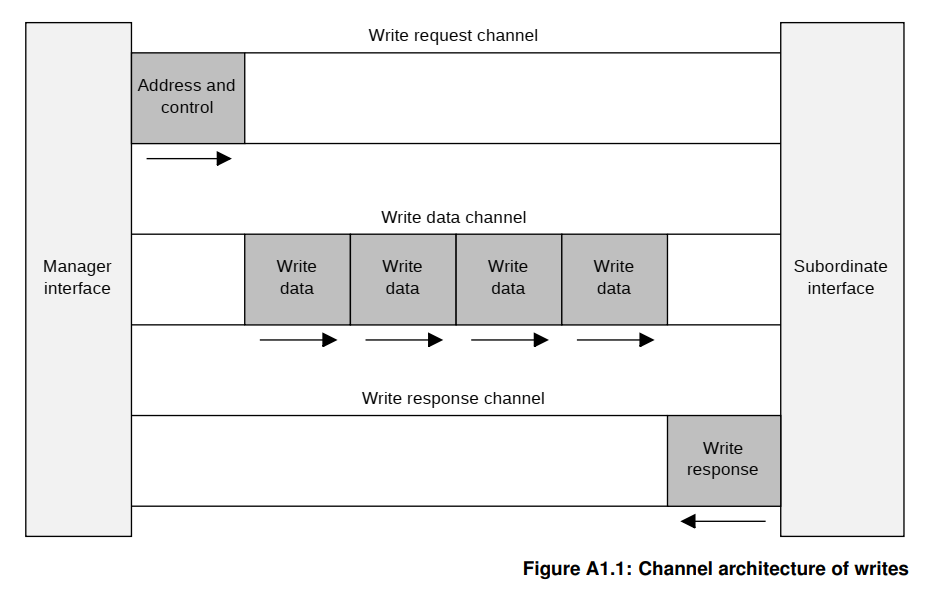

write transaction(写传输)

写传输事务使用write request、write data、write response通道,写操作如下:

- Master主机对write request通道写入地址和控制

- Master主机向write data通道写入数据

- Slave从机向write response通道写入响应信息.

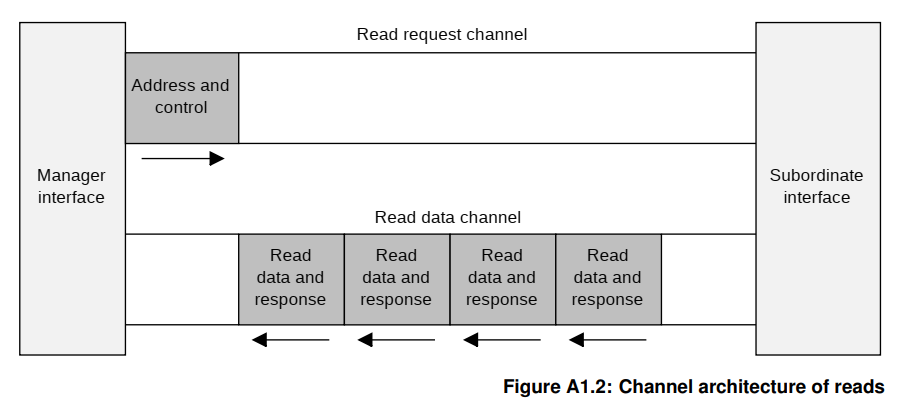

read tramsaction(读传输)

读传输事务使用read request、read data通道,读操作如下:

- Master主机对read request通道写入地址和控制.

- Slave从机向read data通道写入数据,返回给Master.

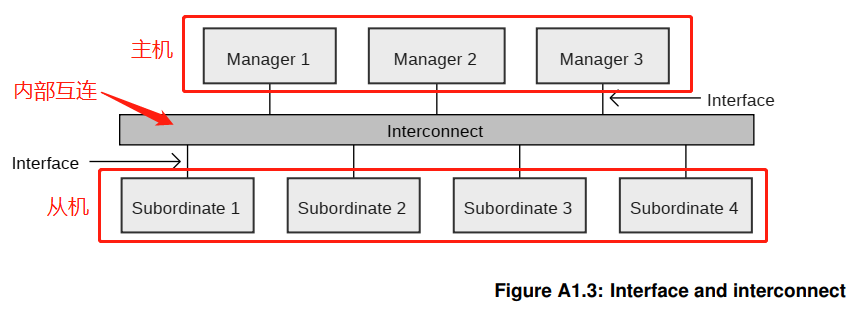

Interface and interconnect

典型的互连系统由多个Manager和Subordinate组成,通过某种形式内部互连在一起。典型互连图如下图所示:

AXI协议提供了单独的接口定义在以下三种互连之间,其支持实现多种不同的互连,三种互连如下:

- Manager和interconnect之间

- Subordinate和interconnect之间

- Manager和Subordinate之间

典型的AXI系统拓扑

大多数的系统使用如下拓扑结构:

- 共享request通道和data通道

- 共享request通道和多个data通道

- 多层拓扑,有多个request通道和多个data通道

在大多数系统中,request通道的带宽需求明显小于data通道的带宽需求。通过使用“共享request通道和多个data通道”的方式以支持并行数据传输,这样可以在系统性能和互连复杂度之间实现良好的平衡。

03 文章总结

本篇推送主要是对AXI总线的协议、协议架构、内部互连和接口模式、典型的拓扑结构进行了介绍。主要是对AXI总线的协议架构、互连模式有个大体的了解,以便后续对接口信号、具体的互连拓扑打下基础。