问题描述:

因项目需求使用STM32F407系类,之前只使用过STM32F103系列,纯属小白一只。

使用的是原子哥的例程,板子是某宝淘的,价格实在便宜才下手的。

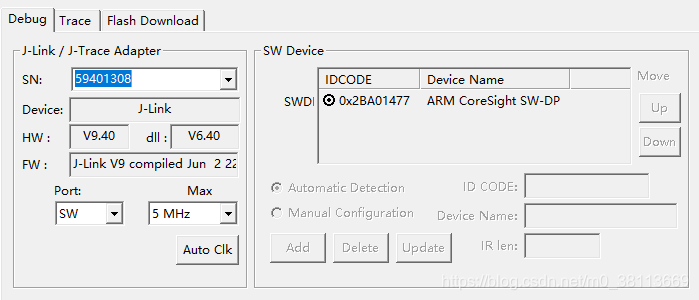

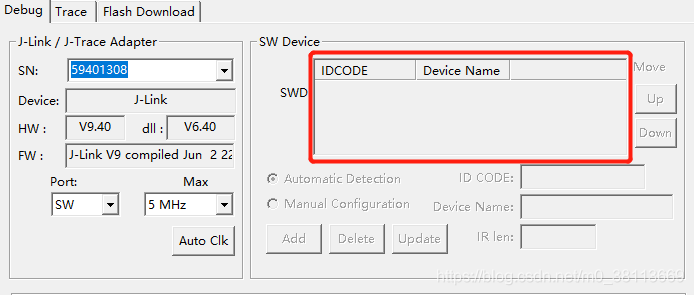

前期准备工作全部到位,使用J-Link烧写程序,程序一烧写进去,

J-Link就消失了,本来LED灯还在闪烁烧写进去后就不闪了,越想越奇怪。一开始怀疑是程序版本问题,这次使用的HAL库开发版本,又去找了一个不带HAL库开发的版本进行测试。效果是一样的,而且每次程序烧写经去后J-Link还失效了,痛苦啊。

让J-Link恢复正常使用:

先需要解决J-Link让它恢复正常,怎么让J-Link可以正常使用。

程序问题导致整个片子死机,拔电源无法恢复,说明之前的程序还在里面作祟,只能把程序删除干净。

mcuisp软件下载:链接:

http://www.mcuisp.com/chinese%20mcuisp%20web/ruanjianxiazai-chinese.htm

.

***需要注意:***J-link的BOOT0是需要接地的,系统的存储器BOOT1需要接高电平。

删除内部程序后J-Link恢复正常。

STM32的启动模式详解:

链接:

https://blog.csdn.net/c12345423/article/details/52809527

.

发现问题并解决问题:

在板子上找了半天发现晶振是25Mhz的,原子哥板子上的晶振都是8Mhz的,估计晶振频率不对导致的整块板子瘫痪的。把程序上面的参数修改一下:

这个是库版本的,下面展示一些

内联代码片

。

stm32f4xx.h文件

#if !defined (HSE_VALUE)

#define HSE_VALUE ((uint32_t)25000000) /*!< Value of the External oscillator in Hz */

//HSE外部晶振

#endif /* HSE_VALUE */

system_stm32f4xx.c文件

#if defined (STM32F40_41xxx) || defined (STM32F427_437xx) || defined (STM32F429_439xx) || defined (STM32F401xx)

/* PLL_VCO = (HSE_VALUE or HSI_VALUE / PLL_M) * PLL_N */

#define PLL_M 25

需要修改 HSE_VALUE及PLL_M这两个参数。

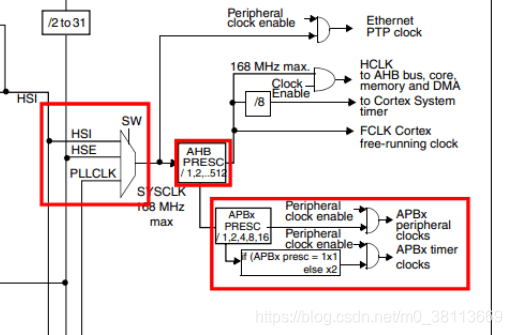

HSE(外部高速晶振),板子焊接8Mhz的晶振,那么HSE = 8Mhz,若焊接25Mhz,则HSE = 25Mhz。

HSI(内部高速晶振),芯片自带晶振,由芯片型号决定,STM32F407的HSI为16Mhz。

PLL(锁相环倍频),将HSE或HSI的频率放大,最大可以放大168Mhz。

STM32F407的时钟配置详见:

链接:

https://blog.csdn.net/husterxmh/article/details/52372403

.

下面是HAL库版本的修改:

main.c 初始化

// Stm32_Clock_Init(u32 plln,u32 pllm,u32 pllp,u32 pllq)

//plln:主PLL倍频系数(PLL倍频),取值范围:64~432.

//pllm:主PLL和音频PLL分频系数(PLL之前的分频),取值范围:2~63.

//pllp:系统时钟的主PLL分频系数(PLL之后的分频),取值范围:2,4,6,8.(仅限这4个值!)

//pllq:USB/SDIO/随机数产生器等的主PLL分频系数(PLL之后的分频),取值范围:2~15.

Stm32_Clock_Init(336,25,2,7); //设置时钟,168Mhz

stm32f4xx_hal_conf.h

#if !defined (HSE_VALUE)

#define HSE_VALUE (25000000U) /*!< Value of the External oscillator in Hz */

#endif /* HSE_VALUE */

STM32F407的晶振计算公式:

PLL_VCO = (HSE_VALUE or HSI_VALUE / PLL_M) * PLL_N

SYSCLK=PLL_VCO/PLL_P

USB OTG FS, SDIO and RNG Clock = PLL_VCO / PLLQ

PLL_M:PLL VCO的输入时钟,范围1~2M

PLL_N:PLL VCO output clock between 192 and 432 MHz

PLL_P:PLL VCO 分频数,must be {2, 4, 6, or 8},此分频作为SYSCLK

PLLQ:OTG FS, SDIO and RNG的分频数,between 4 and 15 并且,如果使用USB OTG FS,那么此分频评论<=48MHZ