一、概述

1.分类

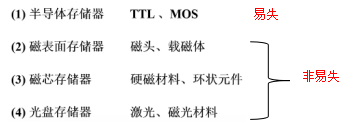

按存储介质分类

:

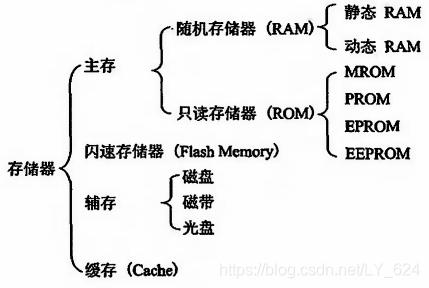

按存取方式分类

:

1)随机存储器(Random Access Memory,RAM):可读可写的存储器,可随机存取,存取时间与存储单元位置无关。

又分为静态RAM(以触发器原理寄存信息)和动态RAM(以电容充放电原理寄存信息)。

2)只读存储器(Read Only Memory,ROM):能读不能写。包括掩模型只读存储器(Masked ROM,MROM)、可编程只读存储器(Programmable ROM,PROM)、可擦除可编程只读存储器(Erasable PROM,EPROM)、用电可擦除可编程只读存储器(Electrically EPROM,EEPROM)。

3)串行访问存储器:磁盘、磁带等。

按在计算机中的作用分类:

分为:主存、辅存和缓存。

主存:可以和CPU直接交换信息;

辅存:主存的后备军,存放暂时不用的程序和数据,不能和CPU直接交换信息;

缓存:用在两部不同速度的部件中。

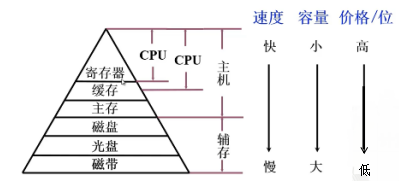

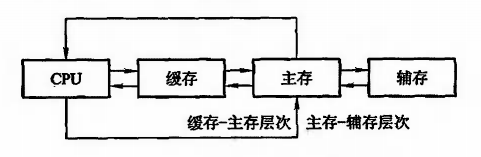

2.层次结构

存储系统层次结构主要体现在缓存-主存和主存-辅存这两个存储层次上。显然,CPU与主存、缓存能直接交换信息;缓存能直接和CPU、主存交换信息;主存可以与CPU、缓存、辅存交换信息。

缓存-主存主要用于解决CPU和主存速度不匹配问题。数据调动由硬件自动完成,对程序员透明。

主存-辅存主要解决存储系统容量问题。数据调动由硬件和操作系统共同完成。后来又形成了虚拟存储系统,虚实地址之间转换问题。

二、主存储器

1.基本组成

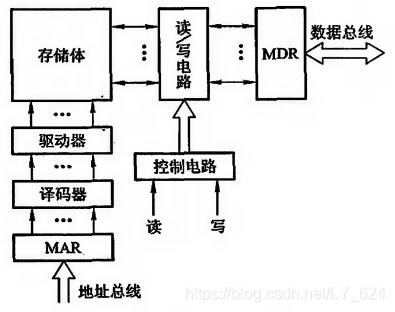

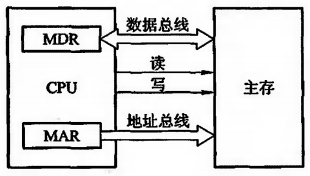

主存由存储体、MAR和MDR组成。

现代计算机的主存由半导体集成电路组成。驱动器、译码器和读写电路均制作在存储芯片内,而MAR和MDR制作在CPU芯片内。存储芯片和CPU芯片可通过总线连接。

当要从主存中读出某一信息字时,首先由CPU将该字地址送到MAR,经地址总线送到主存,然后发出读命令。主存接到读命令之后,得知需要将该地址单元的内容读出,便完成读操作,将该单元的内容读至数据总线上,至于该信息由MDR送到什么地方,由CPU决定。若要向主存存入一个信息字时,首先CPU将该字所在主存单元的地址经MAR送到地址总线,并将该信息字送入MDR,然后向主存发出写命令,主存接到写命令后,便将数据线上的信息写入到对应地址线指出的主存单元中。

2.主存中存储单元的分配

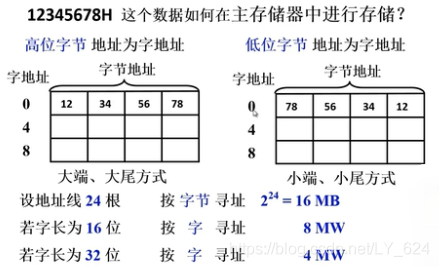

分为大端方式和小端方式。内存中按字节编址。一个字节占8位,即两个十六进制位,如12H。计算机中左边为高。

大端方式:高字节放在低地址内;小端方式:低字节放在低地址内。

上图中,24根地址线,按字节寻址范围为16M,因为2的20次方为1M,2的4次方为16,按字节寻址说明,一个地址有1B。

若一个字为2B,即16位,所以24根地址线,按字寻址范围为8M;若一个字为4B,即32位,则为4M。

注意:地址范围不能用字节(B)表示,上图中,后面的B和W为单位,表示寻址方式,即存储单位。

3.主存的技术指标

(1)存储容量:存放二进制代码的位数,即存储容量=存储单元个数*存储字长,单位为:bit,即位。

(2)存储速度:由存取时间和存取周期来表示的。

存取时间:又称为存储器的访问时间,指启动一次存储操作(读或写)到完成该操作所需的时间。分为读出和写入时间。分别指从接收到有效地址,到读出或写入的全部时间。

存取周期:指存储器进行连续两次独立的存储操作(如连续两次读操作)所需的最小间隔时间。通常存取周期大于存取时间。因为存取周期=存取时间+恢复时间。

三、半导体存储芯片

1.存储芯片的基本结构

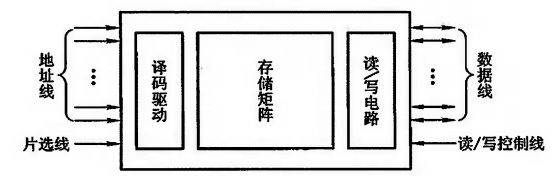

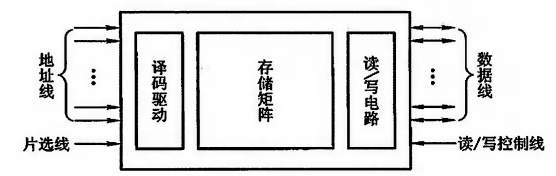

芯片内由具有记忆功能的存储矩阵、译码驱动电路和读/写电路等构成。其中:

地址线单向传输,数据线双向传输,共同决定存储芯片的容量。如地址线为10根,数据线为4根,则芯片容量为2的十次方*4=4K位。

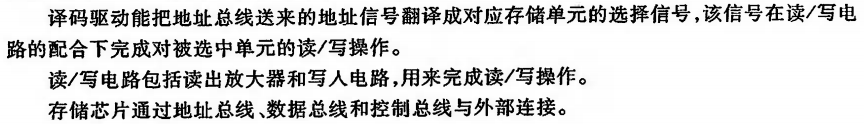

控制线有读/写控制线和片选线两种。读/写控制线决定芯片进行读/写操作,片选线用来选择存储芯片。读/写控制线可由一或两根组成。64K*8位的存储器可由32片16K*1位的存储芯片组成,其中选择8片16K*1位的芯片构成1个16K*8位的芯片,然后选4组就构成一个64K*8位的芯片,每读一个字时,选择8片,因为数据线为8位。片选信号决定选择的哪一组,比如地址为65535,由片选信号选择最后一组。

2.半导体存储芯片的译码驱动方式

(1)线选法

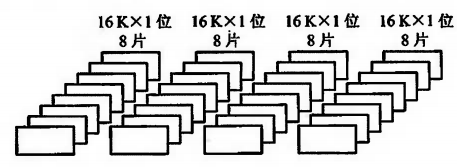

下图为2的四次方*8=16*8字节的存储芯片示意图。

如当地址线A3A2A1A0为1111时,则第15根线被选中,下面8位线便可直接读出或写入。

缺点:当1M的存储单元时,地址线需要20根,但字线需要2的20次方根,存储体内字线数目众多。

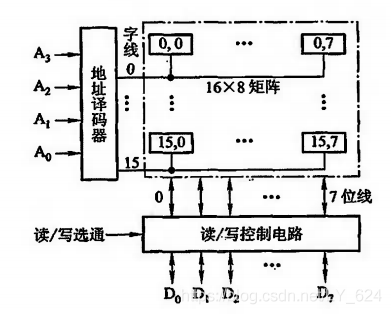

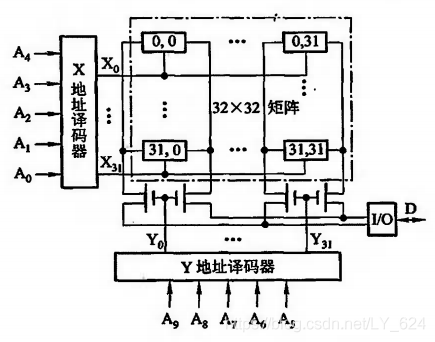

(2)重合法

下图为1K*1位冲重合法结构示意图。

X和Y两个方向各32根线,即可选择32*32矩阵中的任一位。如当地址线全为0时,译码输出X0和Y0有效,矩阵中第0行、第0列共同选中的那位即被选中。当欲构成1K*1字节的存储器时,用8片即可。