系列文章目录

文章目录

前言

使用最广泛而且面试最常考的AMBA总线,必须要进行一次梳理,记录自己的学习过程,希望大家看了也能自己理解~

一、APB

目前的APB是APB4,APB3中添加了PREADY、PSLVERR表明了signal ready,error信号, APB4添加了PPROT、PSTRB表明了protection signal支持安全与不安全的传输、第二个允许sparse data在写数据bus传输。

APB是

fixed two cycle access

。

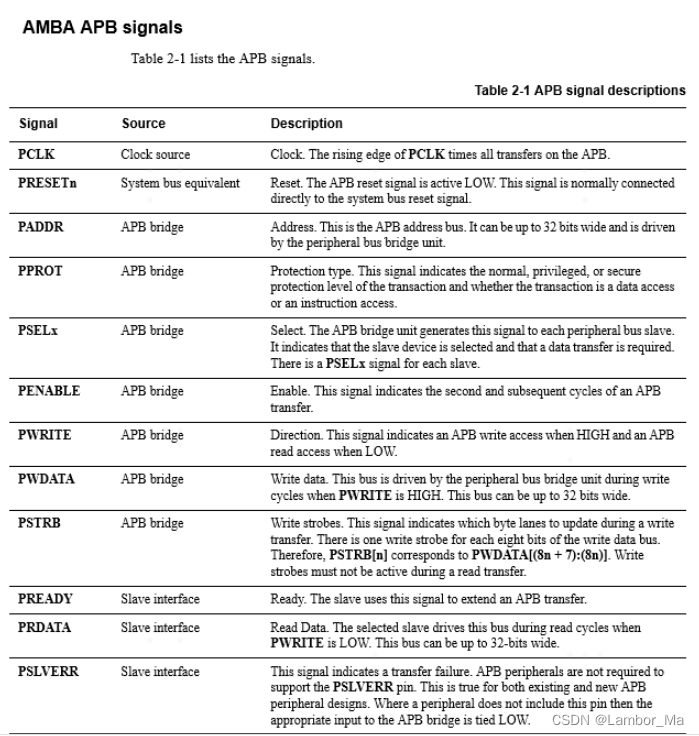

二、APB signals

中文傻瓜讲解的话

系统提供:

PCLK 时钟

PRESETn 系统reset

APB bridge提供:

PADDR : 地址线最多32bits 由外设提供,

PPROT : 表明这次传输是data access还是instruction access,等级分为normal、privileged or secure。

PSELx : 表明这个slave device被选择,data transfer需求。

PENABLE : 表明下一个和紧接着APB transfer,

PWRITE : 高的时候write 低的时候read,

PWDATA : 最高32bits,由外设提供当PWRITE是高的时候传输数据,

PSTRB: write data bus上每8bits有一个write strobes。PSTRB[n] 对应PWDATA[(8n+7):8n],在read的时候无效。

Slave interface提供:

PREADY:延续APB transfer,有等待的时候来控制。

PRDATA: 被选择的slave可以驱动写bus,最高32bits。

PSLVERR: 表示transfer失败,这个不是必须支持的。

Data buses: 有两个独立的data buses, 因为write和read都没有自己独立的handshake机制所以两种传输不能在同一时间发生。

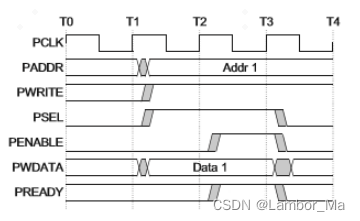

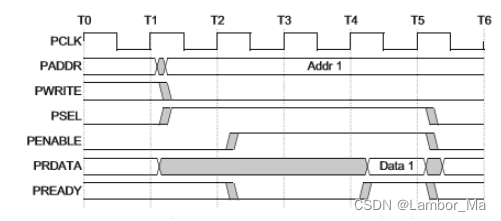

三、write transfers

no wait states

T1-T2这个叫Setup phase,T1的rising edge,有PADDR, PWRITE, PSEL,PWDATA,4个基础配置信号。

T2时刻是能PENABLE和PREADY,

PENABLE表明Access phase的开始

PREADY表明slave在下一个时刻传输完成

需要传输的data,PADDR和PWDATA直到T3都有效。

PENABLE和PSEL会在T3及传输完成的时候被拉低。如果下一个紧跟着的传输还是这个slave的话PSEL不会被拉低。

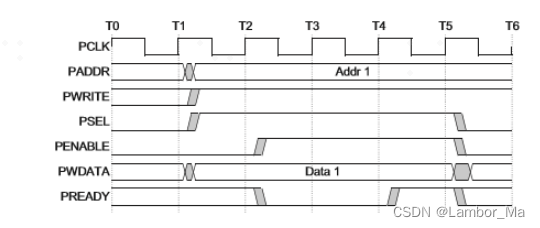

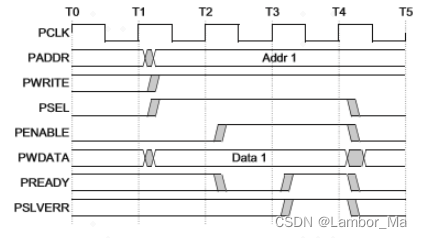

wait states

可以看到PENABLE和PREADY可以延长传输,PENABLE高的时候,PREADY调成low可以延长transfer到达的时刻。

建议address和write signals在transfer结束之后,不要立即改变知道下一个access开始,这样会降低功耗。

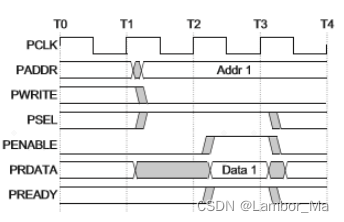

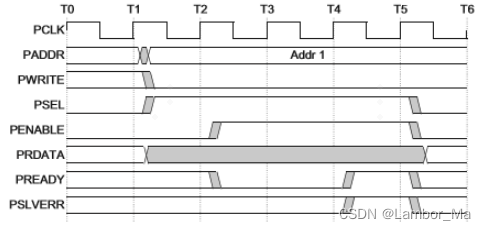

四、Read transfers

no wait states

可以看到这个也是两个周期access,其他的状态和write类似,只是read data的提供必须要在read transfer结束之前。

wait states

可以看到通过PREADY添加了2个空闲周期,PREADY有效的那个时刻数据被成功读出去。

五、Error response

write error

PSLVERR表明是否有error conditions,它在最后一个周期有效。

PSLVERR存在并不代表在写过程中外设的寄存器没有被更新,它是会被更新的。同样在读过程中,外设也会有读数据只是是非有效数据。而且这个PSLVERR并不是apb外设必须有的端口。

read error

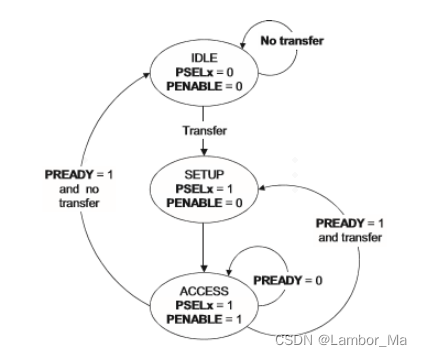

六、operating states

根据对读写操作的分析,APB的states转换很好理解,

即在Setup阶段的时候开始使能enable,

在Access阶段如果PREADY为0即上文中的有等待的时间,如果PREADY为1即在下个上升沿(可以理解为PREADY有效的时刻)完成传输,

如果还有数据要穿要满足2个周期传一次的机制返回到Setup阶段,如果没有数据要传即回到idle状态。