一.基本知识

一.基本知识

1.1 计算机信息

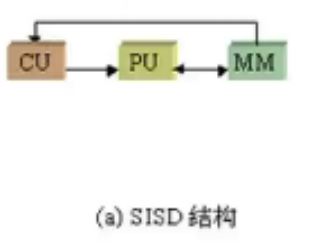

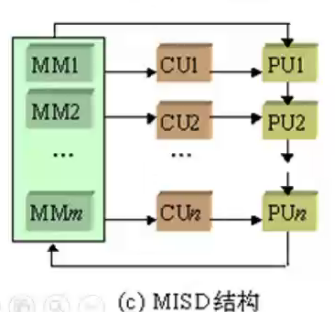

- 指令流:从存储器流入控制器,控制计算机

- 数据流:从输入流入存储器,再流入执行器,运算结果流入存储器或输出设备。

- CU:控制部件 PU:执行部件 MM:存储器

单指令单数据 |

单指令多数据 |

多指令单数据 |

多指令多数据 |

1.2 计算机硬件的主要技术指标

- 机器字长:CPU一次处理数据位数

- 存储容量:存储单元个数*存储字长

- 运算速度:不同的指令运行的时间以及该指令占全部操作的百分比

1.3 计算机硬件

以运算器为中心 |

以总线为中心 |

- 中央处理器(CPU):计算机中的核心部件,它执行程序中的指令。它具有加法、测试和控制其他部件的功能。

- 主存储器:计算机的一个组成部分,运行态的程序和相关数据置于其中。

- 控制器:处理器中根据程序的指令指示运算器、存储器和I/O设备做什么的部件。

- 嵌入式系统:嵌入在其他设备中的计算机,运行设计好的应用程序实现相应功能。

- 集成电路:在一个芯片中集成几十万到上百万个晶体管的工艺。

- 操作系统:管理计算机中的资源以便程序在其中运行的程序。

- 编译器:将高级语言翻译成机器语言的程序。

- 汇编器:将指令从助记符号的形式翻译成二进制码的程序。

- 控制器:计算机硬件与其底层软件的特定连接纽带。

1.4 三极管:

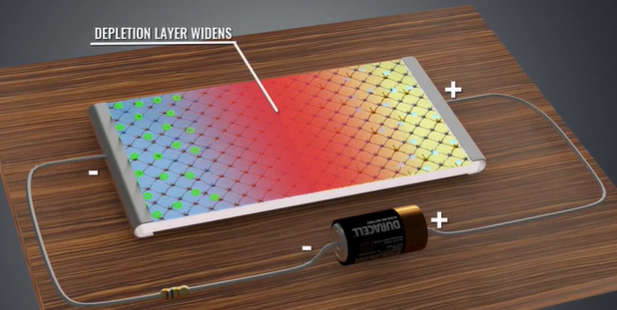

- P极中存在空穴,N极中的电子有靠近P极空穴的趋势,PN结的连通是由N极的电子迁往P极空穴而实现的。下图显示了反向截止的情况。

PN结反向连通示意图 |

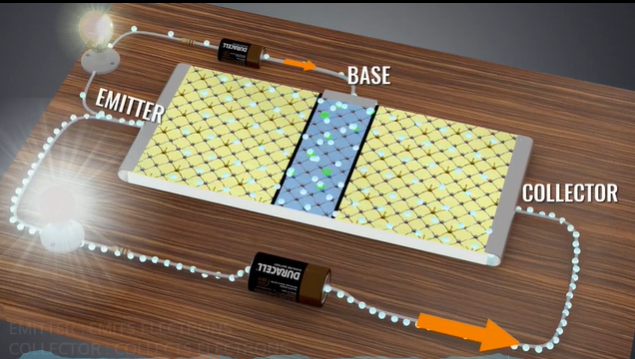

三极管原理图 |

-

C极始终有着较大的电压,但是只有B极电压达到一定的值,令BE电势差达到截止电压,才能让导通(部分导通),导通前称为截止状态;但是B极连接在P极上,比较小,大部分电流都经过C,称为放大状态;随着B的电压增大,越来越多的电子被激活,则电流不断扩大,当所有电子都被带动,则B改变也无效,称为饱和状态(完全导通)。

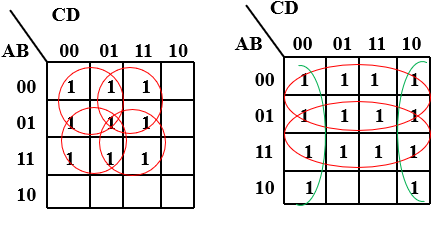

1.5 卡诺图

- 行列都只能相差一个变量

- 画最大的圈,可以透过边界,可以重复,但是必须是2的次方

- 无关项d,可用可不用(取决于画图)

四变量卡诺图 |

五变量卡诺图 |

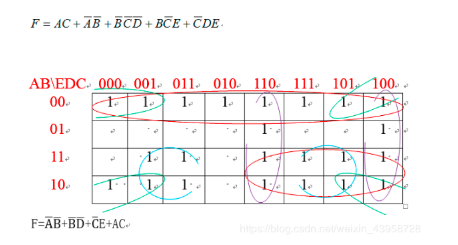

五变量卡诺图举例 |

PS. 真值表中X表示可为0,也可为1,无关项

1.6 逻辑表达式化简

-

分配率:A+BC=(A+B)(A+C)

-

吸收率:A+AB=A

-

第二吸收率:A+(|A)B=A+B [|A是非A]

-

包含率(2-13中的1化开的思想):

1.7 输入输出连接:

- 允许输入相连,但不许输出相连(OC门,三态门除外)

1.8 基本电路部件

-

加法器

(1)一位全加器:存在两个输入以及进位

(2)四位二进制加法器:通过四个一位加法器组合,但是需要等待前一个阶段的进位

(3)四位超前进位加法器:不使用进位,直接代入,则只需要第一个进位,速度更快

(4)四位并行进位加法器:通过更加复杂的结构,多输入实现并行

-

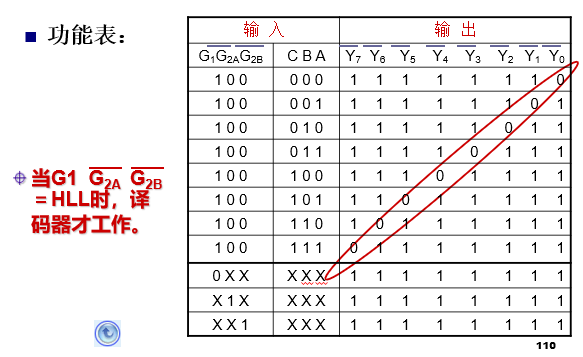

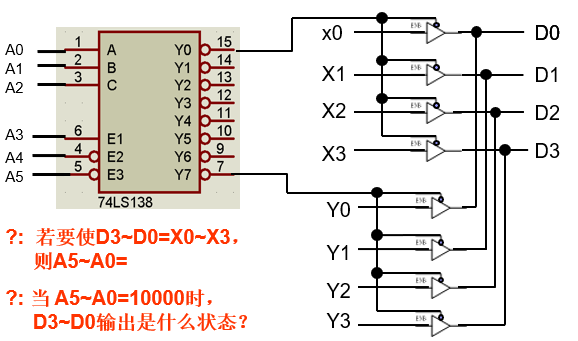

译码器

(1)把n位输入编码翻译成2的n次方个输出控制,一个编码对应一个输出,输出是设定好的

(2)存在控制端,使能情况下才能有输出

(3)低电平有效,输出为Y的反(为0)

3-8译码器真值表(存在译码条件) |

应用 |

-

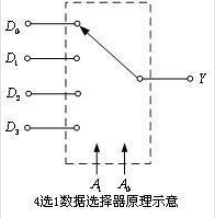

多路选择器:

(1)只有一个输出,由s0,s1决定输出A,B,C,D的哪个,输出是输入决定的

四选一电路 |

真值表 |

译码器和多路选择器的区别:译码器是翻译后输出自己的结果,而多路选择器是选择输入后输出。

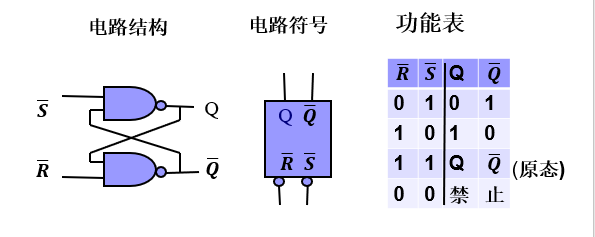

- R-S触发器(Reset,Set):利用电平进行触发(只有当电平改变时数据才会改变)

触发器示意图 |

- D触发器:主要针对模型的上升下降沿触发,当RS都不起作用才有效

D触发器示意图

R-S触发器和D触发器的区别:R-S是电平触发,而D是是中上升沿触发

- 锁存器:当输入一定的数据之后,将E调成0,就能锁住数据

-

寄存器:用来暂时存放数据

(1)右移寄存器:将高位的输出和低位的输入相连

(2)计数器:前一个的输出作为下一个的时钟

-

缓冲器:输入不直接传入,使用三态门,在需要的时候再传入

二.信息编码与数据表示

二.信息编码与数据表示

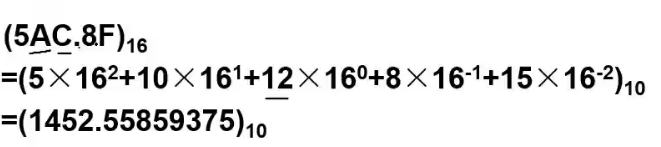

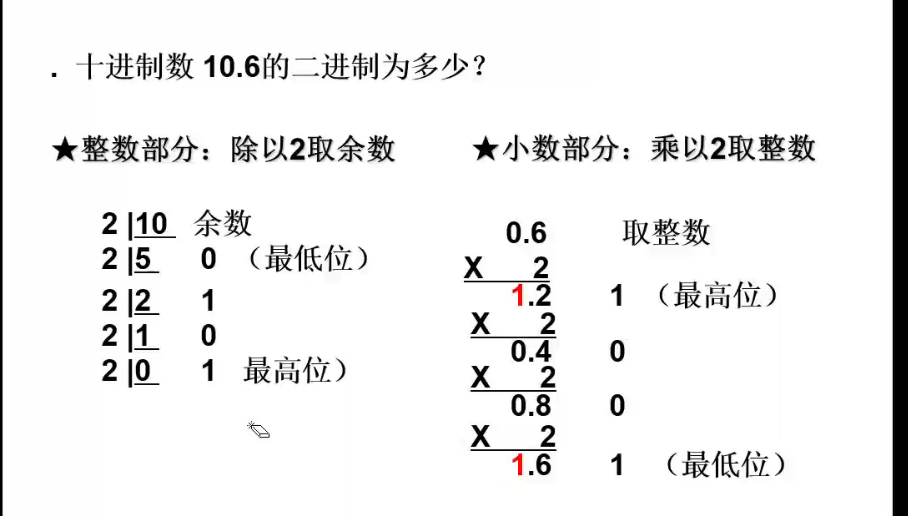

2.1 进制

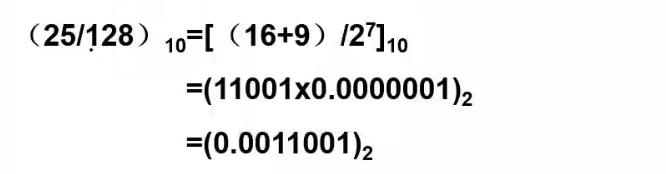

- 十进制转换成别的进制,小数整数要分开处理,转换成二进制,乘2取高位

3-8译码器真值表(存在译码条件) |

应用 |

应用 |

-

编码制度:可分为加权与非加权

- C(12) 表示正,D(13)表示负

- 符号位占半个字节,一个字节两个十位数

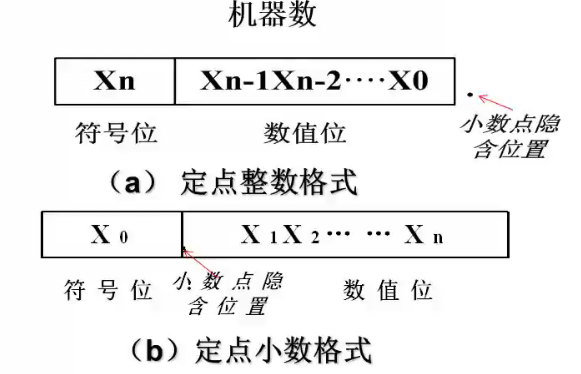

2.2 机器数与真值

- 机器数:n+1位(将符号代码化)

- 真值:机器数的真实值

定点数 |

浮点数 |

-浮点数表示

(1)非规格化表示:以2为底的科学计数法*1.**

数符+尾数(作为系数的小数项),阶符+阶码(其中的127是最高位Es产生的)

(2)规格化表达:原码的系数必须0.5≤|M|≤1;对于补码,必须Ms与M1不同

三.运算方法和运算器

三.运算方法和运算器

3.1 补码

- 两个补码相加,等于相加取补码(减法相同)

- 正溢出:两个正数相加—负溢出

-

溢出的表现

1.数值的最高位和符号位只有一个进位;

2.使用双符号位,11表示正,00表示负,变成异号则溢出(10负溢出,01正溢出) -

补码加减法计算器

3.2 移码

- 相加的移码=移码与补码的和

- 溢出的判断:双符号的最高符号位为1则溢出,低符号位为0,上溢

3.3 移位

- 逻辑移位:无符号数

-

算术移位:符号位不变

(1)右移都补零,可能会溢出

(2)左移针对情况,原码补零,补码符号位 反码左移正数补零,负数补一;右移符号位来补

3.4 总结(原码,反码,补码,移码)

3.5 乘法

-

原码乘法:

(1)同10进制乘法:按位直接乘,结合右移

(2)原码一位乘法:符号位单独计算,取两者的绝对值,将Y的倒数几位依次乘上|x|,并右移(先得到的是后面的y与x相乘的结果)。

|

|

|

-

补码乘法

(1)校正法:符号位单独处理,取小数部分,类似原码一位乘法,最后根据符号位是否为负数,决定要不要加上[-x]补

|

|

(2) Booth算法 :类似补码移位乘法,但本次要带上符号位(几位加几次),最后一位先补零,然后逆序取两位判断应该加啥,11/00不加…

|

|

3.6 除法

-

原码除法

(1)手工除法

(2)恢复余数算法:除法分成余数(R)和商(Q),余数的符号取决于被除数的符号,商的符号取决于两者。重复(1)-(3)

|

|

(3)不恢复余数算法

|

|

3.7 定点数运算器的组成与结构

-

标志寄存器

3.8 浮点数运算器的组成与结构

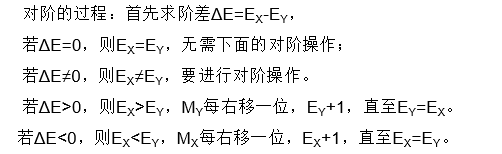

对阶(小阶靠向大阶),尾数计算(具体方法选择),规格化,舍入

-

加减

(1)0操作数检查

(2)对阶:小阶向大阶(避免左移)

|

(3)尾数加减

(4)规格化:

若尾数溢出,则右规一位(只能一次)

若尾数过小,则需要左规

(5)舍入:截断,0舍1入,末位恒置1

- 乘除(尾数只能左规一位)

|

版权声明:本文为weixin_43958728原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接和本声明。