【VHDL】【作业】2 基于CASE语句的4选1多路选择器表述

文章目录

前言

记录学习的过程,顺便期末复习一下。

1、八选一多路选择器

LIBRARY IEEE; --引用库

USE IEEE.STD_LOGIC_1164.ALL; --调用库中的程序包

ENTITY MUX81A IS --实例化一个 名为 MUX81A 的实体

PORT ( a, b, c, d, e, f, g, h, s0, s1, s2 : IN STD_LOGIC; y : OUT STD_LOGIC);--定义其各端口

END ENTITY MUX81A;

ARCHITECTURE BHV OF MUX81A IS

SIGNAL S : STD_LOGIC_VECTOR (2 DOWNTO 0);

BEGIN

S <= s2 & s1 & s0 ; -- 并置s2、s1与s0

PROCESS(s2,s1,s0) BEGIN --敏感信号表中可以方s1 s0,也可以直接放s

CASE (S) IS

WHEN "000" => y<=a; -- "=>"是格式符号 "<="是赋值符号

WHEN "001" => y<=b;

WHEN "010" => y<=c;

WHEN "011" => y<=d;

WHEN "100" => y<=e;

WHEN "101" => y<=f;

WHEN "110" => y<=g;

WHEN "111" => y<=h;

WHEN OTHERS => NULL;

END CASE;

END PROCESS;

END BHV;

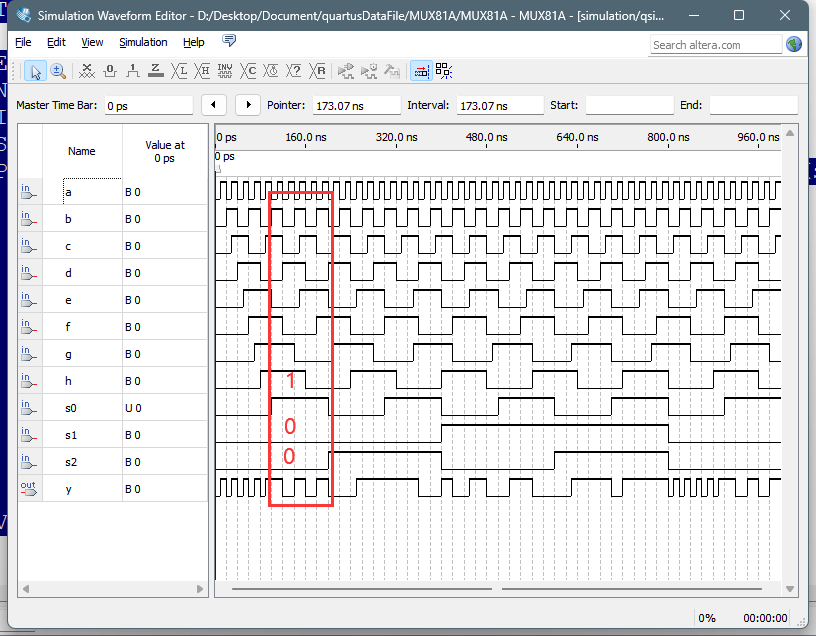

仿真波形

S

对应的是

001

对应选择输出B的波形。

2、半减器

a.什么是半减器?

半减器用于计算

2Bit 的 Xi(被减数)

和

Yi(减数)

的减法,

输出结果

Di(半减差)

和

Bo(Borrow output 高位的借位输出信号)

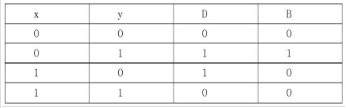

b.真值表

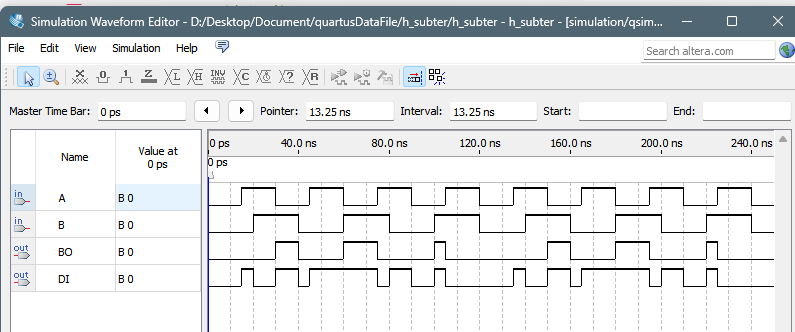

c.仿真时序图

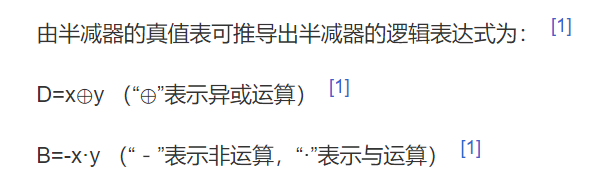

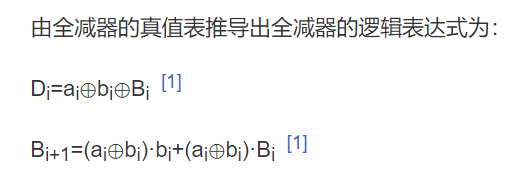

d.逻辑表达式

xor

表示

异或

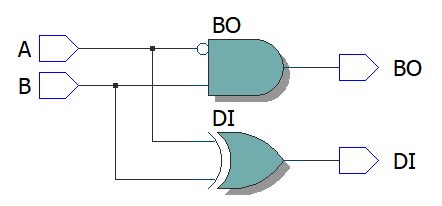

e.门电路图

f.VHDL代码

LIBRARY IEEE;--引用库

USE IEEE.STD_LOGIC_1164.ALL;--调用库中的函数

ENTITY h_subter IS--实例化一个半减器

PORT(

A : IN STD_LOGIC;

B : IN STD_LOGIC;

DI : OUT STD_LOGIC;--结果位

BO : OUT STD_LOGIC --借位端

);

END ENTITY h_subter ;--结束实例化

ARCHITECTURE fh1 of h_subter IS --声明一个半减器结构体

BEGIN

DI <= A XOR B ; --A 异或 B

BO <= NOT A AND B;-- 非A 与 B

END ARCHITECTURE fh1;--结束结构体的声明

3、全减器

a.什么是全减器?

全减器不同于半减器在于,全减器输入来自低位的借位

Bi(Borrow input)

,另外两个输入

Xi,Yi

,输出为

Di

和向高位的借位

Bo

b.真值表

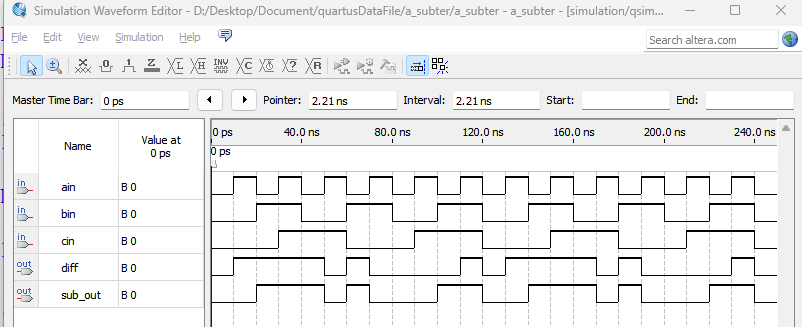

Xi

=

ain

,

Yi

=

bin

,

Bi

=

cin

,

Di

=

diff

,

Bo

=

sub_out

这样还看不懂的话,可以用纸笔演算一下。

c.仿真时序图

d.逻辑表达式

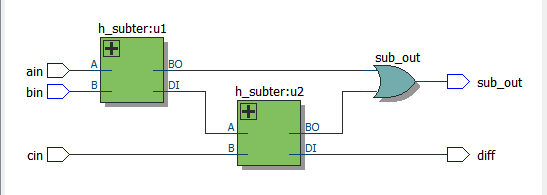

e.门电路图

f.VHDL代码

LIBRARY IEEE; --全减器顶层设计描述

USE IEEE.STD_LOGIC_1164.ALL; --调用库函数中的程序包

ENTITY a_subter IS

PORT ( ain, bin, cin : IN STD_LOGIC;

diff, sub_out : OUT STD_LOGIC );

END ENTITY a_subter;

ARCHITECTURE fd1 OF a_subter IS

COMPONENT h_subter --调用半减器声明语句

PORT ( A, B : IN STD_LOGIC;

DI, BO : OUT STD_LOGIC );

END COMPONENT;

COMPONENT or2a --调用或门声明语句

PORT ( a, b : IN STD_LOGIC; c : OUT STD_LOGIC );

END COMPONENT;

SIGNAL net1, net2, net3 : STD_LOGIC; --定义3个信号作为内部的连接线(看电路图会更加清晰)

BEGIN

u1 : h_subter PORT MAP(A=>ain, B=>bin, DI=>net1, BO=>net2 );--例化语句

u2 : h_subter PORT MAP(A=>net1, B=>cin, DI=>diff, BO=>net3); --简写的语句

sub_out <= net2 or net3;

--u3 : or2a PORT MAP(a=>net2, b=>net3, c=>sub_out);

END ARCHITECTURE;

总结

1、

全减器

是包含低位借位的三个输入变量、两个输出变量的一位减法器,在半减器的基础上再加一个低位借位输入位。

2、

半减器

是只有两个输入变量、两个输出变量,无借位输入的一位减法器。

每天进步一点点 笔记仅供自学,用来回看复习,不一定适合你,如有错误请指出。