前言

版本:Vivado2019.1

平台:Xilinx ZCU102开发板

官方文档:

PG074

背景知识

工程搭建

计划搭建一个1lane的自回环测试工程,可以进行自发自收。

作者本人没有在Block Design中使用过Aurora IP,但是我看别人用过,有机会自己也捣鼓一下。

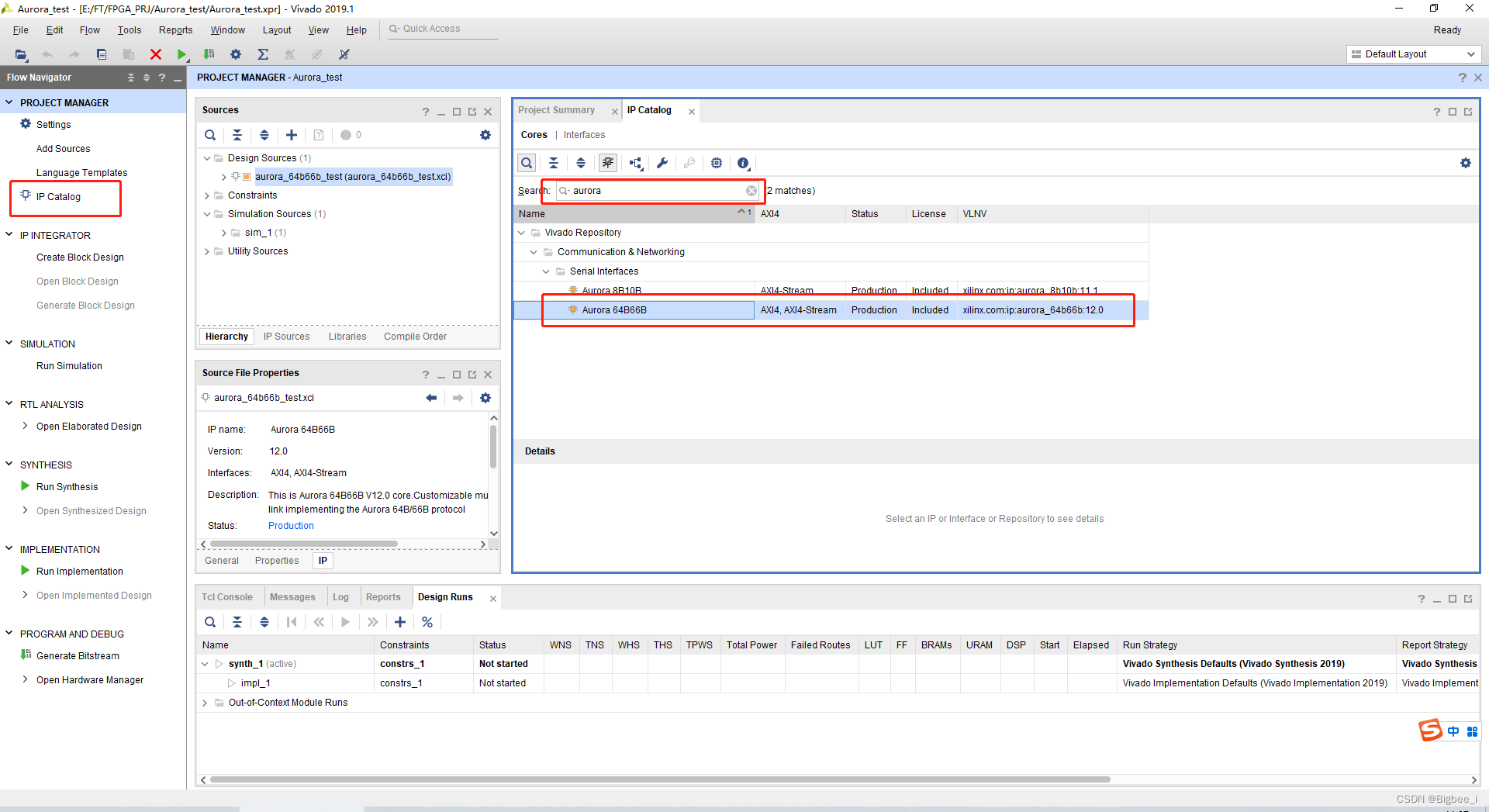

选择Aurora 64B/66B,双击打开

64B/66B 和 8B/10B 是算法的不同,8位信息使用10位数据进行传输,时钟也是从数据中直接恢复。很明显,64B/66B的传输效率会高很多。

参数设置按照需求,为了省事,我将Line Rate设置成了10Gbps,这样我的GT时钟和我IP的INIT时钟都能设置为156.25MHz。

-

GT Type 没得选只有GTH,差别可以看这篇博文

GTX/GTH/GTY/GTP/GTZ/GTM有什么区别?-张大侠

- Line Rate 选择10

- Column Used 排序方式,因为数据时并行传输的,在组合数据时要选择排序方式。

- Lanes 选1

- GT Quad 和 GT Lane默认

- GT Refclk和INIT clk都选择为156.25

- 下面的保持默认

- interface选Framing(数据帧格式),当然也可以选择Stream(数据流格式),interface选项决定的是IP与用户逻辑的接口类型,按照整体设计确定

设置玩参数后等综合完成生成example deign

代码分析

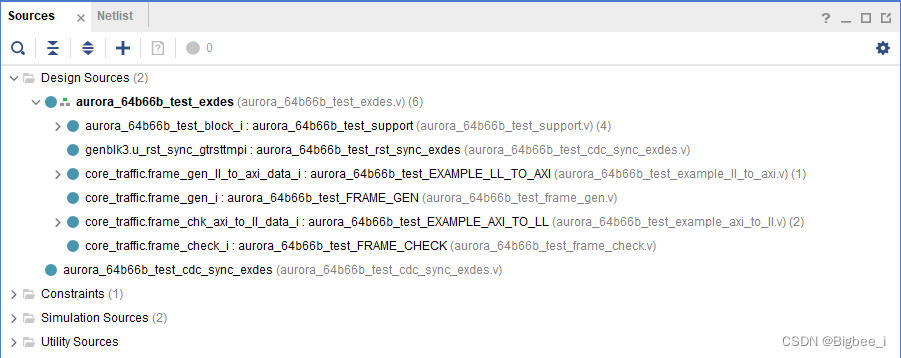

代码架构如下。在进行移植时下面四个core_traffic.frame文件都不需要被用到,但是在进行移植之前,可以跑一下仿真看看Aurora IP在工作时的一些行为。

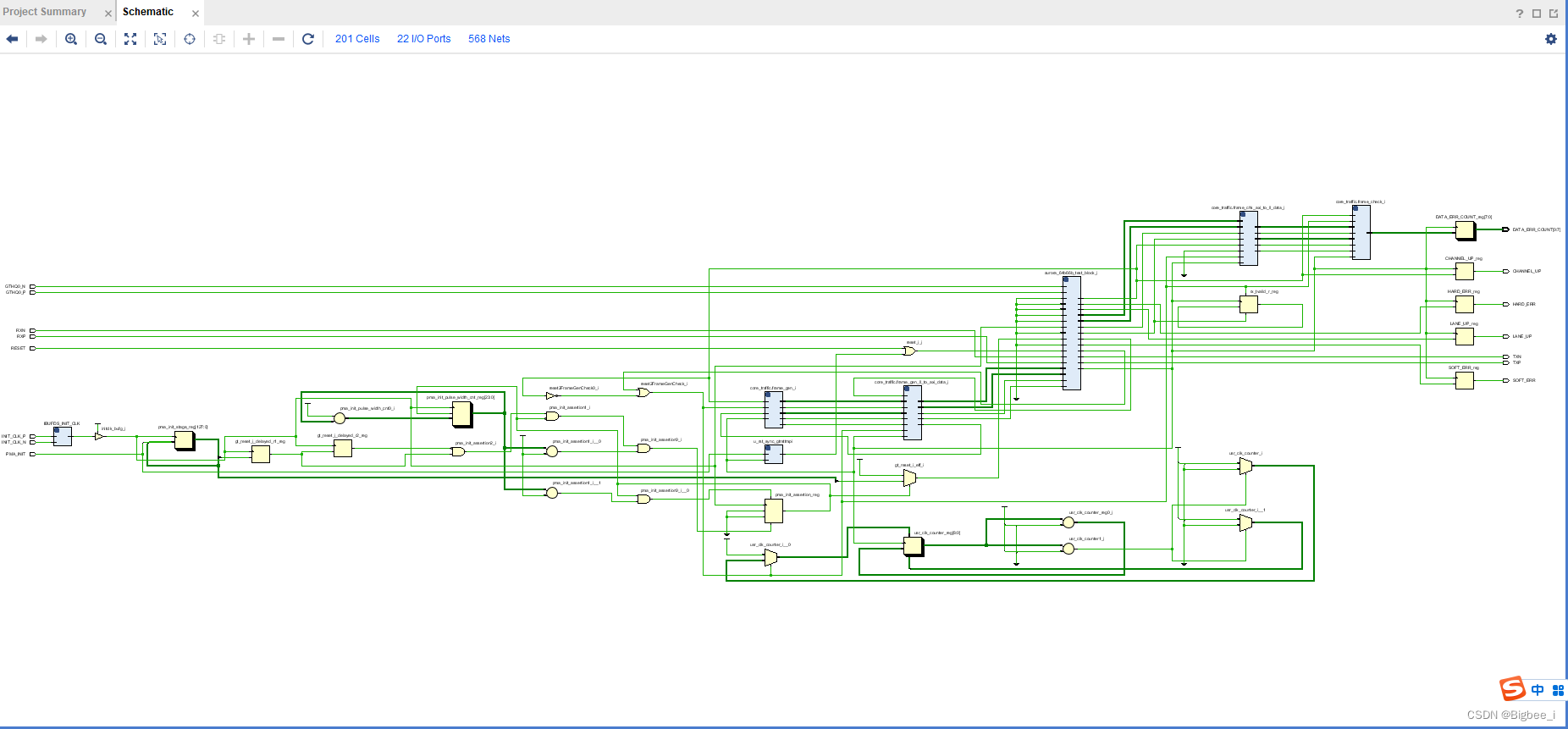

RLT图

注意事项

这里面有一个GT时钟的问题,在进行多lane的设计时,要注意有一个时钟只有一个,不能扩展。

版权声明:本文为liuhandd原创文章,遵循 CC 4.0 BY-SA 版权协议,转载请附上原文出处链接和本声明。