前言:最近再搞个PCIe的高速串行总线的项目,关于串行和并行数据的传输到底谁更快,分别有哪些优势和劣势呢等等一些问题现在做个整理,是对自己学习的一个记录,同时呢,也为刚刚想入门的或者对高速串行总线有些误解的(暂且说误解把 词穷呀 最近在看主持人大赛2019,,,,,,,,,汗颜),我下面首先从总线的技术方面说起,当然只是浅显的说一下,深了咱也不会

其次,PCIE的概念

最后,进行PCIe的数据传输实验

1 并行技术的简介

1 并行传输就是将Nbit数据以成组的形式同时(在一个时钟周期下)在不同的线路上传输。分组一般8bit 16bit等

那么为了数据能够正确的被接收端接收,每组(8bit或者16bit或者更大的数据位)数据必须在时钟上进行同步(源同步和系统同步),

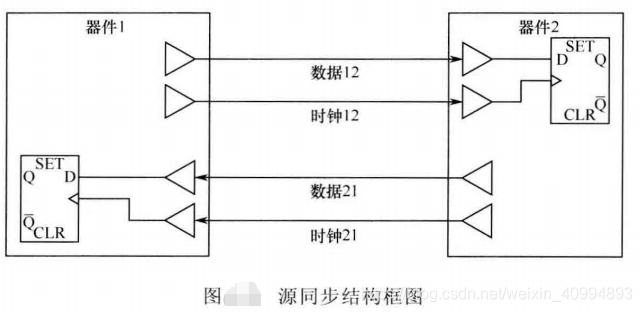

源同步:

发送端产生的数据和时钟保持一定的相位关系(clk和data都在发送端产生),并同时传输到接收端,接收端使用发送端的时钟作为采样时钟,对数据进行采样。在采样的过程中,只要保证接收端clk和data满足一定的建立时间/保持时间。数据一定能够正确接收。

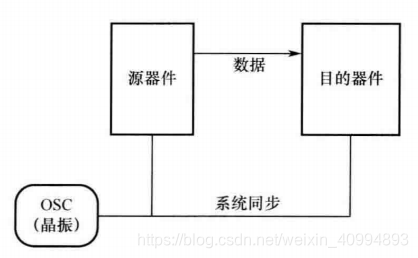

2 系统同步

传统的数据传输通常采用系统同步的方式进行传输,多个期间时使用同一个时钟进行系统同步,器件之间的数据传输时序关系以系统时钟作为参考,如图,这种方式使各个器件处于同步工作模式,但是器件之间的时延难以确定,当系统时钟的频率增加之后,数据接收接口同步电路难以实现,因此不适合高速数据传输。

上述两种方式,PCB Layout时数据线总是成组并排布线,线间距小,线之间存在较大的耦合,导致串扰问题严重,除了数据线和时钟线之外,并行总线还有很多的控制线,走线数目多且一般是单端信号传输,抗干扰能力差,数据不能同时到达,因此并行传输的时钟频率很难达到1GHz。

并行总线常用的接口找个图了解一下:

2 串行传输技术简介

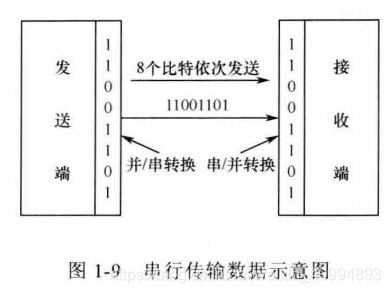

1 串行传输的原理

串行传输指的是发送方和接收方直接的数据在单根通信线上逐位顺序传送,每一位数据都占据一个固定时间,示意图如下,,时钟频率相同,并行当然比串行要快的多,这个可以理解吧,在低速情况下,并行结构绝对是一种非常高效的传输方式,但是当传输速度非常高,并行传输的致命性缺点就出现了。因为时钟在高速的情况下,因为每一位在传输线路上不可能严格的一致,并行传输的一个字节中的每个位不会同时到达接受端就被放大了。而串行传输一位一位传输就不会出现这个问题。串行的优势就出现了,串行因为不存在并行的这些问题,就可以工作在非常高的频率下,用频率的提升掩盖它的劣势。

在串行传输中,发送端和接收设备必须达到bit同步,发送设备和接收设备必须以同步时钟(这个是频率可以很大,不存在数据不能同时到达的问题,人家就1bit嘛)发送和接收数据必须以同步时钟发送和接收数据,在接收端才能正确的接收数据。衡量串行串行传输通道的频宽的重要指标是波特率,数据的个数/单位时间,举个例子把,每秒传输240个字符(1个起始位。1个停止位,8个数据位),波特率:240Bd,比特率=240*10=2400b/s,对串行接口,必须设置正确的波特率,不然 你懂的(是不是想到了串口,那就对了)

也列举几个串行接口协议的常用接口

串口和USB及IEEE1394

通过上面的讨论,简单介绍一下高速并行传输的瓶颈问题(也是抄来的 将就着看一下把)

1 时序同步问题

2 信号偏移

3 抗干扰能力

4设计复杂度和设计成本(线多呀!!!!!!!!)

串行传输的优势:

1 传输频率的提高是最大的优势,串行通信在

发送端

通过

数据编码技术把时钟信号嵌入到数据信号

中,在

接收端

使用

时钟恢复技术

,从

数据中提取同步时钟信号来恢复数据

,消除了传输线延迟导致的时序问题对速率的约束,实现单通道的数据传输速率10Gb/s以上。

2 使用差分信号,抑制共模噪声产生的影响,在相同驱动电压的驱动下,差分信号的摆幅是单端信号的两倍,那么发送端就能以更低的电压发送信号,不但降低了功耗并且还抑制了电磁干扰的影响,减少对外的电磁辐射,此外,此外,此外呀,差分信号模式一般采用恒定的电流驱动,这将保证驱动器电路在任何时刻保持不变,消除了信号同步翻转而产生的同步开关噪声问题哦。

3 线少了 你懂的的

4 使用点对点连接方式,避免并行总线的共享机制造成的总线利用率低的问题,通信链路利用率达到100%(听起来是不是很牛b),而且在点对点拓扑情况下,阻抗的匹配端接也非常简单,一般高速串行收发器都自带匹配,实现双端端接,进一步降低反射。

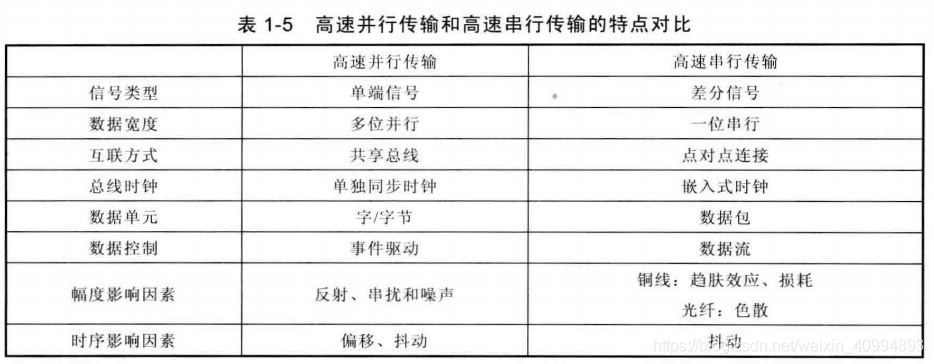

娘妈的 抄的手疼 贴个图

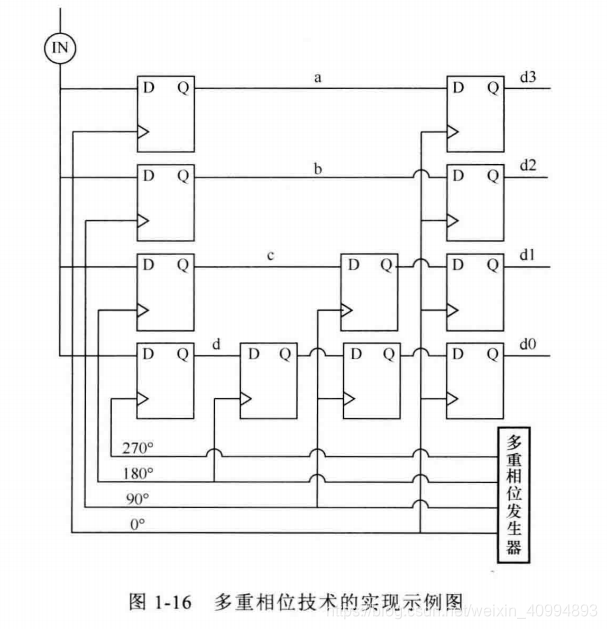

多重相位技术

这个多啰嗦几句 我也是刚学,如有错误,请指出

多重相位技术是实现高速串行I/O的通信技术之一,多重相位在时钟的不同相位对串行的数据流进行采样,将串行数据流转化为并行数据输出,从而实现 低速时钟处理高速时钟的的数据,如下示意图,由锁相环的多相时钟产生器输出4个相时钟信号,即在0°,90°,180°,270°上采样数据,最后由零相位时钟信号同步并行输出。采用多重相位提取电路。若输入的串行数据流比特率位x,则并行输出的数据流比特率为x / 4。

线路编码技术

https://wenku.baidu.com/view/c3280ec0b9f3f90f76c61b38.html参看一下

扰码传输技术

发送预加重技术

接收均衡技术

这几个技术以后用到再补充吧。。。。。。。。。。。。。。。。