第一次接触AXI 4 总线是在使用xilinx zynq的时候,当时用的时候一团雾水,现在雾水少了些,但还是有很多地方没有接触到。本文作为自己的总结,有任何问题,欢迎批评指正。

什么是AXI总线?

AXI 作为 ARM AMBA 微控制器总线的一部分,第一次出现在AMBA 3.0中。后面AMBA 4.0发布,AXI4出现了。

AXI 4总线和别的总线一样,都用来传输bits信息(包含了数据或者地址)。AXI4总线有三种类型,分别是AXI4、AXI4-Lite、AXI4-Stream。

AXI4 是一种高性能memory-mapped总线,AXI4-Lite是一只简单的、低通量的memory-mapped 总线,而 AXI4-Stream 可以传输高速数据流。从字面意思去理解,AXI4-Lite是AXI4的轻量版。这里保留了memory-mapped的写法,主要是为了与AXI4-Stream区分开。

memory-mapped 可以这样去理解,假设有master A , 和 slave B, A与B通过AXI4或者AXI4-Lite连接通讯,A可以把B这个外设看作A上的某个地址。当A向B传输数据时,就等同于A向这个地址传输数据。

AXI4-Stream与AXI4、AXI4-Lite不同, 它不需要地址通道。

AXI4 、 AXI4-Lite 、AXI4-Stream接口

AXI4 和 AXI4-Lite接口包含5个不同的通道:两个读通道和三个写通道。

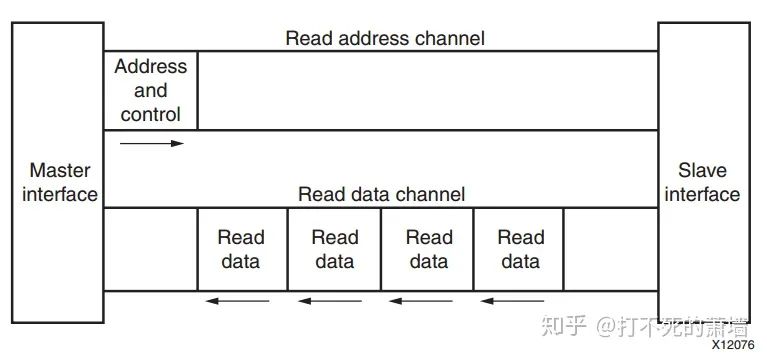

两个读通道

:读地址通道(read address channel)、读数据通道(read data channel);

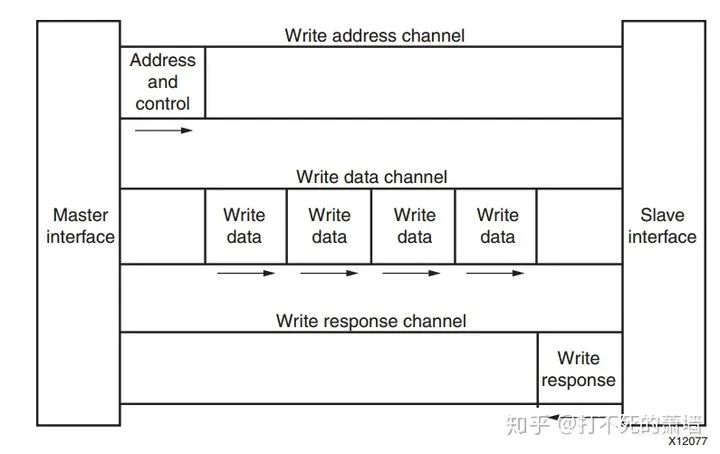

三个写通道

:写地址通道(write address channel)、写数据通道(write data channel)、写响应通道(write response channel);

AXI4读通道操作 图片源自参考[1]

AXI4 写通道操作 图片源自参考[1]

读通道和写通道是分开的,因此可以完成数据的双向传输。此外AXI4能够实现burst传输,换句说就是,可以在一个地址后传输多个数据,最多可以达256 字节。AXI4-Lite不支持burst传输。

AXI4-Stream 只有一个通道,不需要地址,可以burst 传输无限的数据。

常见的辅助IP

AXI Interconnect IP 和AXI SmartConnect IP :

上文提到AXI4 和 AXI4-Lite采用了memory-mapped 的方式,无论是1个master和1个slave、1个master和N个slave、N个master和1个slave、N个master和M个slave,采用这两个ip能帮助我们完成映射。

AXI FIFOs :

缓存数据,或者跨时钟域时有用。

AXI Direct Memory Access (DMA) engines

当我们有一个AXI4-stream接口的IP想与AXI4接口的IP相连时,可以通过AXI DMA完成转换。

ZYNQ上的AXI接口

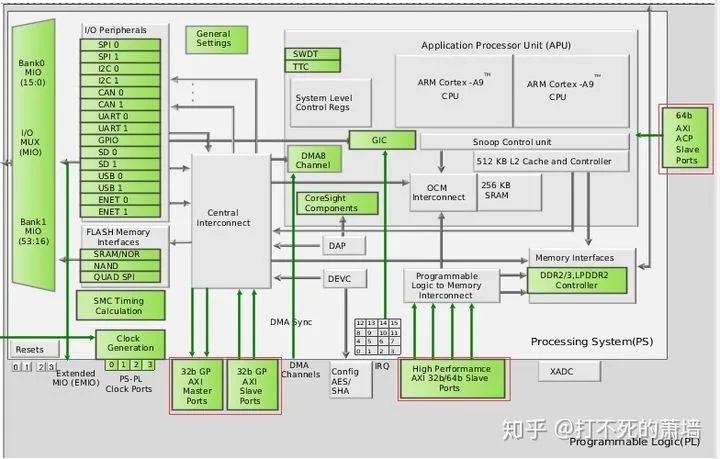

图片源自 zynq 7 processing system ip

zynq的ps上共留了9个AXI接口,其中两个GP AXI master、两个GP AXI slave、四个HP AXI slave、以及一个ACP AXI slave。

这些接口都是AXI3类型的,但使用AXI4-Lite、AXI4 的IP仍然可以与这些接口通讯,因为在实际使用中,软件会使用AXI Interconnect ip帮助我们完成接口的转换。

主要参考

[1] ug1037-vivado-axi-reference-guide

[2] ug585-Zynq-7000-TRM

AXI4-Stream在AXI4家族中相对来说比较简单,接下来主要回答两个问题:

(1)AXI4-Stream 传输的数据流都包含什么?

(2)AXI4-Stream 的接口信号有哪些?master和slave是如何握手的?

数据流

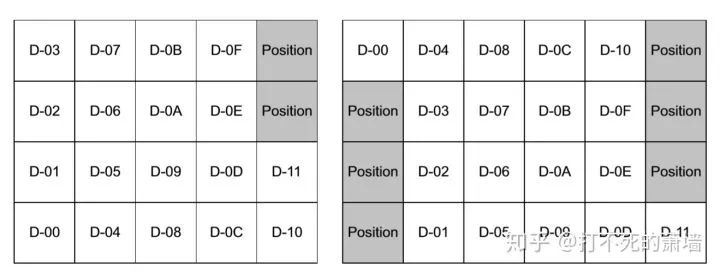

AXI4-Stream传输的数据流包含三种类型:data type、position type、null type。

data type是最有意义的数据;position type 作为占位符使用,可以用来表征date type 的相对位置,null type不包含任何有用的信息。

数据流的结构可以有很多种,例如:可以只传数据,也即都是data type,不包含position type和null type;也可以将data type 和 null type 混着传输;还可以将position type 和 data type混着传输。当然,三者混着传输也没有问题。

全都是data type

data type 和 position type 混搭

那么问题来了,数据流传输类型有三种,在传输的过程中如何分辨这三种类型呢?AXI4-Stream的接口信号可以帮助我们进行区分,接下来看看都有哪些接口信号。

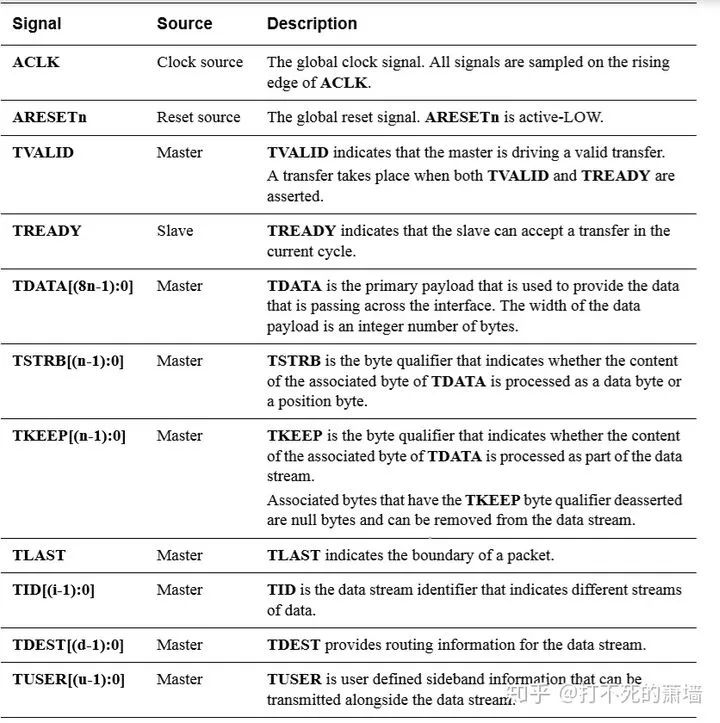

接口信号

先来一图尽览:

ACLK和ARESETn信号,不必多说,时钟和复位信号;

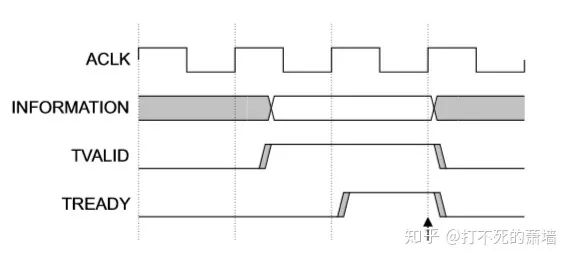

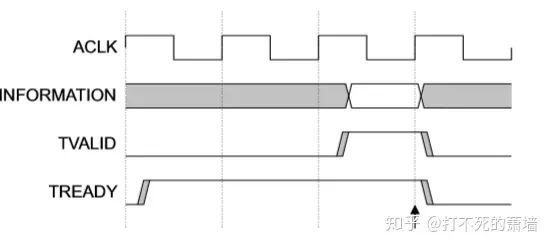

接下来是TVALID和TREADY信号,这两个信号作为握手信号,分别从master 和 slave发出。如何握手呢?想想一下,你和别人握手的过程,大概分为三个阶段:双方心里进行某种心理活动、伸手、握手上下抖动;AXI4-Stream上握手也大体经历这三个过程。

(1)双方心里进行某种心理活动:相当于 master 和 slave 在自己内部搞事情,搞完自己的事情才能闲下来去握手,master搞完事情发出 TVALID high 信号,slave 搞完事情发出TREADY high 信号。

(2)伸手的过程其实比较讲究,现实生活中也是。你和别人握手,可能对方先伸手、也可能你先伸手、也可能你俩同时伸手。master和slave也是如此,可能 TVALID high 信号比TREADY high 早,可能TVALID比TREADY晚,也可能同时出现。

(3)握手上下抖动:当你们两个都抬起了手,接下来就是隆重的握手阶段,在握手的时候,你可以感受到对方的手那么有力量……master和slave在TVALID 和 TREADY同为高时开始传输数据。

TVALID 先高为敬

TREADY 先高为敬

TVALID TREADY 同时变高

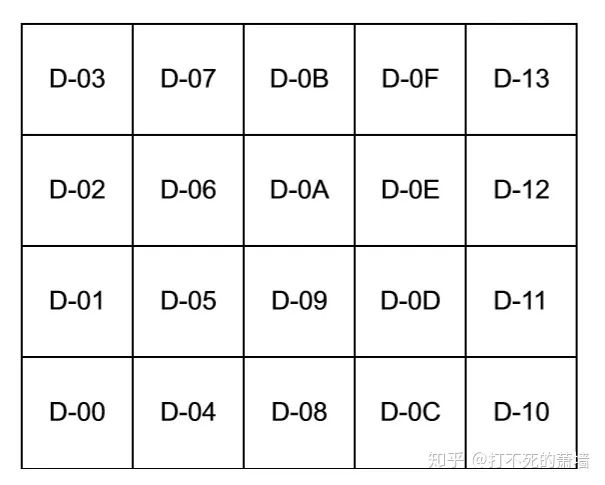

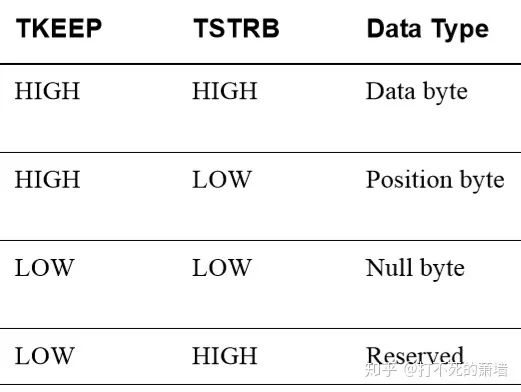

TDATA不多说了,它就是数据流。前文中提到在数据流中有三种类型,分别为data type、position type和null type,那么在传输的时候如何区分呢?要靠TKEEP和TSTRB。

为了便于说明,假设n为数据总线的字节数,即TDATA的字节数,可以把TDATA表示为TDATA[(8*n-1):0],TKEEP和TSTRB有n位,和TDATA上的每个字节一一对应,二者共同表示TDATA上每个字节的类型。举个例子,n = 2、TDATA = 0x0036、TKEEP = 2’b01、 TSTRB= 2’b01。由于TKEEP和TSTRB高位为0,那么TDATA的高阶字节为null type;由于TKEEP和TSTRB地位为1,那么TDATA的低阶字节为data type。

有一点需要注意,TKEEP为0、TSTRB为1的情况是不能使用的。

TKEEP 和 TSTRB 表示数据流中字节类型

TLAST信号,用来表示一个包的结尾。例如发送大小为32字节的包,在发送第32个字节的时候,可以把TLAST信号拉高,来表示这个包发送完了。

TID和TDEST信号:当我们在同一个接口传输不同数据流时有用,一般来讲,AXIS4-Stream Interconnect Core IP可以帮助我们完成这个过程。TUSER信号用来传输一些额外的信息。

参考

[1] ug1037-vivado-axi-reference-guide.pdf

[2] IHI0051A_amba4_axi4_stream_v1_0_protocol_spec.pdf

本文转自:https://zhuanlan.zhihu.com/p/149721810